## High Performance Synchronous Buck EVM Using the TPS5210

# User's Guide

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

#### **Preface**

### **Read This First**

#### About This Manual

This User's Guide describes how to connect and evaluate a synchronous buck regulator using a TI TPS5210 Programmable Synchronous Buck Regulator Controller.

The User's Guide describes the TPS5210EVM-119 Buck Converter Evaluation Module (SLVP119) that provides a convenient method for evaluating the performance of a synchronous buck converter using the TPS5210 Ripple Regulator Controller designed to meet or exceed the Intel VRM8.3 DC-DC converter electrical specifications. A complete designed and tested power supply is presented. Test results can be found in *Designing Fast* Response Synchronous Buck Regulators Using the TPS5210 Application Report, Literature Number SLVA044

| How to Use This Mani  | ıal                                                                                                                  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| Т                     | his document contains the following chapters:                                                                        |

|                       | Chapter 1 Introduction                                                                                               |

|                       | Chapter 2 Schematic                                                                                                  |

|                       | Chapter 3 Physical Layouts                                                                                           |

|                       | Chapter 4 Bills of Material                                                                                          |

| Related Documentation | on From Texas Instruments                                                                                            |

|                       | Designing Fast Response Synchronous Buck Regulators Using the TPS5210 Application Report, Literature Number SLVA044. |

|                       | TPS5210 PROGRAMMABLE SYNCHRONOUS-BUCK REGULATOR CONTROLLER Data Sheet, Literature Number SLVS171                     |

| Related Documentation | on From Intel                                                                                                        |

|                       | VRM 8.3 DC-DC Converter Design Guidelines Intel document Order<br>number: 243870–001, June 1998.                     |

#### **FCC Warning**

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **Trademarks**

TI is a trademark of Texas Instruments Incorporated.

### **Contents**

| 1                 | Introduction1-11.1 Background1-21.2 Performance Specification Summary1-31.3 Voltage Identification Codes1-4 |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| 2                 | Schematic2-12.1Schematic Diagram2-2                                                                         |

| 3                 | Physical Layouts3-13.1 Board Layout3-23.2 Input/Output Connections3-3                                       |

| 4                 | Bill of Materials 4-1                                                                                       |

| =                 | Figures                                                                                                     |

| 2-1<br>3-1<br>3-2 | SLVP119 Board Layout                                                                                        |

| _                 | Tables                                                                                                      |

| 1-1<br>1-2<br>4-1 | 2 Voltage Identification Codes                                                                              |

### Introduction

This user's guide describes the TPS5210EVM-119 Synchronous Buck Converter Evaluation Module (SLVP119). The SLVP119 provides a convenient method for evaluating the performance of a synchronous buck converter using the TPS5210 Ripple Regulator Controller. The TPS5210 meets or exceeds the Intel VRM8.3 dc-dc converter electrical specifications. A complete designed and tested power supply is presented. The power supply is a programmable step-down dc-dc EVM that can deliver up to 20 A of continuous output current at a programmable output voltage from 1.3 V to 3.5 V determined by a 5 bit DAC code. The PWB board layout provides test points for viewing waveforms.

| Topi | c Page                               |

|------|--------------------------------------|

| 1.1  | Background1–2                        |

| 1.2  | Performance Specification Summary1-3 |

| 1.3  | Voltage Identification Codes1-4      |

|      |                                      |

#### 1.1 Background

New high performance microprocessors may require from 40 to 80 watts of power for the CPU alone. Load current must be supplied with up to 30 A/ $\mu$ s slew rate while keeping the output voltage within tight regulation and response time tolerances. Parasitic interconnect impedances between the power supply and the processor must be kept to a minimum. Fast responding synchronous buck dc/dc converters controlled by the Texas Instruments TPS5210 hysteretic controller are ideally suited for microprocessor power applications requiring fast response and precise regulation to rapidly changing loads.

Conventional synchronous regulator control techniques include fixed frequency voltage-mode, fixed frequency current-mode, variable frequency current-mode, variable on-time, or variable off-time. CPU power supplies that are designed using these types of control methods require additional bulk storage capacitors on the output to maintain  $V_O$  within the regulation limits during the high di/dt load transients because of the limited bandwidth of the controller. Some controllers add a fast loop around the slower main control loop to improve the response time, but  $V_O$  must deviate outside a fixed tolerance band before the fast loop becomes active. The hysteretic control method employed by the TPS5210 offers superior performance with no requirements for additional output capacitance or difficult loop compensation design.

The TPS5210 controller was optimized for tight  $V_O$  regulation under static and dynamic load conditions for improved system efficiency. The TP5520 can operate in systems that derive main power from 12 V or 5 V.

1-2 Introduction

#### 1.2 Performance Specification Summary

This section summarizes the performance specifications of the SLVP119 converter. Table 1–1 gives the performance specifications of the converters.

Table 1–1. Performance Specification Summary

| SPECIFI                 | CATION                       | TEST CONDITIONS   | MIN  | TYP    | MAX   | UNITS |

|-------------------------|------------------------------|-------------------|------|--------|-------|-------|

|                         | Main power (V <sub>I</sub> ) |                   | 4.5  |        | 13    | V     |

| Input voltage range     | 5-V input                    |                   | 4.5  | 5      | 5.5   | V     |

|                         | 12-V input                   |                   | 11.4 | 12     | 13    | V     |

| Output voltage range    |                              | See Note 1        | 1.3  | 2      | 3.5   | V     |

| Static voltage tolerand | ce                           | See Note 2        | 1.98 | 2      | 2.02  | V     |

| Line regulation         |                              | See Notes 1 and 3 |      | ±0.05% | ±0.1% |       |

| Load regulation         |                              | See Notes 4 and 5 |      | ±0.1%  | ±0.4% |       |

|                         |                              | 0 11 1 0          |      | ±55    |       | mV pk |

| Transient response      |                              | See Note 6        |      | 50     |       | μsec  |

| Output current range    |                              | See Note 3        | 0    |        | 20    | Α     |

| Current limit           |                              | See Note 3        | 20   |        |       | Α     |

| Output ripple           |                              | See Notes 3 and 5 |      | 35     |       | mV    |

| Soft-start risetime     |                              | See Note 4        |      | 10     |       | ms    |

| Operating frequency     |                              | See Notes 1 and 4 |      | 125    |       | kHz   |

| Efficiency, 10 A load   |                              | See Notes 2 and 4 |      | 90%    |       |       |

| Efficiency, 4 A load    |                              | See Notes 2 and 4 |      | 86%    |       |       |

- **Notes:** 1)  $I_0 = 12 \text{ A}$ .

- 2) VID inputs set for V<sub>REF</sub> = 2 V.

- 3) Input voltage can be at any point over entire range.

- 4) Input voltage adjusted to 12 Vdc.

- 5) IO can be at any point over entire range.

- 6) I<sub>O</sub> pulsed from 0 A to 16 A,  $di/dt = 30 A/\mu s$ .

#### 1.3 Voltage Identification Codes

The output voltage is programmed by driving the 5 VID inputs. The output voltage for a given VID input is shown in Table 1–2.

Table 1–2. Voltage Identification Codes

| VID Terminals<br>(0 = GND, 1 = floating or pull-up to 5 V) |      |      |      |      | VREF   |

|------------------------------------------------------------|------|------|------|------|--------|

| VID4                                                       | VID3 | VID2 | VID1 | VID0 | (Vdc)  |

| 0                                                          | 1    | 1    | 1    | 1    | 1.30   |

| 0                                                          | 1    | 1    | 1    | 0    | 1.35   |

| 0                                                          | 1    | 1    | 0    | 1    | 1.40   |

| 0                                                          | 1    | 1    | 0    | 0    | 1.45   |

| 0                                                          | 1    | 0    | 1    | 1    | 1.50   |

| 0                                                          | 1    | 0    | 1    | 0    | 1.55   |

| 0                                                          | 1    | 0    | 0    | 1    | 1.60   |

| 0                                                          | 1    | 0    | 0    | 0    | 1.65   |

| 0                                                          | 0    | 1    | 1    | 1    | 1.70   |

| 0                                                          | 0    | 1    | 1    | 0    | 1.75   |

| 0                                                          | 0    | 1    | 0    | 1    | 1.80   |

| 0                                                          | 0    | 1    | 0    | 0    | 1.85   |

| 0                                                          | 0    | 0    | 1    | 1    | 1.90   |

| 0                                                          | 0    | 0    | 1    | 0    | 1.95   |

| 0                                                          | 0    | 0    | 0    | 1    | 2.00   |

| 0                                                          | 0    | 0    | 0    | 0    | 2.05   |

| 1                                                          | 1    | 1    | 1    | 1    | No CPU |

| 1                                                          | 1    | 1    | 1    | 0    | 2.10   |

| 1                                                          | 1    | 1    | 0    | 1    | 2.20   |

| 1                                                          | 1    | 1    | 0    | 0    | 2.30   |

| 1                                                          | 1    | 0    | 1    | 1    | 2.40   |

| 1                                                          | 1    | 0    | 1    | 0    | 2.50   |

| 1                                                          | 1    | 0    | 0    | 1    | 2.60   |

| 1                                                          | 1    | 0    | 0    | 0    | 2.70   |

| 1                                                          | 0    | 1    | 1    | 1    | 2.80   |

| 1                                                          | 0    | 1    | 1    | 0    | 2.90   |

| 1                                                          | 0    | 1    | 0    | 1    | 3.00   |

| 1                                                          | 0    | 1    | 0    | 0    | 3.10   |

| 1                                                          | 0    | 0    | 1    | 1    | 3.20   |

| 1                                                          | 0    | 0    | 1    | 0    | 3.30   |

| 1                                                          | 0    | 0    | 0    | 1    | 3.40   |

| 1                                                          | 0    | 0    | 0    | 0    | 3.50   |

1-4 Introduction

### **Schematic**

This chapter contains the schematic diagram for the SLVP119 EVM.

| Topic |                   | Pag | е |

|-------|-------------------|-----|---|

| 2.1   | Schematic Diagram | 2-  | 2 |

#### 2.1 Schematic Diagram

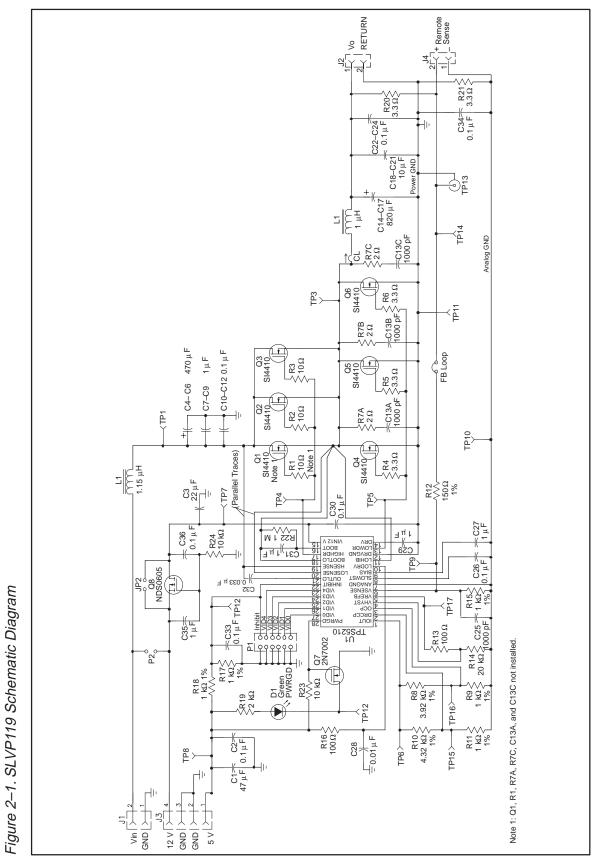

Figure 2–1 shows the SLVP119 EVM schematic diagram.

2-2 Schematic

# **Physical Layouts**

This chapter contains the board layout and I/O connection drawings for the SLVP119 EVM.

| Topi | ic P                     | age |

|------|--------------------------|-----|

| 3.1  | Board Layout             | 3–2 |

| 3.2  | Input/Output Connections | 3–3 |

#### 3.1 Board Layout

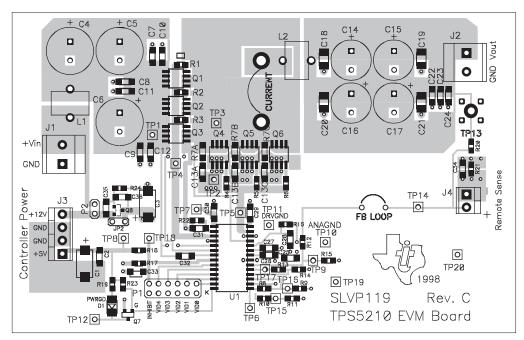

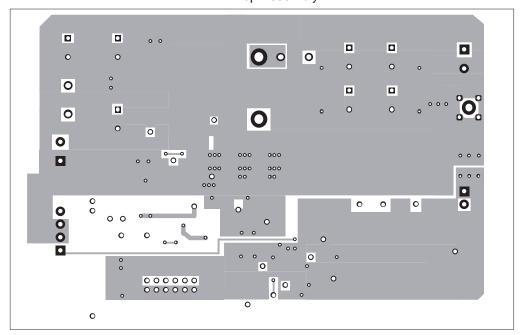

The power supply module consists of one PWB. The board layout includes many test points so that waveforms may be viewed during operation. Figure 3–1 shows the front view and back view of the SLVP119 EVM board.

Figure 3–1. SLVP119 Board Layout

Top Assembly

Bottom Layer (Top View)

3-2 Physical Layouts

#### 3.2 Input/Output Connections

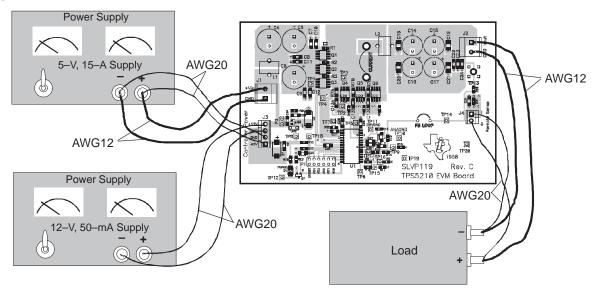

Figure 3–2 shows the input/output connections to the SLVP119.

Figure 3-2. SLVP119 Input/Output Connections

Note: All wire pairs should be twisted.

3-4 Physical Layouts

### **Bill of Materials**

This chapter contains the bill of materials required for the SLVP119EVM.

| Topic | C                 | Page |

|-------|-------------------|------|

| 4.1   | Bill of Materials | 4–2  |

#### 4.1 Bill of Materials

Table 4–1 lists materials required for the SLVP119 EVM.

Table 4-1. SLVP119 Bill of Materials

| REF DES           | PART NUMBER        | DESCRIPTION                                            | MFG       |

|-------------------|--------------------|--------------------------------------------------------|-----------|

| C1                | ECS-H1AD476R       | Capacitor, Tantalum, 47 μF, 10 V, 20%                  | Panasonic |

| C2                | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F},$ 50 V, 10%, X7R  | muRata    |

| C3                | ECS-H1CD226R       | Capacitor, Tantalum, 22 $\mu\text{F}$ , 16 V, 20%      | Panasonic |

| C4                | 16SA470M           | Capacitor, Os–Con, 470 $\mu$ F, 16 V, 20%              | Sanyo     |

| C5                | 16SA470M           | Capacitor, Os-Con, 470 μF, 16 V, 20%                   | Sanyo     |

| C6                | 16SA470M           | Capacitor, Os–Con, 470 $\mu$ F, 16 V, 20%              | Sanyo     |

| C7                | GRM42-6Y5V105Z025A | Capacitor, Ceramic, 1 $\mu$ F, 25 V, 80%–20%, Y5V      | muRata    |

| C8                | GRM42-6Y5V105Z025A | Capacitor, Ceramic, 1 $\mu$ F, 25 V, 80%–20%, Y5V      | muRata    |

| C9                | GRM42-6Y5V105Z025A | Capacitor, Ceramic, 1 $\mu$ F, 25 V, 80%–20%, Y5V      | muRata    |

| C10               | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F}$ , 50 V, 10%, X7R | muRata    |

| C11               | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F}$ , 50 V, 10%, X7R | muRata    |

| C12               | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F},$ 50 V, 10%, X7R  | muRata    |

| C13A <sup>†</sup> | GRM42-6X7R102K050A | Capacitor, Ceramic, 1000 pF, 50 V, 10%, X7R            | muRata    |

| C13B              | GRM42-6X7R102K050A | Capacitor, Ceramic, 1000 pF, 50 V, 10%, X7R            | muRata    |

| C13C <sup>†</sup> | GRM42-6X7R102K050A | Capacitor, Ceramic, 1000 pF, 50 V, 10%, X7R            | muRata    |

| C14               | 4SP820M            | Capacitor, OS–Con, 820 $\mu\text{F}$ , 4 V, 20%        | Sanyo     |

| C15               | 4SP820M            | Capacitor, OS–Con, 820 $\mu\text{F}$ , 4 V, 20%        | Sanyo     |

| C16               | 4SP820M            | Capacitor, OS–Con, 820 $\mu\text{F}$ , 4 V, 20%        | Sanyo     |

| C17               | 4SP820M            | Capacitor, OS–Con, 820 $\mu\text{F}$ , 4 V, 20%        | Sanyo     |

| C18               | GRM235Y5V106Z016A  | Capacitor, Ceramic, 10 $\mu\text{F}$ , 16 V, Y5V       | TDK       |

| C19               | GRM235Y5V106Z016A  | Capacitor, Ceramic, 10 $\mu\text{F}$ , 16 V, Y5V       | TDK       |

| C20               | GRM235Y5V106Z016A  | Capacitor, Ceramic, 10 $\mu\text{F}$ , 16 V, Y5V       | TDK       |

| C21               | GRM235Y5V106Z016A  | Capacitor, Ceramic, 10 $\mu\text{F}$ , 16 V, Y5V       | TDK       |

| C22               | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F},$ 50 V, 10%, X7R  | muRata    |

| C23               | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F},$ 50 V, 10%, X7R  | muRata    |

| C24               | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F}$ , 50 V, 10%, X7R | muRata    |

| C25               | GRM42-6X7R102K050A | Capacitor, Ceramic, 1000 pF, 50 V, 10%, X7R            | muRata    |

| C26               | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F}$ , 50 V, 10%, X7R | muRata    |

<sup>†</sup>C13A and C13C not installed.

4-2 Bill of Materials

Table 4–1. SLVP119 Bill of Materials (Continued)

| REF DES         | PART NUMBER        | DESCRIPTION                                                  | MFG         |

|-----------------|--------------------|--------------------------------------------------------------|-------------|

| C27             | GRM42-6Y5V105Z025A | Capacitor, Ceramic, 1 μF, 25 V, 80%–20%, Y5V                 | muRata      |

| C28             | GRM42-6X7R103K050A | Capacitor, Ceramic, 0.01 $\mu\text{F}$ , 50 V, 10%, X7R      | muRata      |

| C29             | GRM42-6Y5V105Z025A | Capacitor, Ceramic, 1 $\mu$ F, 25 V, 80%–20%, Y5V            | muRata      |

| C30             | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F}$ , 50 V, 10%, X7R       | muRata      |

| C31             | GRM42-6Y5V105Z025A | Capacitor, Ceramic, 1 $\mu$ F, 25 V, 80%–20%, Y5V            | muRata      |

| C32             | GRM42-6X7R333Z050A | Capacitor, Ceramic, 0.033 $\mu\text{F}$ , 50 V, 10%, X7R     | muRata      |

| C33             | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F}$ , 50 V, 10%, X7R       | muRata      |

| C34             | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 $\mu\text{F}$ , 50 V, 10%, X7R       | muRata      |

| C35             | GRM42-6Y5V105Z025A | Capacitor, Ceramic, 1 $\mu$ F, 25 V, 80%, –20%, Y5V          | muRata      |

| C36             | GRM42-6X7R104K050A | Capacitor, Ceramic, 0.1 μF, 50 V, 10%, X7R                   | muRata      |

| D1              | SML-LX2832GC-TR    | Diode. LED, Green, 2.1 V, SM                                 | Lumex       |

| J2              | MKDS3/2-5.08       | Terminal Block, 2-Pin, 32A, 5.08 mm                          | Phoenix     |

| J3              | ED1516-ND          | Terminal Block, 4-Pin, 6A, 3.5 mm                            | OST         |

| J4              | ED1514-ND          | Terminal Block, 2-Pin, 6A, 3.5 mm                            | OST         |

| L1              |                    | Inductor, Filter, 1.15 μH, 11 A<br>(8T #18 on T44–8/90 Core) | MicroMetals |

| L2              |                    | Inductor, Filter, 1 μH, 25 A<br>(7T #16 on T68–8/90 Core)    | MicroMetals |

| P1              | 929836-09-36-ND    | Header, Straight, 2x6, 0.1" (72-Pin cut down)                | 3M          |

| P2              | A19350-ND          | Header, Straight, 1x2, 0.1" center                           | AMP         |

| Q1 <sup>†</sup> | Si4410DY           | FET, N–ch, 30–V, 10–A, 13-m $\Omega$                         | Siliconix   |

| Q2              | Si4410DY           | FET, N–ch, 30–V, 10–A, 13-m $\Omega$                         | Siliconix   |

| Q3              | Si4410DY           | FET, N–ch, 30–V, 10–A, 13-m $\Omega$                         | Siliconix   |

| Q4              | Si4410DY           | FET, N–ch, 30–V, 10–A, 13-m $\Omega$                         | Siliconix   |

| Q5              | Si4410DY           | FET, N–ch, 30–V, 10–A, 13-m $\Omega$                         | Siliconix   |

| Q6              | Si4410DY           | FET, N–ch, 30–V, 10–A, 13-m $\Omega$                         | Siliconix   |

| Q7              | SN7002             | FET, N–ch, 60–V, 115 mA, 1.2- $\Omega$                       | Diodes Inc. |

| Q8              | NDS0605            | FET, N–ch, 60–V, 180 mA, 5- $\Omega$                         | Fairchild   |

| R1 <sup>†</sup> | Std                | Resistor, Chip, Zero Ohm, 1/10 W, 5%                         |             |

| R2              | Std                | Resistor, Chip, Zero Ohm, 1/10 W, 5%                         |             |

| R3              | Std                | Resistor, Chip, Zero Ohm, 1/10 W, 5%                         |             |

TR1, Q1 not installed.

Table 4–1. SLVP119 Bill of Materials (Continued)

| REF DES             | PART NUMBER  | DESCRIPTION                                  | MFG       |

|---------------------|--------------|----------------------------------------------|-----------|

| J1                  | MKDS3/2-5.08 | Terminal Block, 2-Pin, 32A, 5.08 mm          | Phoenix   |

| R4                  | Std          | Resistor, Chip, 3.3 $\Omega$ , 1/10 W, 5%    |           |

| R5                  | Std          | Resistor, Chip, 3.3 $\Omega$ , 1/10 W, 5%    |           |

| R6                  | Std          | Resistor, Chip, 3.3 $\Omega$ , 1/10 W, 5%    |           |

| R7A <sup>†</sup>    | Std          | Resistor, Chip, 2.7 $\Omega$ , 1/8 W, 5%     |           |

| R7B                 | Std          | Resistor, Chip, 2.7 $\Omega$ , 1/8 W, 5%     |           |

| R7C <sup>†</sup>    | Std          | Resistor, Chip, 2.7 $\Omega$ , 1/8 W, 5%     |           |

| R8                  | Std          | Resistor, Chip, 3.92 k $\Omega$ , 1/10 W, 1% |           |

| R9                  | Std          | Resistor, Chip, 1 k $\Omega$ , 1/10 W, 1%    |           |

| R10                 | Std          | Resistor, Chip, 4.32 k $\Omega$ , 1/10 W, 1% |           |

| R11                 | Std          | Resistor, Chip, 1 k $\Omega$ , 1/10 W, 1%    |           |

| R12                 | Std          | Resistor, Chip, 150 $\Omega$ , 1/10 W, 1%    |           |

| R13                 | Std          | Resistor, Chip, 100 $\Omega$ , 1/10 W, 1%    |           |

| R14                 | Std          | Resistor, Chip, 20 k $\Omega$ , 1/10 W, 1%   |           |

| R15                 | Std          | Resistor, Chip, 10 k $\Omega$ , 1/10 W, 1%   |           |

| R16                 | Std          | Resistor, Chip, 100 $\Omega$ , 1/10 W, 5%    |           |

| R17                 | Std          | Resistor, Chip, 1 k $\Omega$ , 1/10 W, 1%    |           |

| R18                 | Std          | Resistor, Chip, 1 k $\Omega$ , 1/10 W, 1%    |           |

| R19                 | Std          | Resistor, Chip, 2 k $\Omega$ , 1/10 W, 5%    |           |

| R20                 | Std          | Resistor, Chip, 3.3 $\Omega$ , 1/10 W, 5%    |           |

| R21                 | Std          | Resistor, Chip, 3.3 $\Omega$ , 1/10 W, 5%    |           |

| R22                 | Std          | Resistor, Chip, 1 M $\Omega$ , 1/10 W, 5%    |           |

| R23                 | Std          | Resistor, Chip, 10 k $\Omega$ , 1/10 W, 5%   |           |

| R24                 | Std          | Resistor, Chip, 10 k $\Omega$ , 1/10 W, 5%   |           |

| TP1-9,<br>12, 14-18 | 240–345      | Test Point, Red                              | Farnell   |

| TP10,11,<br>19,20   | 240–333      | Test Point, Black                            | Farnell   |

| TP13                | 131–4244–00  | Adaptor, 3.5-mm probe clip ( or 131-5031-00) | Tektronix |

TR7A, R7C not installed.

4-4 Bill of Materials

Table 4–1. SLVP119 Bill of Materials (Continued)

| REF DES           | PART NUMBER  | DESCRIPTION                                  | MFG    |

|-------------------|--------------|----------------------------------------------|--------|

| U1                | TPS5210DW    | IC, PWM Ripple Controller, Adjustable Output | TI     |

| Current<br>Jumper | 9912         | Wire, PVC, Stranded, 12AWG, 600 V, 1055C     | Belden |

| FB Loop           | 8021         | Wire, Bare, Solid, 22AWG                     | Belden |

| NA                | 929950-00-ND | Shunt, Jumper, 0.1" (for P1)                 | ЗМ     |

| NA                | SLVP119      | PCB, TPS5210 EVM Board                       |        |