#### features

- Up to 100-mA Output Current

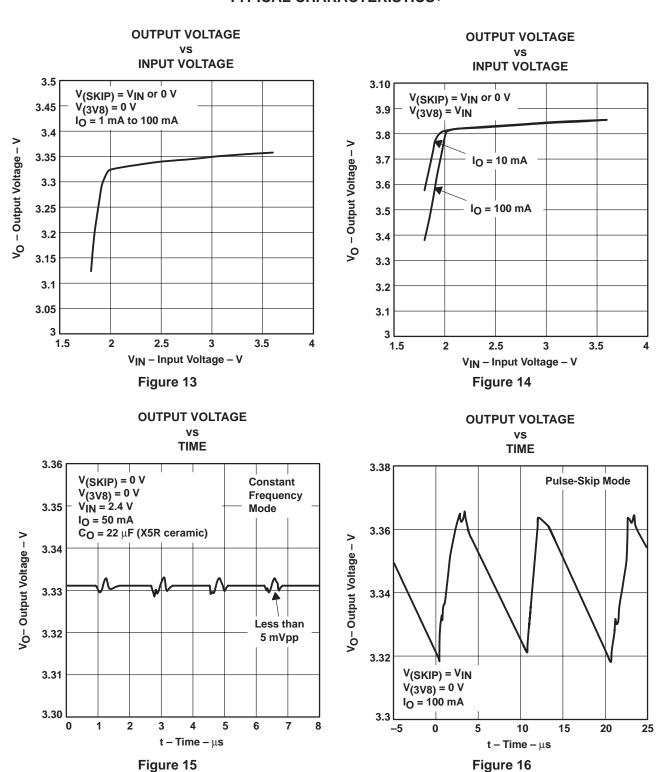

- Less Than 5-mV<sub>pp</sub> Output Voltage Ripple

- No Inductors Required/Low EMI

- Regulated 3.3-V ±4% Output

- Only Four External Components Required

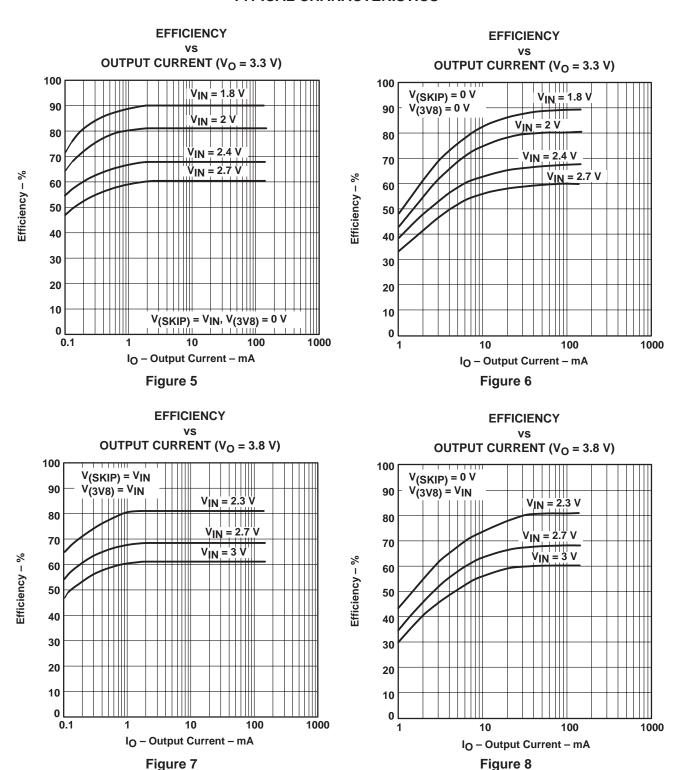

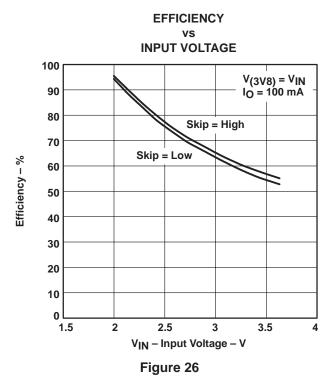

- Up to 90% Efficiency

- 1.8-V to 3.6-V Input Voltage Range

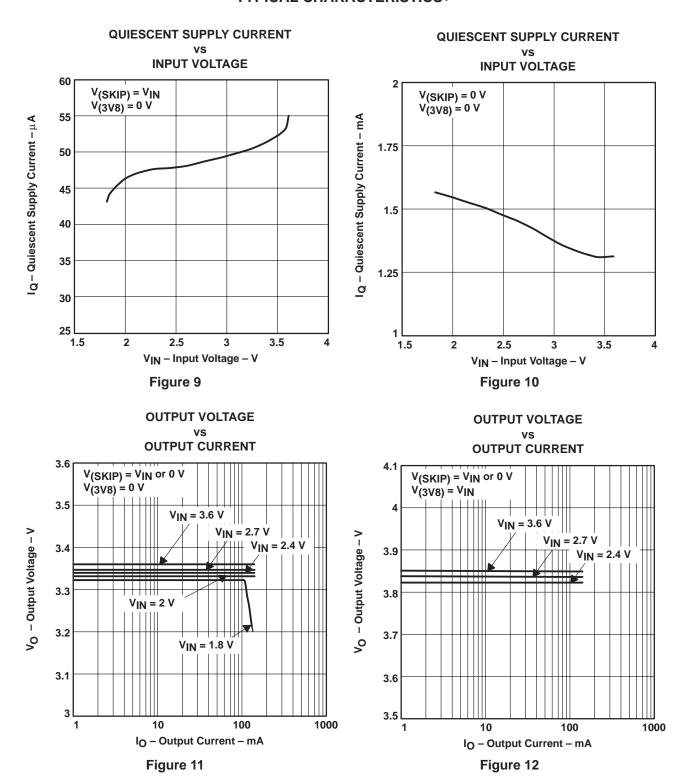

- 50-μA Quiescent Supply Current

- 0.05-μA Shutdown Current

- Load Isolated in Shutdown

- Space-Saving Thermally-Enhanced TSSOP PowerPAD™ Package

- Evaluation Module Available (TPS60100EVM-131)

# description

The TPS60101 step-up, regulated charge pump generates a 3.3-V  $\pm 4\%$  output voltage from a 1.8-V to 3.6-V input voltage (two alkaline, NiCd, or NiMH batteries). Output current is 100 mA from a 2-V input. Only four external capacitors are needed to build a complete low-noise dc/dc converter. The push-pull operating mode of two single-ended charge pumps assures the low output voltage ripple as current is continuously transferred to the output. From a 2-V input, the TPS60101 can start into full load with loads as low as 33  $\Omega$ .

The TPS60101 features either constant frequency mode to minimize noise and output voltage ripple or the power-saving pulse-skip mode to extend battery life at light loads. The TPS60101 switching frequency is 300 kHz. The logic shutdown function reduces the supply current to 1- $\mu$ A (max) and disconnects the load from the input. Special current-control circuitry prevents excessive current from being drawn from the battery during start-up. This DC/DC converter requires no inductors and has low EMI. It is available in the small 20-pin TSSOP PowerPAD<sup>TM</sup> package (PWP).

## applications

### Replaces DC/DC Converters With Inductors in

- Battery-Powered Applications

- Two Battery Cells to 3.3-V Conversion

- Portable Instruments

- Battery-Powered Microprocessor and DSP Systems

- Miniature Equipment

- Backup-Battery Boost Converters

- PDAs

- Laptops

- Handheld Instrumentation

- Medical Instruments

- Cordless Phones

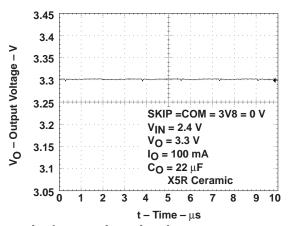

#### output voltage ripple

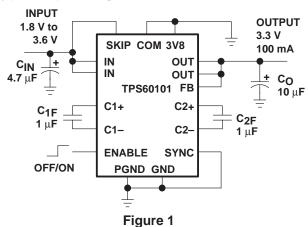

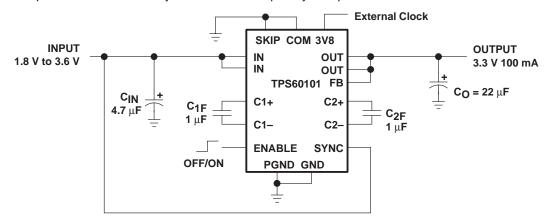

# typical operating circuit

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **AVAILABLE OPTIONS**

| 7.07.02.22.20.110.10        |  |  |  |  |  |

|-----------------------------|--|--|--|--|--|

| PACKAGE                     |  |  |  |  |  |

| TSSOP <sup>†</sup><br>(PWP) |  |  |  |  |  |

| TPS60101PWP                 |  |  |  |  |  |

<sup>†</sup> This package is available taped and reeled. To order this packaging option, add an R suffix to the part number (e.g., TPS60101PWPR).

### **Terminal Functions**

| TERMI  | TERMINAL |     | DECORPORTION                                                                                                                                                                                                                                                   |

|--------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                    |

| 3V8    | 19       | I   | Mode selection. When 3V8 is logic low the charge pump operates in the regulated 3.3-V mode. When 3V8 is connected to IN the regulator operates in preregulated 3.8-V mode.                                                                                     |

| C1+    | 6        |     | Positive terminal of the charge-pump capacitor C <sub>1</sub> F                                                                                                                                                                                                |

| C1-    | 8        |     | Negative terminal of the charge-pump capacitor C <sub>1F</sub>                                                                                                                                                                                                 |

| C2+    | 15       |     | Positive terminal of the charge-pump capacitor C <sub>2</sub> F                                                                                                                                                                                                |

| C2-    | 13       |     | Negative terminal of the charge-pump capacitor C <sub>2</sub> F                                                                                                                                                                                                |

| СОМ    | 18       | I   | Mode selection.  When COM is logic low the charge pump operates in push-pull mode to minimize output ripple. When COM is connected to IN the regulator operates in single-ended mode requiring only one flying capacitor.                                      |

| ENABLE | 3        | ı   | ENABLE Input. The device turns off, the output disconnects from the input, and the supply current decreases to 0.05 μA when ENABLE is a logic low. Connect ENABLE to IN for normal operation.                                                                  |

| FB     | 4        | I   | FEEDBACK input. Connect FB to OUT as close to the load as possible to achieve best regulation. Resistive divider is on chip to match internal reference voltage of 1.22 V.                                                                                     |

| GND    | 1, 20    |     | GROUND. Analog ground for internal reference and control circuitry. Connect to PGND through a short trace.                                                                                                                                                     |

| IN     | 7, 14    | ı   | Supply Input. Connect to an input supply in the 1.8-V to 3.6-V range. Bypass IN to GND with a $(C_O/2)$ $\mu$ F capacitor. Connect both INs through a short trace.                                                                                             |

| OUT    | 5, 16    | 0   | Regulated power output. Connect both OUTs through a short trace and bypass OUT to GND with the output filter capacitor $C_0$ . $V_0 = 3.3$ V when $3V_8 = 10$ low and $V_0 = 3.8$ V when $3V_8 = 10$ light.                                                    |

| PGND   | 9–12     |     | PGND power ground. Charge-pump current flows through this pin. Connect all PGNDs together.                                                                                                                                                                     |

| SKIP   | 17       | I   | Mode selection. When SKIP is logic low, the charge pump operates in constant-frequency mode. Output ripple and noise are minimized in this mode. When SKIP is connect to IN, the device operates in pulse skip mode. Quiescent current is lowest in this mode. |

| SYNC   | 2        | I   | Selection for external clock signal. Connect to GND to use the internally generated clock signal. Connect to IN for external synchronization. In this case, the clock signal needs to be fed through 3V8 and the device operates in the regulated 3.3-V mode.  |

# absolute maximum ratings (unless otherwise noted)†‡

| Input voltage range, V <sub>I</sub> (IN, OUT, ENABLE, SKIP, COM, 3V8, FB, SY | NC)0.3 V to 5.5 V                   |

|------------------------------------------------------------------------------|-------------------------------------|

| Differential input voltage, V <sub>ID</sub> (C1+, C2+ to GND)                | 0.3 V to (V <sub>OUT</sub> + 0.3 V) |

| Differential input voltage, V <sub>ID</sub> (C1–, C2– to GND)                | 0.3 V to (V <sub>IN</sub> + 0.3 V)  |

| Continuous total power dissipation                                           | See Dissipation Rating Tables       |

| Continuous output current                                                    | 150 mA                              |

| Storage temperature range, T <sub>stq</sub>                                  | –55°C to 150°C                      |

| Lead temperature 1,6 mm (1/16 inch) from case for 10s                        | 260°C                               |

| Maximum junction temperature, T <sub>.1</sub>                                | 150°C                               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

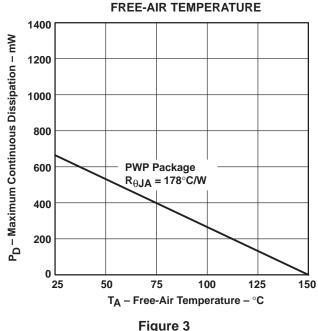

#### DISSIPATION RATING TABLE 1 - FREE-AIR TEMPERATURE (see Figure 3)

| PACKAGE | $\begin{aligned} & \textbf{T}_{\pmb{A}} \leq \textbf{25}^{\circ}\textbf{C} \\ & \textbf{POWER RATING} \end{aligned}$ | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| PWP     | 700 mW                                                                                                               | 5.6 mW/°C                                      | 448 mW                                | 364 mW                                |

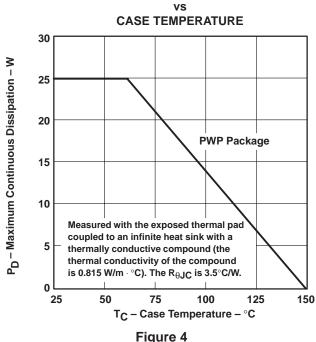

#### DISSIPATION RATING TABLE 2 - CASE TEMPERATURE (see Figure 4)

| PACKAGE | $T_C \le 62.5^{\circ}C$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>C</sub> = 62.5°C | T <sub>C</sub> = 70°C<br>POWER RATING | T <sub>C</sub> = 85°C<br>POWER RATING |

|---------|--------------------------------------|--------------------------------------------------|---------------------------------------|---------------------------------------|

| PWP     | 25 W                                 | 285.7 mW/°C                                      | 22.9 W                                | 18.5 W                                |

#### **DISSIPATION DERATING CURVE§**

# MAXIMUM CONTINUOUS DISSIPATION§

\$ Dissipation rating tables and figures are provided for maintenance of junction temperature at or below absolute maximum temperature of 150°C. It is recommended not to exceed a junction temperature of 125°C.

VENABLE, VSKIP, VCOM, V3V8 and VSYNC can exceed VIN up to the maximum rated voltage without increasing the leakage current drawn by these mode select inputs.

# TPS60101 REGULATED 3.3-V 100-mA LOW-NOISE CHARGE PUMP DC/DC CONVERTER

SLVS214A – JUNE 1999 – REVISED SEPTEMBER 1999

# electrical characteristics at C<sub>IN</sub> = 10 $\mu$ F, C<sub>1F</sub> = C<sub>2F</sub> = 2.2 $\mu$ F†, C<sub>O</sub> = 22 $\mu$ F, T<sub>C</sub> = -40°C to 85°C, V<sub>IN</sub>=2V, V<sub>FB</sub>=V<sub>O</sub>, V<sub>ENABLE</sub>=V<sub>IN</sub>, V<sub>SKIP</sub>=V<sub>IN</sub> or 0 V and V<sub>COM</sub>=V<sub>3V8</sub>=V<sub>SYNC</sub>=0 V (unless otherwise noted)

| PARAMETER             |                                                        | TEST CO                                                              | NDITIONS                                         | MIN                      | TYP   | MAX                      | UNIT |

|-----------------------|--------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------|--------------------------|-------|--------------------------|------|

| VIN                   | Input voltage                                          |                                                                      |                                                  | 1.8                      |       | 3.6                      | V    |

| V <sub>IN(UV)</sub>   | Input undervoltage lockout threshold                   |                                                                      |                                                  |                          | 1.6   | 1.8                      | V    |

| I <sub>O(MAX)</sub>   | Maximum output current                                 |                                                                      |                                                  | 100                      |       |                          | mA   |

|                       |                                                        | 1.8 V < V <sub>IN</sub> < 2 V,<br>V <sub>O</sub> (Start-Up) = 3.3 V, |                                                  | 3.17                     | 3.3   | 3.43                     |      |

| Vo                    | Output voltage                                         | 2 V < V <sub>IN</sub> < 3.3 V,                                       | 0 < I <sub>O</sub> < 100 mA                      | 3.17                     | 3.3   | 3.43                     | V    |

|                       |                                                        | 3.3 V < V <sub>IN</sub> < 3.6 V,                                     | 0 < I <sub>O</sub> < 100 mA                      | 3.17                     | 3.3   | 3.47                     |      |

| VO(RIP)               | Output voltage ripple                                  | I <sub>O</sub> = 100 mA,                                             | VSKIP = 0 V                                      |                          | 5‡    |                          | mVpp |

| lO(LEAK)              | Output leakage current                                 | $V_{IN} = 2.4 V,$                                                    | VENABLE = 0 V                                    |                          |       | 1                        | μΑ   |

| la.                   | Quiescent current                                      | V <sub>SKIP</sub> = V <sub>IN</sub> = 2.4 V                          |                                                  |                          | 50    | 90                       | μΑ   |

| IQ                    | (no-load input current)                                | V <sub>SKIP</sub> = 0 V,                                             | $V_{IN} = 2.4 V$                                 |                          | 1.5   |                          | mA   |

| I <sub>DD(SDN)</sub>  | Shutdown supply current                                | V <sub>IN</sub> = 2.4 V,                                             | VENABLE = 0 V                                    |                          | 0.05  | 1                        | μΑ   |

| fOSC(int)             | Internal switching frequency                           | V <sub>IN</sub> = 2.4 V                                              |                                                  | 200                      | 300   | 400                      | kHz  |

| fOSC(ext)             | External clock frequency                               | VSYNC = VIN,                                                         | V <sub>IN</sub> = 1.8V to 3.6 V                  | 400                      | 600   | 800                      | kHz  |

|                       | External clock duty cycle                              | VSYNC = VIN,                                                         | V <sub>IN</sub> = 1.8V to 3.6 V                  | 20%                      |       | 80%                      |      |

|                       | Efficiency                                             | I <sub>O</sub> = 50 mA                                               |                                                  |                          | 80%   |                          |      |

| V <sub>INL</sub>      | Input voltage low,<br>ENABLE, SKIP, COM, 3V8, SYNC     | V <sub>IN</sub> = 1.8 V                                              |                                                  |                          |       | 0.3 ×<br>V <sub>IN</sub> | V    |

| VINH                  | Input voltage high,<br>ENABLE, SKIP, COM, 3V8, SYNC    | V <sub>IN</sub> = 3.6 V                                              |                                                  | 0.7 ×<br>V <sub>IN</sub> |       |                          | V    |

| I <sub>I</sub> (LEAK) | Input leakage current,<br>ENABLE, SKIP, COM, 3V8, SYNC | VENABLE = VSKIP = V                                                  |                                                  |                          | 0.01  | 0.1                      | μА   |

|                       | Output load regulation                                 | V <sub>O</sub> = 3.3 V,<br>T <sub>C</sub> = 25°C                     | 1 mA < I <sub>O</sub> < 100 mA                   |                          | 0.004 |                          | %/mA |

|                       | Output line regulation                                 | 2 V < V <sub>IN</sub> < 3.3 V,<br>I <sub>O</sub> = 50 mA,            | V <sub>O</sub> = 3.3 V,<br>T <sub>C</sub> = 25°C |                          | 0.6   |                          | %/V  |

|                       | Short circuit current                                  | V <sub>IN</sub> = 2.4 V<br>T <sub>C</sub> = 25°C                     | V <sub>O</sub> = 0 V,                            |                          | 125   |                          | mA   |

<sup>†</sup> Use only ceramic capacitors with X5R or X7R dielectric as flying capacitors.

$<sup>\</sup>ddagger$  Achieved with C<sub>O</sub> = 22  $\mu$ F X5R dielectric ceramic capacitor

electrical characteristics for preregulated 3.8-V Mode (V<sub>(3V8)</sub> = V<sub>IN</sub>), at C<sub>IN</sub> = 10  $\mu\text{F},$  C<sub>1F</sub> = C<sub>2F</sub> = 2.2  $\mu\text{F}^{\dagger},$  C<sub>O</sub> = 22  $\mu\text{F},$  T<sub>C</sub> = -40°C to 85°C, V<sub>IN</sub> = 2.4 V, V<sub>FB</sub> = V<sub>O</sub>, V<sub>ENABLE</sub> = V<sub>IN</sub>, V<sub>SKIP</sub> = V<sub>IN</sub> or 0 V and V<sub>COM</sub> = V<sub>SYNC</sub> = 0 V (unless otherwise noted)

|                     | PARAMETER                    | TEST CONDITIO                                       | NS       | MIN | TYP  | MAX | UNIT |

|---------------------|------------------------------|-----------------------------------------------------|----------|-----|------|-----|------|

| V <sub>IN</sub>     | Input voltage                |                                                     |          | 2.2 |      | 3.6 | V    |

| I <sub>O(MAX)</sub> | Maximum output current       |                                                     |          | 100 |      |     | mA   |

| Vo                  | Output voltage               | 2.2 V < V <sub>IN</sub> < 3.6 V, 0 < I <sub>O</sub> | < 100 mA | 3.6 | 3.8  | 4   | V    |

| IO(LEAK)            | Output leakage current       | VENABLE = 0 V                                       |          |     |      | 1   | μΑ   |

| la                  | Quiescent current            | VSKIP = VIN                                         |          |     | 60   |     | μΑ   |

| <sup>I</sup> Q      | (no-load input current)      | V <sub>SKIP</sub> = 0 V                             |          |     | 2    |     | mA   |

| IDD(SDN)            | Shutdown supply current      | VENABLE = 0 V                                       |          |     | 0.05 | 1   | μΑ   |

| fosc                | Internal switching frequency |                                                     |          | 200 | 300  | 400 | kHz  |

|                     | Short circuit current        | $V_O = 0 V$ , $T_C = 2$                             | 25°C     |     | 125  |     | mA   |

<sup>&</sup>lt;sup>†</sup> Use only ceramic capacitors with X5R or X7R dielectric as flying capacitors.

# TYPICAL CHARACTERISTICS†

## detailed description

# operating principle

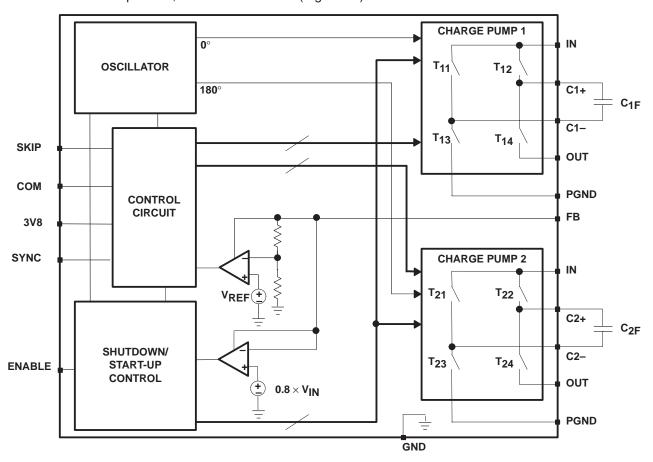

The TPS60101 charge pump provides a regulated 3.3-V output from a 1.8-V to 3.6-V input. It delivers a maximum load current of 100 mA. Designed specifically for space critical battery powered applications, the complete charge pump circuit requires only four external capacitors. The circuit can be optimized for highest efficiency at light loads or lowest output noise. The TPS60101 consists of an oscillator, a 1.22-V bandgap reference, an internal resistive feedback circuit, an error amplifier, high current MOSFET switches, a shutdown/start-up circuit, and a control circuit (Figure 29)

Figure 29. Functional Block Diagram TPS60101

The oscillator runs at a 50% duty cycle. The device consists of two single-ended charge pumps which operate with 180° phase shift. Each single ended charge pump transfers charge into its transfer capacitor ( $C_{XF}$ ) in one half of the period. During the other half of the period (transfer phase),  $C_{XF}$  is placed in series with the input to transfer its charge to  $C_O$ . While one single-ended charge pump is in the charge phase, the other one is in the transfer phase. This operation guarantees an almost constant output current which ensures a low output ripple.

If the clock were to run continuously, this process would eventually generate an output voltage equal to two times the input voltage (hence the name doubler). In order to provide a regulated fixed output voltage of 3.3 V, the TPS60101 uses either pulse-skip mode or constant-frequency mode. Pulse-skip mode and constant-frequency mode are externally selected via the SKIP input pin.

# detailed description (continued)

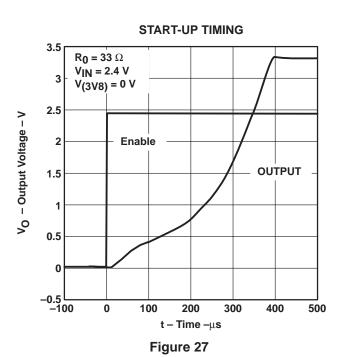

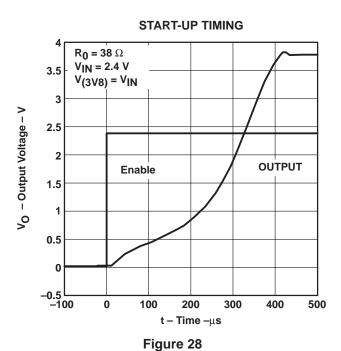

#### start-up procedure

During start-up, i.e. when ENABLE is set from logic low to logic high, the switches T12 and T14 (charge pump 1), and the switches T22 and T24 (charge pump 2) are conducting to charge up the output capacitor until the output voltage  $V_O$  reaches  $0.8\times V_{IN}$ . When the start-up comparator detects this limit, the IC begins to operate in the mode selected with SKIP, COM and 3V8. This start-up charging of the output capacitor guarantees a short start-up time and eliminates the need for a Schottky diode between IN and OUT.

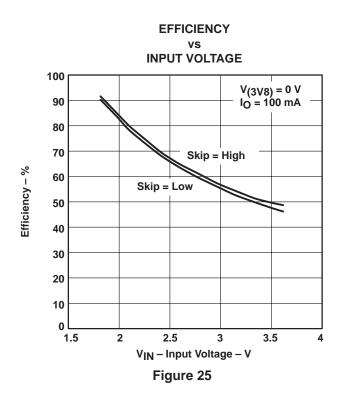

# pulse-skip mode

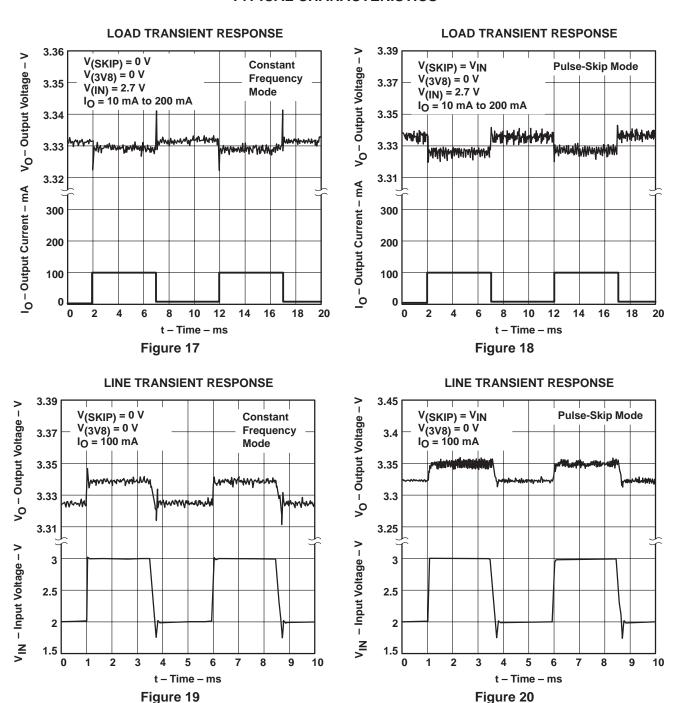

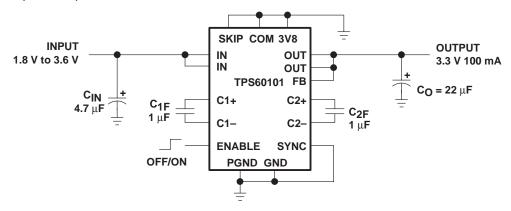

In pulse-skip mode (SKIP = high), the error amplifier disables switching of the power stages when it detects an output higher than 3.3 V. The oscillator halts. The IC then skips switching cycles until the output voltage drops below 3.3 V. Then the error amplifier reactivates the oscillator and switching of the power stages starts again. The pulse-skip regulation mode minimizes operating current because it does not switch continuously and deactivates all functions except bandgap reference and error amplifier when the output is higher than 3.3 V. When switching is disabled from the error amplifier, the load is also isolated from the input. SKIP is a logic input and should not remain floating. The typical operating circuit of the TPS60101 in pulse skip mode is shown in Figure 1.

#### constant-frequency mode

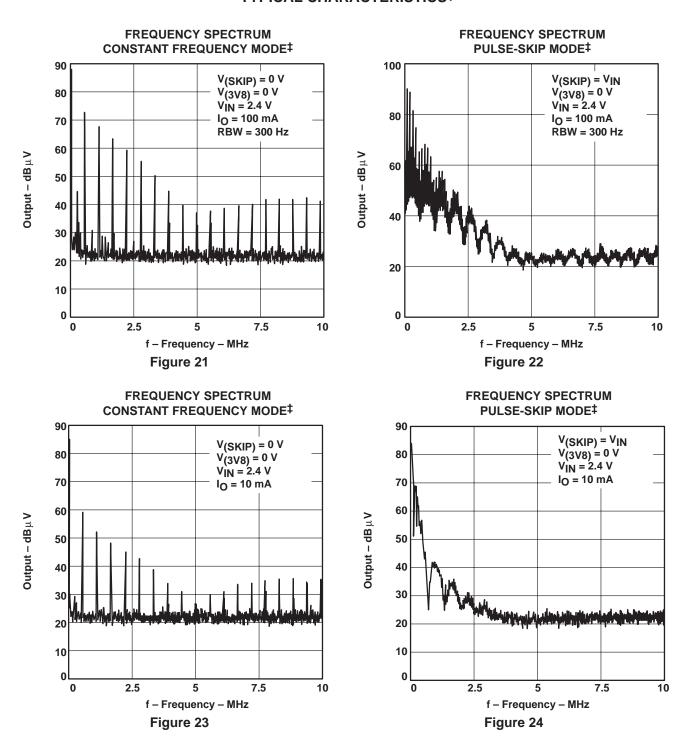

When SKIP is low, the charge pump runs continuously at the frequency  $f_{OSC}$ . The control circuit, fed from the error amplifier, controls the charge on  $C_{1F}$  and  $C_{2F}$  by driving the gates of the FETs  $T_{12}/T_{13}$  and  $T_{22}/T_{23}$ , respectively. When the output voltage falls, the gate drive increases, resulting in a larger voltage across  $C_{1F}$  and  $C_{2F}$ . This regulation scheme minimizes output ripple. Since the device switches continuously, the output noise contains well-defined frequency components, and the circuit requires smaller external capacitors for a given output ripple. However, constant-frequency mode, due to higher operating current, is less efficient at light loads than pulse-skip mode.

Figure 30. Typical Operating Circuit TPS60101 in Constant Frequency Mode

**Table 1. Tradeoffs Between Operating Modes**

| FEATURE                                                    | PULSE-SKIP MODE<br>(SKIP = High) | CONSTANT-FREQUENCY MODE (SKIP = Low) |

|------------------------------------------------------------|----------------------------------|--------------------------------------|

| Best light-load efficiency                                 | X                                |                                      |

| Smallest external component size for a given output ripple |                                  | X                                    |

| Output ripple amplitude                                    | Small amplitude                  | Very small amplitude                 |

| Output ripple frequency                                    | Variable                         | Constant                             |

| Load regulation                                            | Very good                        | Good                                 |

NOTE: Even in pulse-skip mode the output ripple amplitude is small if the push-pull operating mode is selected via COM.

# detailed description (continued)

#### push-pull operating mode

In push-pull operating mode (COM = low), the two single-ended charge pumps operate with 180° phase shift. The oscillator signal has a 50% duty cycle. Each single-ended charge pump transfers charge into its transfer capacitor ( $C_{XF}$ ) in one-half of the period. During the other half of the period (transfer phase),  $C_{XF}$  is placed in series with the input to transfer its charge to  $C_O$ . While one single-ended charge pump is in the charge phase, the other one is in the transfer phase. This operation guarantees an almost constant output current which ensures a low output ripple. COM is a logic input and should not remain floating. The typical operating circuit of the TPS60101 in push-pull mode is shown in Figure 1 and Figure 30.

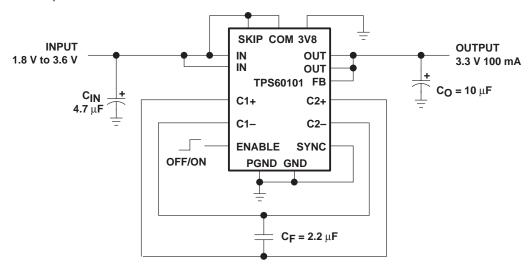

# single-ended operating mode

When COM is high, the device runs in single-ended operating mode. The two single-ended charge pumps operate in parallel without phase shift. They transfer charge into the transfer capacitor  $(C_F)$  in one half of the period. During the other half of the period (transfer phase),  $C_F$  is placed in series with the input to transfer its charge to  $C_O$ . In single-ended operating mode only one transfer capacitor  $(C_F = C_{1F} + C_{2F})$  is required, resulting in less board space.

Figure 31. Typical Operating Circuit TPS60101 in Single-Ended Operating Mode

**Table 2. Tradeoffs Between Operating Modes**

| FEATURE                 | PUSH-PULL MODE<br>(COM = Low) | SINGLE-ENDED MODE<br>(COM = High) |

|-------------------------|-------------------------------|-----------------------------------|

| Output ripple amplitude | Small amplitude               | Large amplitude                   |

| Smallest board space    |                               | X                                 |

#### regulated 3.3 V operating mode

In regulated 3.3-V operating mode (3V8 = low) the device provides a regulated 3.3-V output from a1.8-V to 3.6-V input. 3V8 is a logic input and should not remain floating. The typical operating circuit of the TPS60101 in (3.3 V) regulated mode is shown in Figure 1 and Figure 30.

# pre-regulated 3.8 V operating mode

When 3V8 is high, the device provides a preregulated 3.8-V output from a 2.2-V to 3.6-V input. This mode should be used if a tighter output voltage tolerance is a major concern. In this case the charge pump generates the input voltage for a low-dropout regulator.

# detailed description (continued)

#### shutdown

Driving ENABLE low places the device in shutdown mode. This disables all switches, the oscillator, and control logic. The device typically draws 0.05- $\mu$ A (1- $\mu$ A max) of supply current in this mode. Leakage current drawn from the output is as low as 1  $\mu$ A max. The device exits shutdown once ENABLE is set high level. The typical no-load shutdown exit time is 10  $\mu$ s. When the device is in shutdown, the load is isolated from the input and the output is high impedance.

#### external clock signal

If the device operates at a user defined frequency, an external clock signal can be used. Therefore, SYNC needs to be connected to IN and the external oscillator signal can drive 3V8. The maximum external frequency is limited to 800 kHz. The switching frequency of the converter is half of the external oscillator frequency. It is recommended to operate the charge pump in constant-frequency mode if an external clock signal is used so that the output noise contains only well-defined frequency components.

Figure 32. Typical Operating Circuit TPS60101 With External Synchronization

#### undervoltage lockout

The TPS60101 has an undervoltage lockout feature that deactivates the device and places it in shutdown mode when the input voltage falls below 1.6 V.

#### **APPLICATION INFORMATION**

# capacitor selection

The TPS60101 requires only four external capacitors as shown in the basic application circuit. Their values are closely linked to the output current capacity, output noise requirements, and mode of operation. Generally, the transfer capacitors ( $C_{xF}$ ) will be the smallest.

The input capacitor improves system efficiency by reducing the input impedance and stabilizes the input current.  $C_{IN}$  is recommended to be about two to four times as large as  $C_{xF}$ .

The output capacitor  $(C_O)$  can be selected from 5-times to 50-times larger than  $C_{\chi F}$ , depending on the mode of operation and ripple tolerance<sup>†</sup>. Tables 3 and 4 show capacitor values recommended for low quiescent-current operation (pulse-skip mode) and for low output voltage ripple operation (constant-frequency mode). A recommendation is given for smallest size.

Table 3. Recommended Capacitor Values for Low Quiescent-Current Operation† (pulse-skip mode)

| V <sub>IN</sub><br>[V] | IO [mA] | C <sub>IN</sub><br>[μF] |           | C <sub>xF</sub><br>[μ <b>F</b> ] |          | ο<br>ι <b>F</b> ] | OUTPUT<br>VOLTAGE<br>RIPPLE V <sub>PP</sub> |

|------------------------|---------|-------------------------|-----------|----------------------------------|----------|-------------------|---------------------------------------------|

| [ [V]                  |         | TANTALUM                | CERAMIC   | μΕ                               | TANTALUM | CERAMIC           | [mV]                                        |

| 2.4                    | 50      | 4.7                     |           | 1                                | 10       |                   | 135                                         |

| 2.4                    | 50      |                         | 4.7 (X7R) | 1                                |          | 10 (X5R)          | 125                                         |

| 2.4                    | 100     | 4.7                     |           | 1                                | 10       |                   | 70                                          |

| 2.4                    | 100     |                         | 4.7 (X7R) | 1                                |          | 10 (X5R)          | 65                                          |

<sup>†</sup> All measurements are done with additional 1-μF X7R ceramic capacitors at input and output.

Table 4. Recommended Capacitor Values for Low Output Voltage Ripple Operation<sup>†</sup> (constant-frequency mode)

| V <sub>IN</sub><br>[V] | I <sub>O</sub><br>[mA] | <b>C</b> <sub>IN</sub><br>[μF] |           | C <sub>χF</sub><br>[μF] |          | o<br>ıF] | OUTPUT<br>VOLTAGE<br>RIPPLE V <sub>PP</sub> |

|------------------------|------------------------|--------------------------------|-----------|-------------------------|----------|----------|---------------------------------------------|

| [4]                    | اداسما                 | TANTALUM                       | CERAMIC   | [μι]                    | TANTALUM | CERAMIC  | [mV]                                        |

| 2.4                    | 50                     | 4.7                            |           | 1                       | 22       |          | 5                                           |

| 2.4                    | 50                     |                                | 4.7 (X7R) | 1                       |          | 22 (X5R) | 3                                           |

| 2.4                    | 100                    | 4.7                            |           | 1                       | 22       |          | 10                                          |

| 2.4                    | 100                    |                                | 4.7 (X7R) | 1                       |          | 22 (X5R) | 5                                           |

<sup>†</sup>All measurements are done with additional 1-μF X7R ceramic capacitors at input and output.

<sup>†</sup> In constant-frequency mode always select  $C_O \ge 22 \mu F$

#### **APPLICATION INFORMATION**

For the TPS60101, the smallest board space size can be achieved using Sprague's 595D-series tantalum capacitors for input and output. However, with the trend towards high capacitance ceramic capacitors in smaller size packages, these type of capacitors might become competitive in size soon.

**MANUFACTURER PART NUMBER CAPACITANCE TYPE** Taiyo Yuden LMK212BJ105KG-T  $1 \mu F$ Ceramic  $2.2\,\mu F$ LMK212BJ225MG-T Ceramic  $4.7 \mu F$ Ceramic LMK316BJ475KL-T  $10 \mu F$ Ceramic JMK316BJ106ML-T LMK432BJ226MM-T  $22\,\mu F$ Ceramic AVX 0805ZC105KAT2A 1 μF Ceramic 1206ZC225KAT2A  $2.2 \, \mu F$ Ceramic TPSC475035R0600  $4.7 \mu F$ Tantalum TPSC106025R0500  $10 \mu F$ Tantalum TPSC226016R0375  $22 \mu F$ Tantalum 4.7 μF Sprague 595D475X0016A2T **Tantalum** 595D106X0010A2T 10 μF **Tantalum** 22 μF 595D226X06R3A2T **Tantalum**  $22 \mu F$ 595D226X06R3B2T **Tantalum** 595D226X0020C2T 22 μF **Tantalum** Kemet T494B475M010AS 4.7 μF **Tantalum** T494C106M010AS 10 μF Tantalum T494C226M010AS  $22 \mu F$ **Tantalum**

**Table 5. Recommended Capacitors**

Table 6 lists the manufacturers of recommended capacitors. In most applications surface-mount tantalum capacitors will be the right choice. However, ceramic capacitors will provide the lowest output voltage ripple due to their typically lower ESR.

**Table 6. Recommended Capacitor Manufacturers**

| MANUFACTURER | CAPACITOR TYPE                               | INTERNET        |

|--------------|----------------------------------------------|-----------------|

| Taiyo Yuden  | X7R/X5R ceramic                              | www.t-yuden.com |

| AVX          | X7R/X5R ceramic<br>TPS–series tantalum       | www.avxcorp.com |

| Sprague      | 595D–series tantalum<br>593D–series tantalum | www.vishay.com  |

| Kemet        | T494–series tantalum                         | www.kemet.com   |

#### power dissipation

The power dissipated in the TPS60101 depends on output current and is approximated by:

$$P_{DISS} = I_{O} \times (2 V_{IN} - V_{O}) \text{ for } I_{Q} << I_{O}$$

$P_{DISS}$  must be less than that allowed by the package rating. See the ratings for 20-PowerPAD<sup>TM</sup> package power-dissipation limits and deratings.

#### APPLICATION INFORMATION

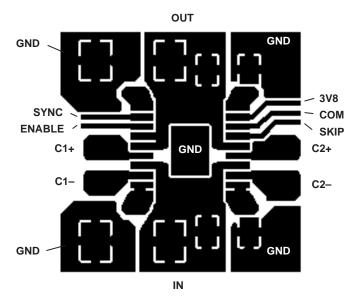

### layout

All capacitors should be soldered in close proximity to the IC. A PCB layout proposal for a two-layer board is given in Figure 33. Care has been taken to connect both single-ended charge pumps symmetrically to the load to achive optimized output voltage ripple performance. The proposed layout also provides improved thermal performance as the exposed leadframe is soldered to the PCB. The bottom layer of the PCB is a ground plain only. All ground areas on the PCB should be connected. Connect ground areas on top layer to the bottom layer via through hole connections.

Figure 33. Recommended PCB Layout for TPS60101 (top view)

The evaluation module designed for the TPS60100 can, with slight modifications, be used for evaluation of the TPS60101. The EVM can be ordered under literature code SLVP131 or under product code TPS60100EVM–131.

#### **APPLICATION INFORMATION**

# applications proposals

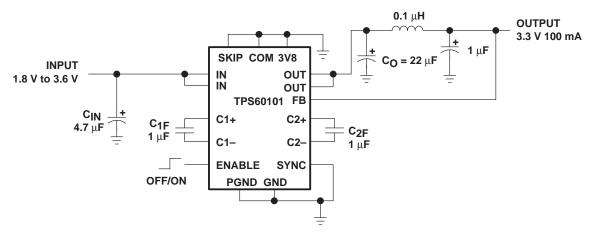

# TPS60101 with LC output filter for ultra low ripple

For applications where extremely low output ripple is required, a small LC filter is recommended. This is shown in Figure 34. The addition of a small inductor and filter capacitor will reduce the output ripple well below what could be achieved with capacitors alone. The corner frequency of 500 kHz was chosen above the 300 kHz switching frequency to avoid loop stability issues in case the feedback is taken from the output of the LC filter. Leaving the feedback (FB) connection point before the LC filter, the filter capacitance value can be increased to achieve even higher ripple attenuation without affecting stability margin.

Figure 34. TPS60101 With LC Filter for Ultra Low Output Ripple Applications

#### related information

#### application reports

For more application information see:

- PowerPAD™ Application Report (Literature Number: SLMA002)

- TPS6010x/TPS6011x Charge Pump Application Report (Literature Number: SLVA070)

#### device family products

Other devices in this family are:

| PART NUMBER | LITERATURE<br>NUMBER | DESCRIPTION                                                   |

|-------------|----------------------|---------------------------------------------------------------|

| TPS60100    | SLVS213              | Regulated 3.3-V, 200-mA Low-Noise Charge Pump DC/DC Converter |

| TPS60110    | SLVS215              | Regulated 5-V, 300-mA Low-Noise Charge Pump DC/DC Converter   |

| TPS60111    | SLVS216              | Regulated 5-V, 150-mA Low-Noise Charge Pump DC/DC Converter   |

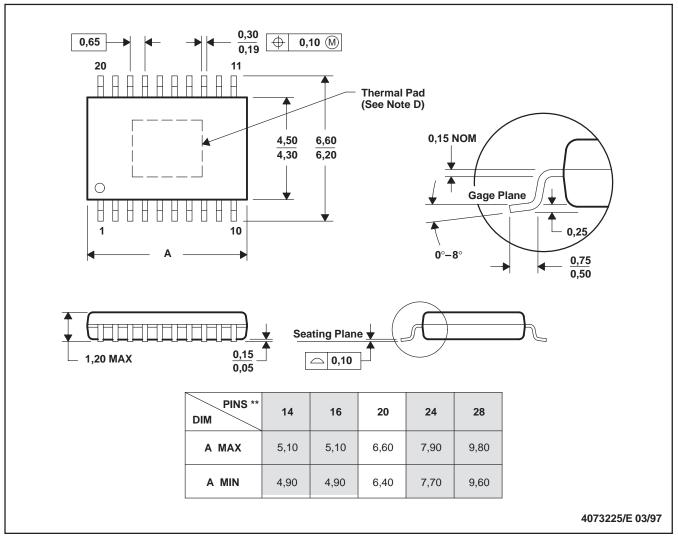

#### **MECHANICAL DATA**

# PWP (R-PDSO-G\*\*)

#### PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

### **20-PIN SHOWN**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions.

- D. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This pad is electrically and thermally connected to the backside of the die and possibly selected leads.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated