CompactFlash CARDS

# 8/16-bit Data Bus CompactFlash Card

# MF0064M-04BAxx MF0128M-04BAxx

**Connector Type**

# Two-piece 50-pin

#### **DESCRIPTION**

Mitsubishi's CompactFlash™ cards provide large memory capacities on a device approximately the size of a match box (36.4mm×42.8mm×3.3mm). The cards use an 8/16 bit data bus. Available in 64MB and 128MB capacities, Mitsubishi's CompactFlash cards conform to the CompactFlash Specification released from CompactFlash Association.

Using with the 68-pin adapter card, Mitsubishi's CompactFlash card operates in PC Card compliant sockets. It conforms to PCMCIA2.1, JEIDA4.2 and PC Card Standard.

When the OE# signal is asserted low level by the Host system in power on cycle, the Mitsubishi's CompactFlash cards can be selected in a True IDE interface. It uses the ATA command set so no software drivers are required.

#### **FEATURES**

- Single 5V or 3.3V Supply

- Card density of up to 128MB maximum

- Four PC Card ATA and True IDE modes

- Nonvolatile, No Batteries Required

- High reliability based on internal ECC function

- Fast read/write performance(Target)

Read: 2.0MB/s(max.)

Write: 900KB/s(max.) (64MB)

1.0MB/s(max.) (128MB)

• 100,000 program/erase cycles

#### **APPLICATIONS**

- Computers

- Digital Camera

- Data Communication

- Office Automation

- Industrial

- Consumer

### **PRODUCT LIST**

|                | Memory capacity (Bytes) | Data Bus<br>width(bits) | Memory            | Cylinder | Head | Sector | Out line |

|----------------|-------------------------|-------------------------|-------------------|----------|------|--------|----------|

| MF0064M-04BAxx | 64,094,208              | 8/16                    | 256Mbit Flash x 2 | 978      | 4    | 32     | Type I   |

| MF0128M-04BAxx | 128,057,344             |                         | 256Mbit Flash x 4 | 977      | 8    | 32     |          |

<sup>\*</sup>CompactFlash is a trademarks of SanDisk Corporation.

#### **PIN ASSIGNMENT**

| FIIN | ASSIGNI  | /I EIN I |         |     |              |        |

|------|----------|----------|---------|-----|--------------|--------|

|      | PC Car   | -        | PC Card | I/O | True IDE Int | erface |

| Pin  | Memory M |          | Mode    |     |              |        |

|      | Signal   | I/O      | Signal  | I/O | Signal       | I/O    |

| 1    | GND      | -        | GND     | -   | GND          | -      |

| 2    | D3       | I/O      | D3      | I/O | D3           | I/O    |

| 3    | D4       | I/O      | D4      | I/O | D4           | I/O    |

| 4    | D5       | I/O      | D5      | I/O | D5           | I/O    |

| 5    | D6       | I/O      | D6      | I/O | D6           | I/O    |

| 6    | D7       | I/O      | D7      | I/O | D7           | I/O    |

| 7    | CE1#     | I        | CE1#    | - 1 | CS0#         | I      |

| 8    | A10      | I        | A10     | ı   | N.U          | -      |

| 9    | OE#      | I        | OE#     | I   | ATA SEL#     | I      |

| 10   | A9       | I        | A9      | - 1 | N.U          | -      |

| 11   | A8       | I        | A8      | I   | N.U          | -      |

| 12   | A7       | I        | A7      | - 1 | N.U          | -      |

| 13   | Vcc      | -        | Vcc     | -   | Vcc          | -      |

| 14   | A6       | I        | A6      | I   | N.U          | -      |

| 15   | A5       | I        | A5      | I   | N.U          | -      |

| 16   | A4       | I        | A4      | I   | N.U          | -      |

| 17   | A3       | I        | A3      | I   | N.U          | -      |

| 18   | A2       | I        | A2      | I   | A2           | I      |

| 19   | A1       | I        | A1      | I   | A1           | I      |

| 20   | A0       | I        | A0      | I   | A0           | I      |

| 21   | D0       | I/O      | D0      | I/O | D0           | I/O    |

| 22   | D1       | I/O      | D1      | I/O | D1           | I/O    |

| 23   | D2       | I/O      | D2      | I/O | D2           | I/O    |

| 24   | WP       | 0        | IOIS16# | 0   | IOCS16#      | 0      |

| 25   | CD2#     | 0        | CD2#    | 0   | CD2#         | 0      |

|     |          |     |           |     |           | _   |

|-----|----------|-----|-----------|-----|-----------|-----|

| 1 1 | PC Ca    |     | PC Card I | /O  | True ID   | _   |

| Pin | Memory N |     | Mode      |     | Interface |     |

|     | Signal   | I/O | Signal    | I/O | Signal    | I/O |

| 26  | CD1#     | 0   | CD1#      | 0   | CD1#      | 0   |

| 27  | D11      | I/O | D11       | I/O | D11       | I/O |

| 28  | D12      | I/O | D12       | I/O | D12       | I/O |

| 29  | D13      | I/O | D13       | I/O | D13       | I/O |

| 30  | D14      | I/O | D14       | I/O | D14       | I/O |

| 31  | D15      | I/O | D15       | I/O | D15       | I/O |

| 32  | CE2#     | I   | CE2#      | ı   | CS1#      | ı   |

| 33  | VS1#     | 0   | VS1#      | 0   | VS1#      | 0   |

| 34  | N.U      | -   | IORD#     | ı   | IORD#     | ı   |

| 35  | N.U      | -   | IOWR#     | I   | IOWR#     | I   |

| 36  | WE#      | I   | WE#       |     | WE#       | ı   |

| 37  | READY    | 0   | IREQ#     | 0   | INTRQ     | 0   |

| 38  | Vcc      | -   | Vcc       | -   | Vcc       | -   |

| 39  | CSEL     | I   | CSEL      | ı   | CSEL      | ı   |

| 40  | VS2#     | 0   | VS2#      | 0   | VS2#      | 0   |

| 41  | RESET    | I   | RESET     |     | RESET#    | ı   |

| 42  | WAIT#    | 0   | WAIT#     | 0   | IORDY     | 0   |

| 43  | N.U      | -   | INPACK#   | 0   | INPACK#   | 0   |

| 44  | REG#     | I   | REG#      | ı   | REG#      | ı   |

| 45  | BVD2     | 0   | SPKR#     | 0   | DASP#     | I/O |

| 46  | BVD1     | 0   | STSCHG#   | 0   | PDIAG#    | I/O |

| 47  | D8       | I/O | D8        | I/O | D8        | I/O |

| 48  | D9       | I/O | D9        | I/O | D9        | I/O |

| 49  | D10      | I/O | D10       | I/O | D10       | I/O |

| 50  | GND      | -   | GND       | -   | GND       | -   |

N.U = Not used.

**Signal Description**

| Signal Description                                                                                                                      |     |                                                                    |                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                                                                                                             | I/O | Pin No.                                                            | Description                                                                                                                                                                                                                                                                                                |

| Address bus[A10-A0]                                                                                                                     | I   | 8, 10, 11, 12,<br>14, 15, 16, 17,<br>18, 19, 20                    | Signals A10-A0 are address bus. A0 is invalid in word mode. A10 is the MSB and A0 is the LSB.                                                                                                                                                                                                              |

| Data bus[D15-D0]                                                                                                                        | I/O | 31, 30, 29, 28,<br>27, 49, 48, 47,<br>6, 5, 4, 3, 2,<br>23, 22, 21 | Signals D15-D0 are data bus. D0 is the LSB of the Even Byte of the Word. D8 is the LSB of the Odd Byte of the Word.                                                                                                                                                                                        |

| Card Enable[CE1#, CE2#] (PC Card Memory Mode)  Card Enable[CE1#, CE2#] (PC Card I/O Mode)  Chip Select[CS0#, CS1#] (True IDE Interface) |     | 7, 32                                                              | In True IDE Interface, CS0# is used to select the Command Block Registers. CS1# is used to select the Control Block Registers.                                                                                                                                                                             |

| Output Enable[OE#] (PC Card Memory Mode) Output Enable[OE#] (PC Card I/O Mode) ATA SEL# (True IDE Interface)                            | I   | 9                                                                  | OE# is used to gate Attribute and Common Memory Read data from the Card. OE# is used to gate Attribute Memory Read data from the Card. To enable True IDE Interface, this input should be grounded by the host.                                                                                            |

| Write Enable[WE#] (PC Card Memory Mode) Write Enable[WE#] (PC Card I/O Mode) Write Enable[WE#] (True IDE Interface)                     | I   | 36                                                                 | WE# is used for strobing Attribute and Common Memory Write data into the Card. WE# is used for strobing Attribute Memory Write data into the Card. This input should be connected Vcc by the host.                                                                                                         |

| I/O Read[IORD#] (PC Card I/O Mode) I/O Read[IORD#] (True IDE Interface)                                                                 | I   | 34                                                                 | IORD# is used to read data from the Card's I/O space.                                                                                                                                                                                                                                                      |

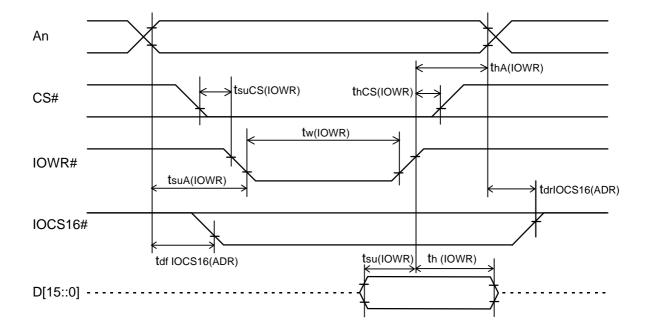

| I/O Write[IOWR#] (PC Card I/O Mode) I/O Write[IOWR#] (True IDE Interface)                                                               | I   | 35                                                                 | IOWR# is used to write data to the Card's I/O space.                                                                                                                                                                                                                                                       |

| Ready[READY] (PC Card Memory Mode) IREQ# (PC Card I/O Mode) INTRQ (True IDE Interface)                                                  | 0   | 37                                                                 | READY signal is set high when the Card is ready to accept a new data transfer operation.  This signal of low level is indicates that the card is requesting software service to host, and high level indicates that the card is not requesting.  This signal is active high interrupt request to the host. |

| Card Detection[CD1#, CD2#]                                                                                                              | 0   | 26, 25                                                             | CD1# and CD2# provided for proper detection of Card insertion.                                                                                                                                                                                                                                             |

| Write Protect[WP] (PC Card Memory Mode)  IOIS16# (PC Card I/O Mode)  IOCS16# (True IDE Interface)                                       | 0   | 24                                                                 | This signal is held low because this card does not have a write protect switch.  This output signal is asserted when the I/O port address is capable of 16-bit access.                                                                                                                                     |

Signal Description(Continued)

| Signal Description(Continued)                                                                                                      |     |         |                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                                                                                                        | I/O | Pin No. | Description                                                                                                                                                                                         |

| Attribute Memory Select[REG#] (PC Card Memory Mode) Attribute Memory Select[REG#] (PC Card I/O Mode) Attribute Memory Select[REG#] | I   | 44      | When this signal is asserted, access is limited to Attribute Memory with OE#/WE# and I/O Space with IORD#/IOWR#.  This input signal is not used for this mode and                                   |

| (True IDE Interface)                                                                                                               |     |         | should be connected to Vcc by the host.                                                                                                                                                             |

| Battery Voltage Detect[BVD2] (PC Card Memory Mode) Audio Digital Waveform[SPKR#]                                                   | 0   | 45      | This output is driven to a high-level.  SPKR# is kept negated because this Card does not                                                                                                            |

| (PC Card I/O Mode)  DASP#                                                                                                          | I/O |         | have digital audio output.  This signal is the DISK Active/Slave Present signal                                                                                                                     |

| (True IDE Interface)                                                                                                               |     |         | in the Master/Slave handshake protocol.                                                                                                                                                             |

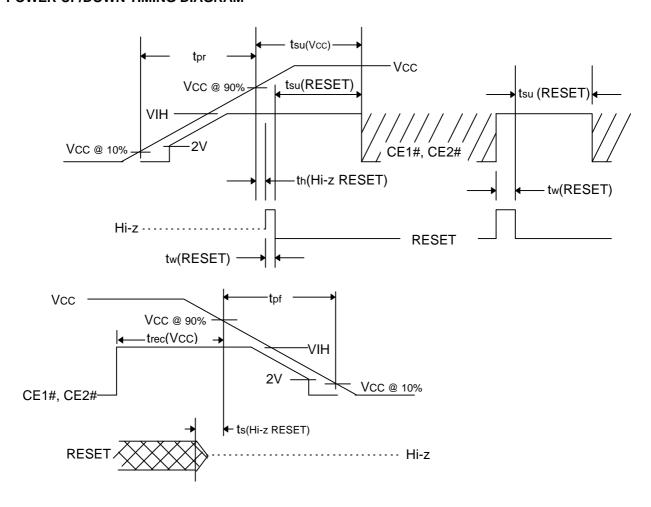

| Card Reset[RESET] (PC Card Memory Mode)  Card Reset[RESET] (PC Card I/O Mode)                                                      | I   | 41      | By assertion of this signal, all registers of this Card are cleared. This signal should be kept to High-Z by the host for at least 1ms after Vcc applied.                                           |

| Card Reset[RESET#] (True IDE Interface)                                                                                            |     |         | This input pin is the active low hardware reset from the host.                                                                                                                                      |

| Wait[WAIT#] (PC card Memory Mode) Wait[WAIT#] (PC card I/O Mode) IORDY (True IDE Interface)                                        | 0   | 42      | This signal is asserted to delay completion of the memory or I/O access cycle.                                                                                                                      |

| Input Port Acknowledge[INPACK#]<br>(PC Card I/O Mode)                                                                              | 0   | 43      | This signal is asserted when the Card is selected and can respond to an I/O Read cycle at the address on the address bus.                                                                           |

| Input Port Acknowledge[INPACK#] (True IDE Interface)                                                                               |     |         | This signal is not used for this mode and should not be connected at the host.                                                                                                                      |

| Battery Voltage Detect[BVD1] (PC Card Memory Mode)                                                                                 | 0   | 46      | This output is driven to a high-level.                                                                                                                                                              |

| STSCHG#<br>(PC Card I/O Mode)                                                                                                      |     |         | This signal is asserted low to alert the host to changes in the status of Configuration Status Register in the Attribute Memory Space.                                                              |

| PDIAG#<br>(True IDE Interface)                                                                                                     | I/O |         | This signal is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                   |

| Voltage Sense[VS1, VS2]                                                                                                            | 0   | 33, 40  | VS1 is grounded so that the Card CIS can be read at 3.3V and VS2 is N.C.                                                                                                                            |

| Cable Select[CSEL] (PC Card Memory Mode)                                                                                           | -   | 39      | This signal is not used for this mode.                                                                                                                                                              |

| Cable Select[CSEL]<br>(PC Card I/O Mode)                                                                                           | -   |         |                                                                                                                                                                                                     |

| Cable Select[CSEL] (True IDE Interface)                                                                                            | I   |         | This signal is used to configure this Card as a Master or a Slave. When this signal is grounded, this Card is configured as a Master. When this signal is Open, this Card is configured as a Slave. |

| Vcc                                                                                                                                | -   | 13, 38  | 5V or 3.3V power.                                                                                                                                                                                   |

| GND                                                                                                                                | -   | 1, 50   | Ground.                                                                                                                                                                                             |

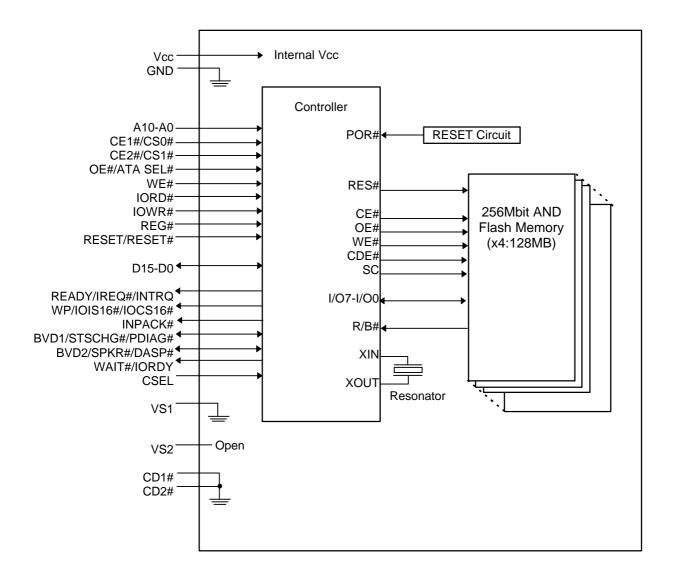

#### **BLOCK DIAGRAM**

#### **MITSUBISHI STORAGE CARD**

# MF0XXXX-04BAXX series CompactFlash CARDS

# **FUNCTION TABLE**

| FUNCTION      |           |             |      |    |     |     |       |       |            |            |

|---------------|-----------|-------------|------|----|-----|-----|-------|-------|------------|------------|

| Function      | REG#      | CE2#        | CE1# | A0 | OE# | WE# | IORD# | IOWR# | D15-D8     | D7-D0      |

| Attribute Mer | mory Rea  | d Functio   | n    |    |     |     |       |       |            |            |

| Standby       | X         | Н           | Н    | Χ  | Χ   | Х   | Х     | Χ     | High-Z     | High-Z     |

| Byte Access   | L         | Н           | L    | L  | L   | Н   | Н     | Н     | High-Z     | Even Byte  |

|               | L         | Н           | Ш    | Н  | L   | Н   | Н     | Н     | High-Z     | Invalid    |

| Word Access   | L         | L           | Ш    | Χ  | L   | Н   | Н     | Н     | Invalid    | Even Byte  |

| Odd Byte      | L         | Ш           | Η    | Χ  | L   | Н   | Н     | Н     | Invalid    | High-Z     |

| Attribute Mer | mory Writ | te Functio  | n    |    |     |     |       |       |            |            |

| Standby       | Χ         | Н           | Η    | Χ  | Χ   | Χ   | Χ     | Χ     | don't care | don't care |

| Byte Access   | L         | Н           | L    | L  | Н   | L   | Н     | Н     | don't care | Even Byte  |

|               | L         | Н           | L    | Н  | Н   | L   | Н     | Н     | don't care | don't care |

| Word Access   | L         | Ш           | Ш    | Χ  | Н   | L   | Н     | Н     | don't care | Even Byte  |

| Odd Byte      | L         | L           | Η    | Χ  | Н   | L   | Н     | Н     | don't care | don't care |

| Common Me     | mory Rea  | ad Function | on   |    |     |     |       |       |            |            |

| Standby       | Χ         | Н           | Η    | Χ  | Χ   | Χ   | Χ     | Χ     | High-Z     | High-Z     |

| Byte Access   | Η         | Н           | L    | L  | L   | Н   | Н     | Н     | High-Z     | Even Byte  |

|               | Н         | Н           | L    | Н  | L   | Н   | Н     | Н     | High-Z     | Odd Byte   |

| Word Access   | Н         | L           | Ш    | Χ  | L   | Н   | Н     | Н     | Odd Byte   | Even Byte  |

| Odd Byte      | Н         | Ш           | Η    | Х  | L   | Н   | Н     | Н     | Odd Byte   | High-Z     |

| Common Me     | mory Wri  | te Function | on   |    |     |     |       |       |            |            |

| Standby       | Χ         | Н           | Н    | Χ  | Χ   | Χ   | Χ     | Χ     | don't care | don't care |

| Byte Access   | I         | Н           | L    | L  | Н   | L   | Н     | Н     | don't care | Even Byte  |

|               | Н         | Н           | L    | Н  | Н   | L   | Н     | Н     | don't care | Odd Byte   |

| Word Access   | Η         | L           | L    | Χ  | Н   | L   | Н     | Н     | Odd Byte   | Even Byte  |

| Odd Byte      | Н         | L           | Н    | Χ  | Н   | L   | Н     | Н     | Odd Byte   | don't care |

| I/O Read Fun  | ction     |             |      |    |     |     |       |       |            |            |

| Standby       | Χ         | Н           | Η    | Χ  | Χ   | Χ   | Χ     | Χ     | High-Z     | High-Z     |

| Byte Access   | L         | Н           | L    | L  | Н   | Н   | L     | Н     | High-Z     | Even Byte  |

|               | L         | Н           | L    | Н  | Н   | Н   | L     | Н     | High-Z     | Odd Byte   |

| Word Access   | L         | L           | L    | Х  | Н   | Н   | L     | Н     | Odd Byte   | Even Byte  |

| Odd Byte      | L         | L           | Н    | Χ  | Н   | Н   | L     | Н     | Odd Byte   | High-Z     |

| I/O Write Fun | nction    |             |      |    |     |     |       |       |            |            |

| Standby       | Χ         | Н           | Н    | Х  | Х   | Х   | Х     | Х     | don't care | don't care |

| Byte Access   | L         | Н           | L    | L  | Н   | Н   | Н     | L     | don't care | Even Byte  |

|               | L         | Н           | L    | Н  | Н   | Н   | Н     | L     | don't care | Odd Byte   |

| Word Access   | L         | L           | L    | Χ  | Н   | Н   | Н     | L     | Odd Byte   | Even Byte  |

| Odd Byte      | L         | L           | Η    | Χ  | Н   | Н   | Н     | L     | Odd Byte   | don't care |

Memory mapped mode(Index=0)

|      |      |      |     | ode(In | _  |     |    |    |                                 |                                 |

|------|------|------|-----|--------|----|-----|----|----|---------------------------------|---------------------------------|

| REG# | CE2# | CE1# | A10 | A9-A4  | A3 | A2  | A1 | A0 |                                 | egister                         |

|      |      |      |     |        |    |     |    |    | OE#="L"                         | WE#="L"                         |

| 1    | 0    | 0    | 0   | Х      | 0  | 0   | 0  | Х  | Data Register(D15-D0)           | Data Register(D15-D0)           |

| 1    | 1    | 0    | 0   | Х      | 0  | 0   | 0  | 0  | Data Register[Even, Odd](D7-D0) | Data Register[Even, Odd](D7-D0) |

| 1    | 1    | 0    | 0   | Х      | 0  | 0   | 0  | 1  | Error Register(D7-D0)           | Feature Register(D7-D0)         |

| 1    | 0    | 1    | 0   | Х      | 0  | 0   | 0  | Х  | Error Register(D15-D8)          | Feature Register(D15-D8)        |

| 1    | 0    | 0    | 0   | Х      | 0  | 0   | 1  | Х  | Sector Count Register(D7-D0)    | Sector Count Register(D7-D0)    |

|      |      |      |     |        |    |     |    |    | Sector Number Register(D15-D8)  | Sector Number Register(D15-D8)  |

| 1    | 1    | 0    | 0   | Х      | 0  | 0   | 1  | 0  | Sector Count Register(D7-D0)    | Sector Count Register(D7-D0)    |

| 1    | 1    | 0    | 0   | Х      | 0  | 0   | 1  | 1  | Sector Number Register(D7-D0)   | Sector Number Register(D7-D0)   |

| 1    | 0    | 1    | 0   | Х      | 0  | 0   | 1  | Х  | Sector Number Register(D15-D8)  | Sector Number Register(D15-D8)  |

| 1    | 0    | 0    | 0   | х      | 0  | 1   | 0  | Х  | Cylinder Low Register(D7-D0)    | Cylinder Low Register(D7-D0)    |

|      |      |      |     |        |    |     |    |    | Cylinder High Register(D15-D8)  | Cylinder High Register(D15-D8)  |

| 1    | 1    | 0    | 0   | Х      | 0  | 1   | 0  | 0  | Cylinder Low Register(D7-D0)    | Cylinder Low Register(D7-D0)    |

| 1    | 1    | 0    | 0   | Х      | 0  | 1   | 0  | 1  | Cylinder High Register(D7-D0)   | Cylinder High Register(D7-D0)   |

| 1    | 0    | 1    | 0   | Х      | 0  | 1   | 0  | Х  | Cylinder High Register(D15-D8)  | Cylinder High Register(D15-D8)  |

| 1    | 0    | 0    | 0   | Х      | 0  | 1   | 1  | Х  | Drive Head Register(D7-D0)      | Drive Head Register(D7-D0)      |

|      |      |      |     |        |    |     |    |    | Status Register(D15-D8)         | Command Register(D15-D8)        |

| 1    | 1    | 0    | 0   | Х      | 0  | 1   | 1  | 0  | Drive Head Register(D7-D0)      | Drive Head Register(D7-D0)      |

| 1    | 1    | 0    | 0   | Х      | 0  | 1   | 1  |    |                                 | Command Register(D7-D0)         |

| 1    | 0    | 1    | 0   | Х      | 0  | 1   | 1  | Х  | Status Register(D15-D8)         | Command Register(D15-D8)        |

| 1    | 0    | 0    | 0   | Х      | 1  | 0   | 0  | Х  | Data Register(D15-D0)           | Data Register(D15-D0)           |

| 1    | 1    | 0    | 0   | Х      | 1  | 0   | 0  | 0  | Data Register[Even, Odd](D7-D0) | Data Register[Even, Odd](D7-D0) |

| 1    | 1    | 0    | 0   | Х      | 1  | 0   | 0  | 1  | Data Register[Odd](D7-D0)       | Data Register[Odd](D7-D0)       |

| 1    | 0    | 1    | 0   | Х      | 1  | 0   | 0  | Х  | Data Register[Odd](D15-D8)      | Data Register[Odd](D15-D8)      |

| 1    | 0    | 0    | 0   | Х      | 1  | 1   | 0  | Х  | invalid(D7-D0)                  | invalid(D7-D0)                  |

|      |      |      |     |        |    |     |    |    | Error Register(D15-D8)          | Feature Register(D15-D8)        |

| 1    | 1    | 0    | 0   | Х      | 1  | _1_ | 0  | 0  | invalid                         | invalid                         |

| 1    | 1    | 0    | 0   | Х      | 1  | 1   | 0  | 1  | Error Register(D7-D0)           | Feature Register(D7-D0)         |

| 1    | 0    | 1    | 0   | Х      | 1  | 1   | 0  | Х  | Error Register(D15-D8)          | Feature Register(D15-D8)        |

| 1    | 0    | 0    | 0   | Х      | 1  | 1   | 1  | Х  | Alt. Status Register(D7-D0)     | Device Control Register(D7-D0)  |

|      |      |      |     |        |    |     |    |    | Drive Address Register(D15-D8)  | invalid                         |

| 1    | 1    | 0    | 0   | Х      | 1  | 1   | 1  | 0  | Alt. Status Register(D7-D0)     | Device Control Register(D7-D0)  |

| 1    | 1    | 0    | 0   | х      | 1  | 1   | 1  | 1  | Drive Address Register(D7-D0)   | invalid                         |

| 1    | 0    | 1    | 0   | х      | 1  | 1   | 1  | Х  | Drive Address Register(D15-D8)  | invalid                         |

| 1    | 0    | 0    | 1   | Х      | Х  | Х   | Х  | Х  | Data Register(D15-D0)           | Data Register(D15-D0)           |

| 1    | 1    | 0    | 1   | Х      | Х  | Х   | Х  | 0  | Data Register[Even, Odd](D7-D0) | Data Register[Even, Odd](D7-D0) |

| 1    | 1    | 0    | 1   | х      | Х  | Х   | Х  | 1  | Data Register[Odd](D7-D0)       | Data Register[Odd](D7-D0)       |

| 1    | 0    | 1    | 1   | Х      | Χ  | Χ   | Χ  | Χ  | Data Register[Odd](D15-D8)      | Data Register[Odd](D15-D8)      |

#### **MITSUBISHI STORAGE CARD**

# MF0XXXX-04BAXX series CompactFlash CARDS

Contiguous I/O Map(Index=1)

| Contigu | ious I/0 | <b>Э Мар</b> ( | Index=1 | 1) |    |    |                                        |                                 |                                 |

|---------|----------|----------------|---------|----|----|----|----------------------------------------|---------------------------------|---------------------------------|

| REG#    | CE2#     | CE1#           | A9-A4   | A3 | A2 | A1 | A0                                     | Reg                             | jister                          |

|         |          |                |         |    |    |    |                                        | IORD#="L"                       | IOWR#="L"                       |

| 0       | 0        | 0              | Х       | 0  | 0  | 0  | Х                                      | Data Register(D15-D0)           | Data Register(D15-D0)           |

| 0       | 1        | 0              | Х       | 0  | 0  | 0  | 0 Data Register[Even, Odd](D7-D0) Data |                                 | Data Register[Even, Odd](D7-D0) |

| 0       | 1        | 0              | Х       | 0  | 0  | 0  | D 1 Error Register(D7-D0) F            |                                 | Feature Register(D7-D0)         |

| 0       | 0        | 1              | Х       | 0  | 0  | 0  | Х                                      | Error Register(D15-D8)          | Feature Register(D15-D8)        |

| 0       | 0        | 0              | Х       | 0  | 0  | 1  | 0                                      | Sector Count Register(D7-D0)    | Sector Count Register(D7-D0)    |

|         |          |                |         |    |    |    |                                        | Sector Number Register(D15-D8)  | Sector Number Register(D15-D8)  |

| 0       | 1        | 0              | Х       | 0  | 0  | 1  | 0                                      | Sector Count Register(D7-D0)    | Sector Count Register(D7-D0)    |

| 0       | 1        | 0              | Х       | 0  | 0  | 1  | 1                                      | Sector Number Register(D7-D0)   | Sector Number Register(D7-D0)   |

| 0       | 0        | 1              | Х       | 0  | 0  | 1  | Х                                      | Sector Number Register(D15-D8)  | Sector Number Register(D15-D8)  |

| 0       | 0        | 0              | х       | 0  | 1  | 0  | 0                                      | Cylinder Low Register(D7-D0)    | Cylinder Low Register(D7-D0)    |

|         |          |                |         |    |    |    |                                        | Cylinder High Register(D15-D8)  | Cylinder High Register(D15-D8)  |

| 0       | 1        | 0              | Х       | 0  | 1  | 0  | 0                                      | Cylinder Low Register(D7-D0)    | Cylinder Low Register(D7-D0)    |

| 0       | 1        | 0              | Х       | 0  | 1  | 0  | 1                                      | Cylinder High Register(D7-D0)   | Cylinder High Register(D7-D0)   |

| 0       | 0        | 1              | Х       | 0  | 1  | 0  | Х                                      | Cylinder High Register(D15-D8)  | Cylinder High Register(D15-D8)  |

| 0       | 0        | 0              | Х       | 0  | 1  | 1  | 0                                      | Drive Head Register(D7-D0)      | Drive Head Register(D7-D0)      |

|         |          |                |         |    |    |    |                                        | Status Register(D15-D8)         | Command Register(D15-D8)        |

| 0       | 1        | 0              | Х       | 0  | 1  | 1  | 0                                      | Drive Head Register(D7-D0)      | Drive Head Register(D7-D0)      |

| 0       | 1        | 0              | Х       | 0  | 1  | 1  | 1                                      | Status Register(D7-D0)          | Command Register(D7-D0)         |

| 0       | 0        | 1              | Х       | 0  | 1  | 1  | Х                                      | Status Register(D15-D8)         | Command Register(D15-D8)        |

| 0       | 0        | 0              | Х       | 1  | 0  | 0  | Х                                      | Data Register(D15-D0)           | Data Register(D15-D0)           |

| 0       | 1        | 0              | Х       | 1  | 0  | 0  | 0                                      | Data Register[Even, Odd](D7-D0) | Data Register[Even, Odd](D7-D0) |

| 0       | 1        | 0              | Х       | 1  | 0  | 0  | 1                                      | Data Register[Odd](D7-D0)       | Data Register[Odd](D7-D0)       |

| 0       | 0        | 1              | Х       | 1  | 0  | 0  | Х                                      | Data Register[Odd](D15-D8)      | Data Register[Odd](D15-D8)      |

| 0       | 0        | 0              | Х       | 1  | 1  | 0  | 0                                      | invalid(D7-D0)                  | invalid(D7-D0)                  |

|         |          |                |         |    |    |    |                                        | Error Register(D15-D8)          | Feature Register(D15-D8)        |

| 0       | 1        | 0              | Х       | 1  | 1  | 0  | 0                                      | invalid                         | invalid                         |

| 0       | 1        | 0              | Х       | 1  | 1  | 0  | 1                                      | Error Register(D7-D0)           | Feature Register(D7-D0)         |

| 0       | 0        | 1              | Х       | 1  | 1  | 0  | Х                                      | Error Register(D15-D8)          | Feature Register(D15-D8)        |

| 0       | 0        | 0              | Х       | 1  | 1  | 1  | 0                                      | Alt. Status Register(D7-D0)     | Device Control Register(D7-D0)  |

|         |          |                |         |    |    |    |                                        | Drive Address Register(D15-D8)  | invalid                         |

| 0       | 1        | 0              | Х       | 1  | 1  | 1  | 0                                      | Alt. Status Register(D7-D0)     | Device Control Register(D7-D0)  |

| 0       | 1        | 0              | Х       | 1  | 1  | 1  | 1                                      | Drive Address Register(D7-D0)   | invalid                         |

| 0       | 0        | 1              | Х       | 1  | 1  | 1  | х                                      | Drive Address Register(D15-D8)  | invalid                         |

Primary(Secondary) I/O(Index=2, 3)

| REG# | CE2# | CE1# | A9-A4    | А3 | A2 | A1 | Α0 | Reg                             | gister                          |

|------|------|------|----------|----|----|----|----|---------------------------------|---------------------------------|

|      |      |      |          |    |    |    |    | IORD#="L"                       | IOWR#="L"                       |

| 0    | 0    | 0    | 1Fh(17h) | 0  | 0  | 0  | Х  | Data Register(D15-D0)           | Data Register(D15-D0)           |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 0  | 0  | 0  | Data Register[Even, Odd](D7-D0) | Data Register[Even, Odd](D7-D0) |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 0  | 0  | 1  | Error Register(D7-D0)           | Feature Register(D7-D0)         |

| 0    | 0    | 1    | 1Fh(17h) | 0  | 0  | 0  | Х  | Error Register(D15-D8)          | Feature Register(D15-D8)        |

| 0    | 0    | 0    | 1Fh(17h) | 0  | 0  | 1  | 0  | Sector Count Register(D7-D0)    | Sector Count Register(D7-D0)    |

|      |      |      |          |    |    |    |    | Sector Number Register(D15-D8)  | Sector Number Register(D15-D8)  |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 0  | 1  | 0  | Sector Count Register(D7-D0)    | Sector Count Register(D7-D0)    |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 0  | 1  | 1  | Sector Number Register(D7-D0)   | Sector Number Register(D7-D0)   |

| 0    | 0    | 1    | 1Fh(17h) | 0  | 0  | 1  | Х  | Sector Number Register(D15-D8)  | Sector Number Register(D15-D8)  |

| 0    | 0    | 0    | 1Fh(17h) | 0  | 1  | 0  | 0  | Cylinder Low Register(D7-D0)    | Cylinder Low Register(D7-D0)    |

|      |      |      |          |    |    |    |    | Cylinder High Register(D15-D8)  | Cylinder High Register(D15-D8)  |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 1  | 0  | 0  | Cylinder Low Register(D7-D0)    | Cylinder Low Register(D7-D0)    |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 1  | 0  | 1  | Cylinder High Register(D7-D0)   | Cylinder High Register(D7-D0)   |

| 0    | 0    | 1    | 1Fh(17h) | 0  | 1  | 0  | Х  | Cylinder High Register(D15-D8)  | Cylinder High Register(D15-D8)  |

| 0    | 0    | 0    | 1Fh(17h) | 0  | 1  | 1  | 0  | Drive Head Register(D7-D0)      | Drive Head Register(D7-D0)      |

|      |      |      |          |    |    |    |    | Status Register(D15-D8)         | Command Register(D15-D8)        |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 1  | 1  | 0  | Drive Head Register(D7-D0)      | Drive Head Register(D7-D0)      |

| 0    | 1    | 0    | 1Fh(17h) | 0  | 1  | 1  | 1  | Status Register(D7-D0)          | Command Register(D7-D0)         |

| 0    | 0    | 1    | 1Fh(17h) | 0  | 1  | 1  | Х  | Status Register(D15-D8)         | Command Register(D15-D8)        |

| 0    | 0    | 0    | 3Fh(37h) | 0  | 1  | 1  | 0  | Alt. Status Register(D7-D0)     | Device Control Register(D7-D0)  |

|      |      |      |          |    |    |    |    | Drive Address Register(D15-D8)  | invalid                         |

| 0    | 1    | 0    | 3Fh(37h) | 0  | 1  | 1  | 0  | Alt. Status Register(D7-D0)     | Device Control Register(D7-D0)  |

| 0    | 1    | 0    | 3Fh(37h) | 0  | 1  | 1  | 1  | Drive Address Register(D7-D0)   | invalid                         |

| 0    | 0    | 1    | 3Fh(37h) | 0  | 1  | 1  | Х  | Drive Address Register(D15-D8)  | invalid                         |

#### **True IDE Interface**

| CS1# | CS0# | A2-A0 | Register                      |                                |  |  |

|------|------|-------|-------------------------------|--------------------------------|--|--|

|      |      |       | IORD#="L"                     | IOWR#="L"                      |  |  |

| 1    | 0    | 0h    | Data Register(D15-D0)         | Data Register(D15-D0)          |  |  |

| 1    | 0    | 1h    | Error Register(D7-D0)         | Feature Register(D7-D0)        |  |  |

| 1    | 0    | 2h    | Sector Count Register(D7-D0)  | Sector Count Register(D7-D0)   |  |  |

| 1    | 0    | 3h    | Sector Number Register(D7-D0) | Sector Number Register(D7-D0)  |  |  |

| 1    | 0    | 4h    | Cylinder Low Register(D7-D0)  | Cylinder Low Register(D7-D0)   |  |  |

| 1    | 0    | 5h    | Cylinder High Register(D7-D0) | Cylinder High Register(D7-D0)  |  |  |

| 1    | 0    | 6h    | Drive Head Register(D7-D0)    | Drive Head Register(D7-D0)     |  |  |

| 1    | 0    | 7h    | Status Register(D7-D0)        | Command Register(D7-D0)        |  |  |

| 0    | 1    | 6h    | Alt. Status Register(D7-D0)   | Device Control Register(D7-D0) |  |  |

| 0    | 1    | 7h    | Drive Address Register(D7-D0) | invalid                        |  |  |

#### **Configuration Register Specifications**

#### **Configuration Option Register**

This register is used for the configuration of the card configuration status and for the issuing soft reset to the card.

| D7     | D6      | D5 | D4 | D3 | D2  | D1 | D0 |

|--------|---------|----|----|----|-----|----|----|

| SRESET | LevIREQ |    |    | In | dex |    |    |

|         | 1   |                                                                                                                                                                                                                                                                                                            |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | R/W | Description                                                                                                                                                                                                                                                                                                |

| SRESET  | R/W | Setting this bit to "1", places the card in the reset state. When the host returns this bit to "0", the function shall enter the same unconfigured, reset state as the card does following a power-up and hardware reset.                                                                                  |

| LevIREQ | R/W | If this bit is set to "0", card generates pulse mode interrupt. If this bit is set to "1", card generates level mode interrupts.                                                                                                                                                                           |

| Index   | R/W | This bits is used for select operation mode of the card as follows.  When Power on, Card Hard Reset and Soft reset, this data is "000000" for the purpose of Memory card interface recognition.  Index: 0 -> Memory mapped  1 -> Contiguous I/O mapped  2 -> Primary I/O mapped  3 -> Secondary I/O mapped |

### **Configuration and Status Register**

This register is used for observing the card state.

| D7      | D6     | D5    | D4 | D3 | D2     | D1   | D0 |

|---------|--------|-------|----|----|--------|------|----|

| Changed | SigChg | lois8 | 0  | 0  | PwrDwn | Intr | 0  |

| Name    | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changed | R/O | This bit indicates that CREADY bit on the Pin Replacement register is set to "1". When Changed bit is set to "1", STSCHG# pin is held "L" if the SigChg bit is "1" and the card is configured for the I/O interface.                                                                                                                                                                                                    |

| SigChg  | R/W | This bit is set or reset by the host for enabling and disabling the status change signal(STSCHG# pin). When the card is configured I/O card interface and this bit is set to "1", STSCHG# pin is controlled by Changed bit. If this bit is set to "0", STSCHG# pin is kept "H".                                                                                                                                         |

| lois8   | R/W | This card is always configured for both 8-bit and 16-bit I/O, so this bit is ignored.                                                                                                                                                                                                                                                                                                                                   |

| PwrDwn  | R/W | When this bit is set to "1", the card enters Power Down mode. When this bit is reset to "0", the host is requesting the card to enter the active mode. RREADY bit on Pin Replacement Register becomes BUSY when this bit is changed. RREADY will not become Ready until the power state requested has been entered. This card automatically powers down when it is idle, and powers back up when it receives a command. |

| Intr    | R/W | This bit represents the internal state of the interrupt request. This bit state is available whether I/O card interface has been configured or not. This signal remains True until the condition which caused the interrupt request has been serviced. If interrupts are disabled by the nIEN bit in the Device Control Register, this bit is a zero.                                                                   |

#### Pin Replacement Register

This register is used for providing the signal state of READY signal when the card configured I/O card interface.

| D7 | D6 | D5     | D4 | D3 | D2 | D1     | D0 |

|----|----|--------|----|----|----|--------|----|

| 0  | 0  | CREADY | 0  | 1  | 1  | RREADY | 0  |

| Name   | R/W | Description                                                                                                       |

|--------|-----|-------------------------------------------------------------------------------------------------------------------|

| CREADY | R/W | This bit is set to "1" when the RREADY bit changes state. This bit may also be written by the host.               |

| RREADY | R/W | When read, this bit indicates READY pin states. When written, this bit acts as a mask for writing the CREADY bit. |

#### **Socket and Copy Register**

This register is used for identification of the card from the other cards. Host can read and write this register. This register should be set by host before this card's Configuration Option register set.

| D7 | D6 | D5      | D4 | D3 | D2     | D1     | D0 |

|----|----|---------|----|----|--------|--------|----|

| 0  | Co | py Numb | er |    | Socket | Number |    |

| Name             | R/W | Description                                                                                                                                                                                                                                                                         |

|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copy Number      | R/W | This bit indicates the drive number of the card for twin card configuration.  And the host can select and drive one card by comparing the number in this field with the drive number of Drive Head Register. In the way, the host can perform the card's master/slave organization. |

| Socket<br>Number | R/W | This field indicates to the card that it is located in the n'th socket.                                                                                                                                                                                                             |

#### **CIS Information**

CIS informatoins are defined as follows.

| Offset         | Data       | 7   | 6      | 5        | 4           | 3                            | 2       | 1        |     | 0     | Description                                                                |  |  |

|----------------|------------|-----|--------|----------|-------------|------------------------------|---------|----------|-----|-------|----------------------------------------------------------------------------|--|--|

| 0000h          | 01h        |     |        |          | CISTP       | L DEVIC                      | F       |          |     |       | Common Memory device information                                           |  |  |

| 0000h          | 03h        |     |        |          |             | L_BLVIO                      |         |          |     |       | Link to next tuple                                                         |  |  |

| 0004h          | D9h        |     | Device | е Туре   |             | WPS                          |         | Device   | Sp  | peed  | Device Type=Dh : Function specific WPS=1 : No WPS Device Speed=1 : 250ns   |  |  |

| 0006h          | 01h        |     |        | 1x       |             |                              |         | 2        | 2K  |       | 2kBytes of address space                                                   |  |  |

| 0008h          | FFh        |     |        | Mar      | ks end of   | Device Info fields           |         |          |     |       | ,                                                                          |  |  |

| 000Ah          | 1Ch        |     |        |          | CISTPL_     |                              |         |          |     |       | Other Conditions Device information                                        |  |  |

| 000Ch          | 05h        |     |        |          |             | L_LINK                       |         |          |     |       | Link to next tuple                                                         |  |  |

| 000Eh          | 02h        | EXT |        | Res      | erved       |                              |         | Vcc      |     | MWAIT | EXT=0, Vcc=5.0V, Wait is not used.                                         |  |  |

| 0010h          | DFh        |     | Device |          |             | WPS                          |         | Device   | Sp  |       | Device Type=Dh : Function specific<br>WPS=1 : No WPS<br>Device Speed=250ns |  |  |

| 0012h          | 01h        |     |        | 1x       |             |                              |         | 2        | 2K  |       | 2kbytes of address space                                                   |  |  |

| 0014h          | FFh        |     | N      | larks en | d of Other  | r Conditio                   | ns Devi | ce Info  |     |       |                                                                            |  |  |

| 0016h          | 1Ch        |     |        |          | CISTPL_     | DEVICE                       | OC      |          |     |       | Other Conditions Device information                                        |  |  |

| 0018h          | 04h        |     |        |          | TPI         | L_LINK                       |         |          |     |       | Link to next tuple                                                         |  |  |

| 001Ah          | 02h        | EXT |        | Res      | erved       |                              |         | Vcc      |     | MWAIT | EXT=0, Vcc=3.3V, Wait is not used.                                         |  |  |

| 001Ch          | D9h        |     | Device | е Туре   |             | WPS                          |         | Device   | Sp  | peed  | Device Type=Dh : Function specific<br>WPS=1 : No WPS<br>Device Speed=250ns |  |  |

| 001Eh          | 01h        |     |        | 1x       |             |                              |         | 2        | 2K  |       | 2kbytes of address space                                                   |  |  |

| 0020h          | FFh        |     | N      | larks en | d of Other  | r Conditio                   | ns Devi | ce Info  |     |       |                                                                            |  |  |

| 0022h          | 18h        |     |        |          |             | JEDEC                        |         |          |     |       | JEDEC Identifier Tuples                                                    |  |  |

| 0024h          | 02h        |     |        |          |             | L_LINK                       |         |          |     |       | Link to next tuple                                                         |  |  |

| 0026h          | DFh        |     | J      | EDEC id  |             | r first device info entry.   |         |          |     |       | PC Card ATA                                                                |  |  |

| 0028h          | 01h        |     |        |          |             | maining device info entries. |         |          |     |       | with no Vpp require for any operation                                      |  |  |

| 002Ah          | 20h        |     | 0222   | O Idona  |             | L_MANFI                      |         | no ontin | 00. |       | Manufacturer Identification Tuple                                          |  |  |

| 0027th         | 04h        |     |        |          |             | L LINK                       |         |          |     |       | Link to next tuple                                                         |  |  |

| 002Eh          | 1Ch        |     |        | PC       | Card ma     |                              | ar code |          |     |       | 001Ch                                                                      |  |  |

| 0030h          | 00h        |     |        |          | ) Oald Ille | and dotal of code            |         |          |     |       | 001011                                                                     |  |  |

| 0030h          | 01h        |     |        |          | nanufactu   | rer information              |         |          |     |       | 0001h                                                                      |  |  |

| 0032h          | 00h        |     |        | '        | ilailulactu | rei information              |         |          |     |       | 000111                                                                     |  |  |

| 0034h          | 15h        |     |        |          | CISTD       | L_VERS_1                     |         |          |     |       | Level 1 Version / Product Information                                      |  |  |

| 0038h          | 1Ch        |     |        |          |             | L_VERO_<br>L LINK            | _!      |          |     |       | Link to next tuple                                                         |  |  |

| 003Ah          | 04h        |     |        |          |             | /1_MAJO                      | P       |          |     |       | PCMCIA2.0 / JEIDA4.1                                                       |  |  |

| 003An          | 04H        |     |        |          |             | /1_MINO                      |         |          |     |       | PCMCIA2.0 / JEIDA4.1                                                       |  |  |

| 003Eh          | 4Dh        |     |        |          |             |                              |         |          |     |       |                                                                            |  |  |

| 003En          | 49h        | 1   |        |          | IFLL        | LV1_INFO                     |         |          |     |       | M<br>I                                                                     |  |  |

| 0040h<br>0042h | 49n<br>54h | 1   |        |          |             | ,                            |         |          |     |       | ·                                                                          |  |  |

|                |            | 1   |        |          |             |                              |         |          |     |       | T                                                                          |  |  |

| 0044h          | 53h        |     |        |          |             |                              |         |          |     |       | S                                                                          |  |  |

| 0046h          | 55h        | 1   |        |          |             |                              |         |          |     |       | U                                                                          |  |  |

| 0048h          | 42h        | ł   |        |          |             |                              |         |          |     |       | B                                                                          |  |  |

| 004Ah          | 49h        |     |        |          |             |                              |         |          |     |       |                                                                            |  |  |

| 004Ch          | 53h        |     |        |          |             |                              |         |          |     |       | S                                                                          |  |  |

| 004Eh          | 48h        |     |        |          |             |                              |         |          |     |       | H                                                                          |  |  |

| 0050h          | 49h        |     |        |          |             |                              |         |          |     |       | I                                                                          |  |  |

| 0052h          | 00h        |     |        |          |             |                              |         |          |     |       |                                                                            |  |  |

| 0054h          | 41h        |     |        |          |             |                              |         |          |     |       | Α                                                                          |  |  |

| 0056h          | 54h        |     |        |          |             |                              |         |          |     |       | T                                                                          |  |  |

| 0058h          | 41h        |     |        |          |             |                              |         |          |     |       | Α                                                                          |  |  |

| 005Ah          | 20h        |     |        |          |             |                              |         |          |     |       |                                                                            |  |  |

| 005Ch          | 43h        |     |        |          |             |                              |         |          |     |       | С                                                                          |  |  |

| 005Eh          | 41h        |     |        |          |             |                              |         |          |     |       | A                                                                          |  |  |

| 0060h          | 52h        | 1   |        |          |             |                              |         |          |     |       | R                                                                          |  |  |

| 0062h          | 44h        | 1   |        |          |             |                              |         |          |     |       | D                                                                          |  |  |

| 0064h          | 00h        | 1   |        |          |             |                              |         |          |     |       |                                                                            |  |  |

|                |            |     |        |          |             |                              |         |          |     |       | ·                                                                          |  |  |

**CIS Information(Continued)**

| CIS Inf | ormati | on(Co | ntinuec                                                 | d)      |        |                             |            |                               |       |                                                                    |

|---------|--------|-------|---------------------------------------------------------|---------|--------|-----------------------------|------------|-------------------------------|-------|--------------------------------------------------------------------|

| Offset  | Data   | 7     | 6                                                       | 5       | 4      | 3                           | 2          | 1                             | 0     | Description                                                        |

| 0066h   | 30h    |       |                                                         |         |        |                             |            |                               |       | 3                                                                  |

| 0068h   | 2Eh    |       |                                                         |         |        |                             |            |                               |       |                                                                    |

| 006Ah   | 31h    |       |                                                         |         |        |                             |            |                               |       | 1                                                                  |

| 006Ch   | 31h    |       |                                                         |         |        |                             |            |                               |       | 1                                                                  |

| 006Eh   | 00h    |       |                                                         |         |        |                             |            |                               |       |                                                                    |

| 0070h   | FFh    |       |                                                         |         |        |                             |            |                               |       | Marks end of chain.                                                |

| 0072h   | 21h    |       |                                                         |         |        | L_FUNCI                     |            | Function Identification Tuple |       |                                                                    |

| 0074h   | 02h    |       |                                                         |         |        | LINK                        |            | Link to next tuple            |       |                                                                    |

| 0076h   | 04h    |       |                                                         |         |        | nction Co                   | de         |                               |       | PC Card ATA(Fixed Disk)                                            |

| 0078h   | 01h    |       |                                                         | Res     | erved  |                             |            | ROM                           | POST  | ROM=0 : No BIOS ROM POST=1: Configure card at power on             |

| 007Ah   | 22h    |       |                                                         |         |        | L_FUNC                      | E          |                               |       | Function Extension Tuple                                           |

| 007Ch   | 02h    |       |                                                         |         |        | LINK                        |            |                               |       | Link to next tuple                                                 |

| 007Eh   | 01h    |       |                                                         | Disk Fu |        | xtension 7                  |            | е                             |       | Disk Interface Type                                                |

| 0080h   | 01h    |       |                                                         |         |        | erface Ty                   |            |                               |       | PC Card ATA Interface                                              |

| 0082h   | 22h    |       |                                                         |         |        | L_FUNC                      | E          |                               |       | Function Extension Tuple                                           |

| 0084h   | 03h    |       |                                                         |         |        | _LINK                       |            |                               |       | Link to next tuple                                                 |

| 0086h   | 02h    |       |                                                         | Disk Fu | 1      | xtension 7                  |            | e                             |       | Basic PC Card ATA Interface tuple                                  |

| 0088h   | 04h    |       | RFU                                                     |         | D      | U                           | S          |                               | V     | V=0 : No Vpp Required                                              |

|         |        |       |                                                         |         |        |                             |            |                               |       | S=1 : Silicon                                                      |

|         |        |       |                                                         |         |        |                             |            |                               |       | U=0 : ID Drive Mfg/SN not Unique<br>D=0 : Single Drive on Card     |

| 008Ah   | 0Fh    | RFU   | 1                                                       | Е       | N      | P3                          | P2         | P1                            | P0    | P0=1 : Sleep Mode Supported                                        |

| UUUAII  | 01 11  | IXI O | '                                                       | _       | 'N     | '3                          | 12         | ' '                           | 10    | P1=1 : Standby Mode Supported                                      |

|         |        |       |                                                         |         |        |                             |            |                               |       | P2=1 : Idle Mode Supported                                         |

|         |        |       |                                                         |         |        |                             |            |                               |       | P3=1 : Drive Auto Power Control                                    |

|         |        |       |                                                         |         |        |                             |            |                               |       | N=0 : No Configs exclude I/O port                                  |

|         |        |       |                                                         |         |        |                             |            |                               |       | 3F7H/377H                                                          |

|         |        |       |                                                         |         |        |                             |            |                               |       | E=0 : Index bit is not emulated                                    |

|         |        |       |                                                         |         |        |                             |            |                               |       | I=0 : IOIS16# use is Unspecified on                                |

|         |        |       |                                                         |         | L      |                             |            |                               |       | Twin Card Configurations                                           |

| 008Ch   | 1Ah    |       |                                                         |         |        | PL_CONF                     | •          |                               |       | Configuration Tuple                                                |

| 008Eh   | 05h    |       |                                                         |         |        | _LINK                       |            |                               | D.4.0 | Link to next tuple                                                 |

| 0090h   | 01h    | R     | FS                                                      |         | 1      | RMS                         |            |                               | RAS   | RFS=0 : No Reserved Field                                          |

|         |        |       |                                                         |         |        |                             |            |                               |       | RMS=0 : 1 Byte Register Mask<br>RAS=1 : 2 Byte Config Base Address |

| 0092h   | 03h    |       |                                                         |         | TPC    | C_LAST                      |            |                               |       | Last Index = 3                                                     |

| 0094h   | 00h    |       |                                                         |         |        | RADR (Is                    | h)         |                               |       | Configuration Registers are located                                |

| 0096h   | 02h    |       |                                                         |         |        | RADR (ms                    |            |                               |       | at 200H in Reg Space                                               |

| 0098h   | 0Fh    | RFU   | RFU                                                     | RFU     | E      | S                           | P          | С                             | 1     | First 4 Configuration Registers present                            |

| 009Ah   | 1Bh    | 0     | 0                                                       |         |        | TABLE_E                     | 1          |                               |       | Configuration Table Entry Tuple                                    |

| 009Ch   | 08h    |       |                                                         |         |        | _ LINK                      |            |                               |       | Link to next tuple                                                 |

| 009Eh   | C0h    | I     | D                                                       |         |        |                             | ration Ind | ex                            |       | Interface Byte Follows, Default Entry,                             |

|         |        |       |                                                         |         |        |                             |            |                               |       | Configuration Index = 0                                            |

| 00A0h   | 40h    | W     | R                                                       | Р       | В      |                             | Interfa    | асе Туре                      |       | Mem Interface; Bvd's and wProt not                                 |

|         |        |       |                                                         |         |        |                             |            |                               |       | used; Ready active and Wait not used                               |

|         |        |       |                                                         |         |        |                             |            |                               |       | for memory cycles.                                                 |

| 00A2h   | A1h    | М     | M                                                       |         | IR     | 10                          | Т          |                               | Р     | Has Vcc, Mem Space and Misc Info                                   |

| 00A4h   | 01h    | R     | DI                                                      | PI      | Al     | SI                          | HV         | LV                            | NV    | Nominal Voltage Only Follows                                       |

| 00A6h   | 55h    | Х     | Mantissa Exponent Length in 256 bytes pages (Isb)       |         |        |                             |            |                               |       | Vcc Nominal is 5 Volts                                             |

| 00A8h   | 08h    |       |                                                         |         |        | Length of Mem Space is 2 KB |            |                               |       |                                                                    |

| 00AAh   | 00h    |       | Length in 256 bytes pages (msb)                         |         |        |                             |            |                               |       | Starts at 0 on card                                                |

| 00ACh   | 21h    | Х     | K   RFU   P   RO   A   T   T   T   CISTPL_CFTABLE_ENTRY |         |        |                             |            |                               |       | Power Down, Twin Card supported.                                   |

| 00AEh   | 1Bh    |       |                                                         | CIS     |        |                             | NIRY       |                               |       | Configuration Table Entry Tuple                                    |

| 00B0h   | 05h    |       |                                                         |         | IPL    | LINK                        |            |                               |       | Link to next tuple                                                 |

| 00B2h   | 00h    | I     | D                                                       |         |        |                             | ration Ind | ex                            |       | No Interface Byte, Non Default Entry,<br>Configuration Index = 0   |

| 00B4h   | 01h    | М     | M                                                       |         | IR     | 10                          | Т          |                               | Р     | Has Vcc Info                                                       |

| 00B6h   | 01h    | R     | DI                                                      | PI      | Al     | SI                          | HV         | LV                            | NV    | Nominal Voltage Only Follows                                       |

| 00B8h   | B5h    | Х     |                                                         | Man     | ıtissa |                             |            | Expone                        | nt    | Vcc Nominal is 3.3 Volts                                           |

| 00BAh   | 1Eh    | 1     |                                                         |         | Ext    | tension                     |            |                               |       |                                                                    |

**CIS Information(Continued)**

| CIS Inf | ormati | on(Coı | ntinued | d)       |                               |           |             |          |                                                                   |                                          |