Low Input Voltage, High Efficiency, 2.5A Integrated FET Synchronous Step down DC/DC Regulator

### **POWER MANAGEMENT**

### Description

The SC4620 is a highly integrated synchronous step-down DC/DC regulator designed for low input voltage range of 2.3V to 5.5 Volts. It can deliver 2.5A continuous output current with the output voltage as low as 0.5 Volts. The internal low  $R_{\scriptscriptstyle DS(ON)}$  synchronous power switches eliminate the need for external Schottky diode while delivering overall converter efficiency up to 95%.

A power good pin is available to monitor the output voltage status. Operating frequency is adjustable from 200 kHz to 2MHz with a single resistor and it can be synchronized to an external clock.

The SC4620 offers adjustable current limit, soft start and over temperature protection to safeguard the device under extreme operating conditions. The soft start provides a controlled output voltage ramp up at startup. When a logic low is applied to the Enable pin, the SC4620 enters the shutdown mode and it consumes less than  $1\mu A$  of current.

The SC4620 is available in 4x4 MLPQ-20 and it is rated over -40°C to +85°C ambient temperature range.

### **Features**

- ◆ VIN Range: 2.3 5.5V

- ◆ 2.5A Continuous Output Current

- ◆ Adjustable Output Voltage 0.5V to Vin

- ◆ Up to 95% Efficiency

- ◆ Synchronizable and Programmable Frequency: 200kHz – 2MHz

- Power Good Monitor

- ◆ <1uA of Shutdown Current

- ◆ Programmable Soft Start

- ◆ Programmable Current Limit

- Over Temperature protection

- ◆ -40 to +85 °C Ambient Temperature Range

- 4X4mm MLPQ-20 packages- WEEE and RoHS compliant

### **Applications**

- ◆ Low Voltage Distributed DC-DC Converters

- ◆ Telecommunication Power Supplies

- Portable Equipment

- ◆ xDSL

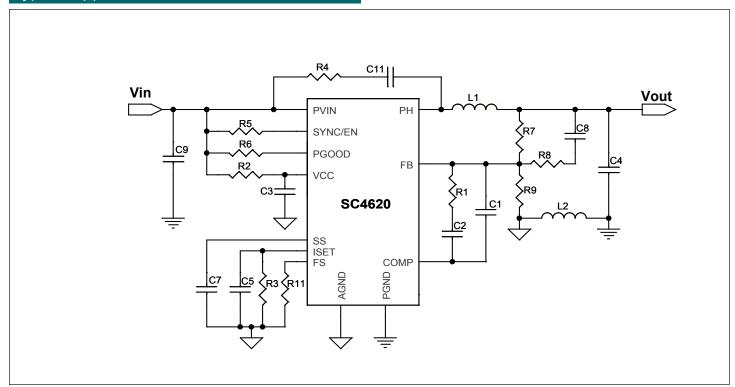

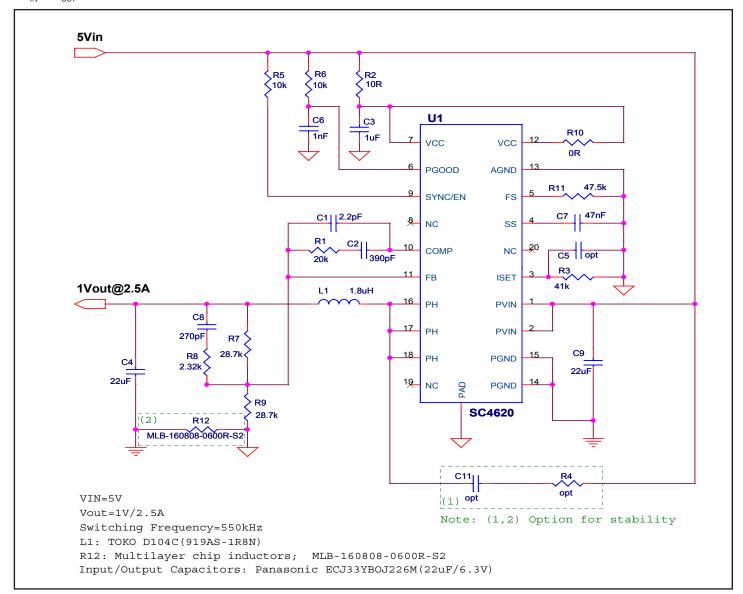

### **Typical Application Circuit**

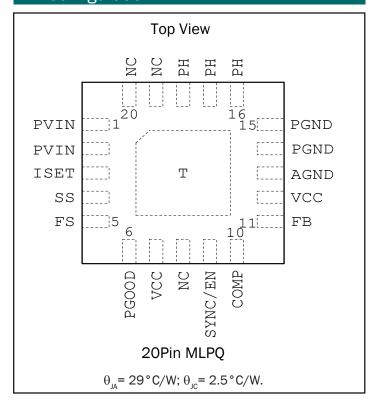

## Pin Configuration

# Ordering Information

| Device              | Top Mark   | Package  |

|---------------------|------------|----------|

| SC4620MLTRT (1) (2) | SC<br>4620 | MLPQ-20  |

| SC4620EVB-MLPQ      | Evaluation | on Board |

#### Notes:

- (1) Available in tape and reel only. A reel contains 3,000 devices for MLPQ-20 package.

- (2) Available in lead-free package only. Device is WEEE and RoHS compliant.

## **Absolute Maximum Ratings**

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                                      | Symbol                             | Maximum           | Units |

|------------------------------------------------|------------------------------------|-------------------|-------|

| Supply Voltage                                 | PV <sub>IN</sub> , V <sub>CC</sub> | -0.3 to 6         | V     |

| PVIN to VCC                                    |                                    | +/- 0.3           | V     |

| FB, COMP, ISET, SYNC/EN, FS, SS, PGOOD to AGND |                                    | -0.3 to VCC+ 0.3  | V     |

| PGND to AGND                                   |                                    | +/- 0.3           | V     |

| PHASE Voltage to PGND                          | V <sub>PHASE</sub>                 | -0.3 to PVIN+ 0.3 | V     |

| PHASE Pulse Voltage to PGND Tpulse < 50ns      | V <sub>PHASE</sub>                 | -3 to PVIN+ 2     | V     |

| Storage Temperature Range                      | T <sub>STG</sub>                   | -40 to 150        | °C    |

| Junction Temperature                           | T <sub>J</sub>                     | 150               | °C    |

| IR Reflow Temperature                          | T <sub>P</sub>                     | 260               | °C    |

## **Recommended Operating Conditions**

The Performance is not guarantied if exceeding the specifications below.

| Parameter                     | Symbol              | Conditions | Min | Тур | Max | Units |

|-------------------------------|---------------------|------------|-----|-----|-----|-------|

| Power Supply                  |                     |            |     |     |     |       |

| Input Voltage Operating Range | V <sub>IN</sub>     |            | 2.3 |     | 5.5 | V     |

| Ambient Temperature Range     | T <sub>A</sub>      |            | -40 |     | 85  | °C    |

| Junction Temperature          | T <sub>J</sub>      |            | -40 |     | 125 | °C    |

| Max. Output Current           | I <sub>OUTMAX</sub> |            | 0   |     | 2.5 | Α     |

### **Electrical Characteristics**

Unless otherwise specified,  $V_{IN} = V_{CC} = SYNC/EN = 3.3V$ ,  $R_{OSC} = 51.1K\Omega$ ,  $R_{ISET} = 27.4K\Omega$ ,  $T_A = -40\,^{\circ}C$  to  $85\,^{\circ}C$

| Parameter                     | Symbol             | Conditions             | Min | Тур | Max  | Units |

|-------------------------------|--------------------|------------------------|-----|-----|------|-------|

| Power Supply                  |                    |                        |     |     |      |       |

| Start Threshold Voltage, UVLO | V <sub>IUV</sub>   | V <sub>IN</sub> Rising |     | 2   | 2.25 | V     |

| Hysteresis Voltage, UVLO      | V <sub>IUVHY</sub> |                        |     | 120 |      | mV    |

| Supply Current, Shutdown      | I <sub>SD</sub>    | V <sub>SYNC</sub> = 0V |     | 0.2 | 1    | μA    |

| Cumply Cumput Operation       | Qswitching         | FB = COMP, No Load     |     | 7   | 10   | mA    |

| Supply Current, Operating     | I <sub>QL</sub>    | FB = 0.6V, No Load     |     | 3.5 | 7    | mA    |

## **Electrical Characteristics (Cont.)**

Unless otherwise specified,  $V_{IN} = V_{CC} = SYNC/EN = 3.3V$ ,  $R_{OSC} = 51.1$ K $\Omega$ ,  $R_{ISET} = 27.4$ K $\Omega$ ,  $T_{A} = -40$ °C to 85°C.

| Parameter                                           | Symbol               | Conditions                                                     | Min  | Тур    | Max  | Units |

|-----------------------------------------------------|----------------------|----------------------------------------------------------------|------|--------|------|-------|

| Thermal Shutdown                                    |                      |                                                                |      |        |      |       |

| Thermal Shutdown Trip Point                         | T <sub>OTP</sub>     | Temperature Rising                                             |      | 160    |      | °C    |

| Thermal Shutdown Hysteresis                         | T <sub>OTP_HYS</sub> |                                                                |      | 10     |      | °C    |

| Synchronization, Enable Input                       |                      |                                                                |      |        |      |       |

| CVNC/FN Throughold                                  | V <sub>ENL</sub>     | Logic Low                                                      |      |        | 0.8  | V     |

| SYNC/EN Threshold                                   | V <sub>ENH</sub>     | Logic High                                                     | 2.0  |        |      | V     |

| Frequency Range, SYNC                               | F <sub>SYNC</sub>    | 20% Higher than F <sub>osc</sub>                               | 200  |        | 2000 | kHz   |

| Oscillator                                          |                      |                                                                |      |        |      |       |

| Osciilator Frequency Range                          | F <sub>osc</sub>     |                                                                | 200  |        | 2000 | kHz   |

| Consider Francisco Anguiron                         |                      | R <sub>osc</sub> = 51.1KΩ                                      | 415  | 500    | 585  | kHz   |

| Osciilator Frequency Accuracy                       |                      | R <sub>osc</sub> =51.1KΩ, T <sub>A</sub> =T <sub>J</sub> =25°C | 435  | 500    | 565  | kHz   |

| Ramp Peak to Valley(1)                              | V <sub>PV</sub>      |                                                                |      | 1.0    |      | V     |

| Ramp Peak Voltage <sup>(1)</sup>                    | V <sub>P</sub>       |                                                                |      | 1.25   |      | V     |

| Ramp Valley Voltage(1)                              | V <sub>v</sub>       |                                                                |      | 0.25   |      | V     |

| Soft Start, Current Limit                           |                      |                                                                |      |        |      |       |

| Soft-Start Charge Current                           | I <sub>SS</sub>      |                                                                |      | 6      |      | μA    |

| ISET Bias Voltage                                   | V <sub>ISET</sub>    | R <sub>ISET</sub> = 27.4KΩ                                     | 0.45 | 0.55   | 0.61 | V     |

| Over Current Trip                                   | I <sub>IST</sub>     | R <sub>ISIT</sub> = 57.6KΩ                                     | 1.9  | 2.55   | 3.1  | А     |

| Output UVLO                                         | V <sub>ouv</sub>     | VFB drop                                                       |      | 0.3    |      | V     |

| Hiccup period <sup>(1)</sup>                        | T <sub>OCHP</sub>    |                                                                |      | 131072 |      | clks  |

| Error Amplifier                                     |                      |                                                                |      |        |      | '     |

| Error Amplifier Open Loop<br>Voltage Gain (1)       |                      |                                                                |      | 100    |      | dB    |

| Error Amplifier Unity Gain Bandwidth <sup>(1)</sup> |                      |                                                                |      | 10     |      | MHz   |

| Output Voltage Slew Rate, COMP(1)                   |                      |                                                                |      | 4      |      | V/µs  |

| Source Output Current, COMP                         |                      | FB = 0.4V                                                      |      | 20     |      | mA    |

| Sink Output Current, COMP                           |                      | FB = 0.6V                                                      |      | 25     |      | mA    |

| Output Voltage High, COMP                           |                      | FB = 0.4V, I <sub>COMP</sub> = -1mA                            |      | 2.5    |      | V     |

# Electrical Characteristics (Cont.)

Unless otherwise specified,  $V_{IN} = V_{CC} = SYNC/EN = 3.3V$ ,  $R_{OSC} = 51.1 \text{K}\Omega$ ,  $R_{ISET} = 27.4 \text{K}\Omega$ ,  $T_A = -40 \,^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ .

| Parameter                | Symbol               | Conditions                                                                                            | Min        | Тур         | Max         | Units |

|--------------------------|----------------------|-------------------------------------------------------------------------------------------------------|------------|-------------|-------------|-------|

| Error Amplifier (Cont.)  |                      |                                                                                                       |            |             |             |       |

| Output Voltage Low, COMP |                      | FB = 0.6V, I <sub>COMP</sub> = 1mA                                                                    |            | 0.1         | 0.25        | V     |

| Foodbook Voltage         |                      |                                                                                                       | 0.4925     | 0.5         | 0.5075      | V     |

| Feedback Voltage         | V <sub>FB</sub>      | Vcc = 2.3V to 5.5V                                                                                    | -2         | <u>+</u> 1  | +2          | %     |

| Input Bias Current(1)    | I <sub>FB</sub>      | FB=V <sub>REF</sub>                                                                                   |            |             | 60          | nA    |

| Power Switches           |                      |                                                                                                       |            |             |             |       |

| High-Side P-MOSFET       | R <sub>DSH(on)</sub> | V <sub>IN</sub> =V <sub>CC</sub> =5V, I <sub>SOURCE</sub> = 1A, T <sub>A</sub> =T <sub>J</sub> =25 °C |            | 74          | 100         | mΩ    |

| Low Side N-MOSFET        | R <sub>DSL(on)</sub> | V <sub>IN</sub> =V <sub>CC</sub> =5V, I <sub>SINK</sub> = 1A, T <sub>A</sub> =T <sub>J</sub> =25 °C   |            | 47          | 85          | mΩ    |

| Power Good               |                      |                                                                                                       |            |             |             |       |

| PGood Voltage Low        | V <sub>PGL</sub>     | I <sub>PGOOD</sub> = 1mA                                                                              |            | 0.2         |             | V     |

| PGood Leakage Current    | I <sub>PGOOD</sub>   | PGOOD = 5V                                                                                            |            |             | 1           | μА    |

| PGood Delay Time(1)      | T <sub>D</sub>       | Vout rising or Vout falling                                                                           |            | 1024        |             | clks  |

| PGood High Window        |                      | With respect to nominal output, $T_A=T_J=25~^{\circ}C$                                                | <u>+</u> 8 | <u>+</u> 10 | <u>+</u> 15 | %     |

Note:

(1) Guaranteed by design.

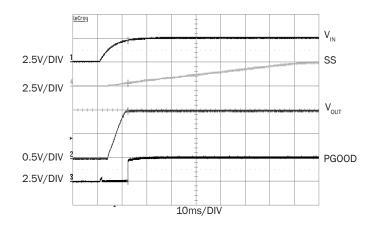

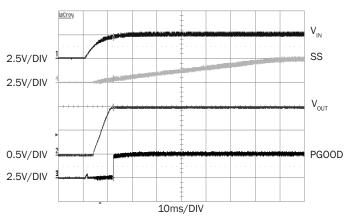

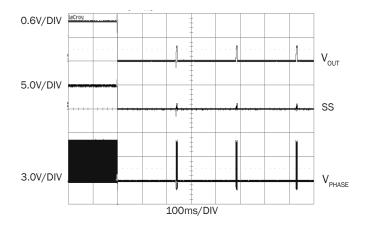

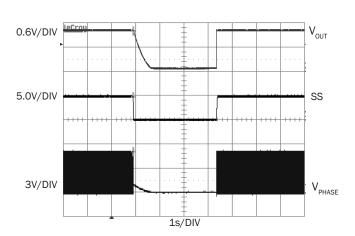

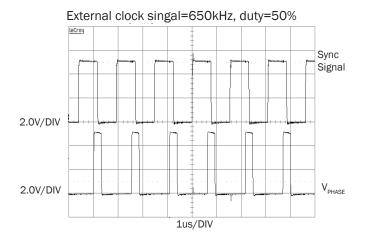

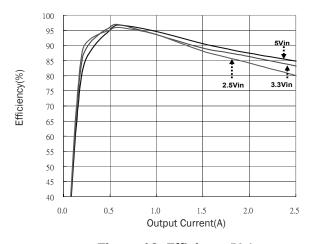

## **Typical Performance Characteristics**

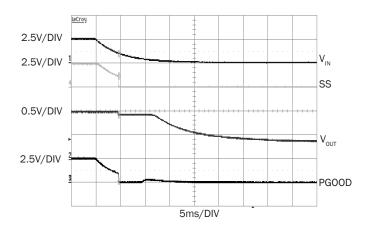

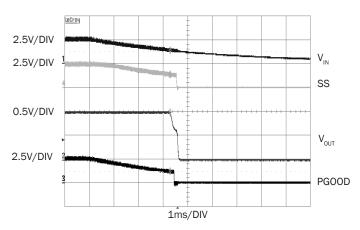

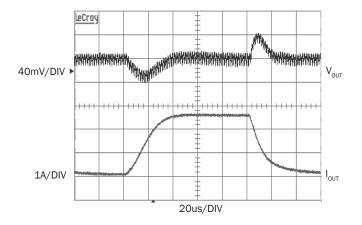

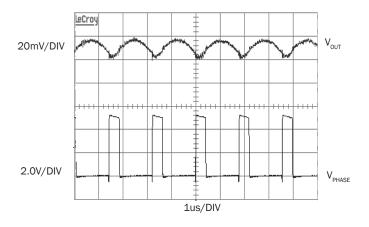

Circuit condition: Application circuit#1,  $5V_{IN}$ ,  $1V_{OUT}$

Figure 1. Start Up by  $V_{IN}@0A$

Figure 2. Start Up by V<sub>IN</sub>@2.5A

Figure 3. Shutdown by  $V_{_{\rm IN}}@0{\rm A}$

Figure 4. Shutdown by V<sub>IN</sub>@2.5A

Figure 5. Transient Response@ 0 to 2.5A

Figure 6. Ripple and Stability@2.5A

## Typical Performance Characteristics (Cont.)

Circuit condition: Application circuit#1,  $5V_{IN}$ ,  $1V_{OUT}$

Figure 7. Over Load Hiccup

Figure 8. Thermal Shutdown Protection@0A

Figure 9. Synchronization

Figure 10. Efficiency(V<sub>IN</sub>)

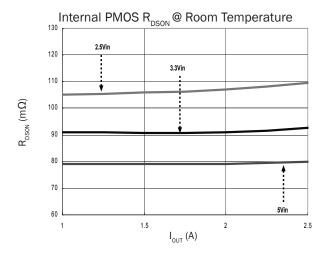

Figure 11. High-Side P-MOSFET

Figure 12. Low-Side N-MOSFET

# Typical Performance Characteristics (Cont.)

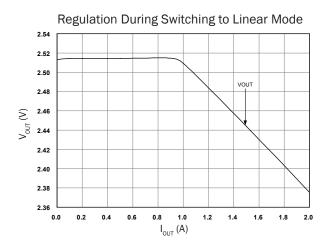

Figure 13. Loading Regulation

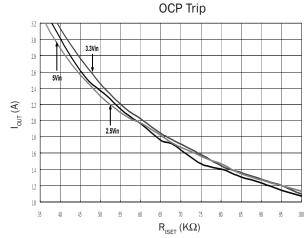

Figure 14. Over Current Setting versus  $R_{\rm ISET}$

# Pin Descriptions

| Pin<br>MLPQ-20 | Pin Name       | Pin Functions                                                                                                                                                                                                                                      |

|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2            | PVIN           | Power supply voltage for high side MOSFETs.                                                                                                                                                                                                        |

| 3              | ISET           | Current limit setting pin. A resistor connected between ISET and AGND sets the over current protection threshold. A ceramic decoupling between ISET pin to AGND have to be reserved to prevent from noise influence.                               |

| 4              | SS             | Soft start time setting pin. A cap connected from this pin to GND sets the soft start up time.                                                                                                                                                     |

| 5              | FS             | Oscillator frequency setting pin. An external resistor connected from this pin to GND sets the oscillator frequency.                                                                                                                               |

| 6              | PGOOD          | Power good indicator. It is an open drain output. Low when the output is below the power good threshold level.                                                                                                                                     |

| 7,12           | VCC            | Power supply voltage for the analog section of the controller.                                                                                                                                                                                     |

| 8,19,20        | NC             | No connection.                                                                                                                                                                                                                                     |

| 9              | SYNC/EN        | The oscillator frequency of the SC4624A is set by FS when SYNC/EN is pulled and held above 2V. Its synchronous mode is activated as SYNC/EN is driven by an external clock. Its shutdown mode is invoked if SYNC/EN is pulled and held below 0.8V. |

| 10             | COMP           | This is the output of the error amplifier. The voltage at this point is connected to the inverting input of the PWM comparator. A compensation network is required in order to optimize the dynamic performance of the voltage mode control loop.  |

| 11             | FB             | The inverting input of the error amplifier. It serves as the output voltage feedback point for the buck controller. It senses the output voltage through an external divider.                                                                      |

| 13             | AGND           | Analog signal ground.                                                                                                                                                                                                                              |

| 14,15          | PGND           | Power ground.                                                                                                                                                                                                                                      |

| 16,17,18       | PH             | Switching nodes                                                                                                                                                                                                                                    |

|                | THERMAL<br>PAD | Pad for heatsinking purposes only. Connect to ground plane using multiple vias. Not electrically connected internally.                                                                                                                             |

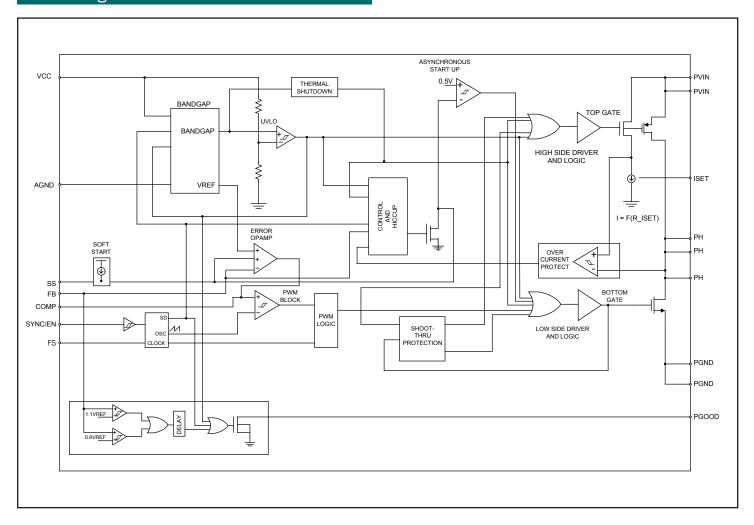

## **Block Diagram**

## Application Information

#### **Overview**

The SC4620 is a programmable high switching frequency, integrated 2.5A MOSFET, synchronous step down regulator. This reduces external component count and makes it effective for applications which are low in cost and sized small. A non-overlap protection is provided for the gate drive signals to prevent shoot through of the internal MOSFET pair.

The SC4620 is capable of producing an output voltage as low as 0.5V and Its operation frequency is programmable up to 2MHz by an external resistor. It features lossless current sensing of the voltage drop across the internal drain to source resistance of the high side MOSFET during its conduction period.

The quiescent supply current in shutdown mode is typically lower than  $1\mu A$ . An external soft start is provided to prevent output voltage overshoot during start-up. Over Temperature Protection, Power Good Indicator, External Clock Synchronization are some of the internal added features.

#### **Enable**

The SC4620 is enabled by applying a voltage greater than 2V (typical) to the  $\rm V_{cc}$  and SYNC/EN pin. The voltage on the  $\rm V_{cc}$  pin determines the operation of the SC4620. As  $\rm V_{cc}$  increases during start up, the UVLO block senses  $\rm V_{cc}$  and keeps the high side and low side MOSFETs off and the internal soft start voltage low until  $\rm V_{cc}$  reaches 2V. If no faults are present, the SC4620 will initiate a soft start when  $\rm V_{cc}$  exceeds 2V. A typical 120mV hysteresis in the UVLO comparator provides noise immunity during its start up. (refer to Figure 1 to 2).

#### **Shutdown**

The SC4620 is disabled when V $_{\rm cc}$  falls below 1.88V (typical) or shutdown mode operation is invoked by clamping the SYNC/EN pin to a voltage below 0.8V. During the shutdown mode, A typical 0.2 $\mu$ A current draw through the V $_{\rm cc}$  pin, the internal soft start voltage is held low and the internal MOSFETs are turned off. (refer to Figure 3 to 4).

#### **Soft Start**

The soft start function is required for step down controllers to prevent excess in-rush current through the DC bus during start up. An external capacitor is necessary for the soft start function and is connected from SS pin to AGND.

During start up or restart, A typical 6µA sourcing current charges the capacitor and then the voltage of capacitor ramp up the error amp reference slowly. The closed loop creates narrow width driver pulses while the output voltage is low and allows these pulses to increase to their steady state duty cycle as the output voltage reaches its regulated value. The duration of the soft start in the SC4620 is controlled by an external capacitor.

The SC4620 starts up in asynchronous mode before SS voltage reaches to 0.5V, and the bottom FET diode is used for circulating current during the top FET off time. The SS voltage level is clamped at  $V_{\rm cc}$  finally.

#### **Oscillator**

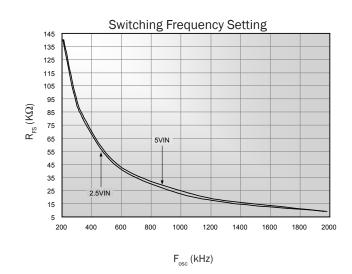

The FS pin is used to set the PWM oscillator frequency through an external resistor that is connected from the FS pin to the AGND. The internal ramp is a triangle at the PWM frequency with a peak voltage of 1.25V and a valley voltage of 0.25V. The approximate operating frequency is determined by the value of an external resistor as shown in Figure 15.

Figure 15. Switching Frequency vs. R<sub>FS</sub>

The operation frequency can be programmed up to 2MHz, but there is a minimum on-time limitation which is around 110ns. Users should take care of minimum limitation on the operating duty cycle under high frequency application.

### Application Information (Cont.)

### **Synchronization Frequency**

Synchronization operation mode is invoked by using an external clock signal and is activated when the SYNC/EN is pulled and held above 2V and held below 0.8V. The range of synchronization frequency is from 200kHz to 2MHz.

A jitter happens when sync pulse clock edge is less than 120ns before the phase switches. It is caused by the ground bounce of synchronization pulse coupled to PWM comparator. Users try to avoid this application. (refer to Figure 9).

#### **Power Good Indicator**

The PGOOD pin is an open-drain and incorporated window comparators output. It's is necessary that a pull-up resistor from the PGOOD pin to the input supply for setting the logic high level of the PGOOD signal. When FB voltage is within  $\pm 10\%$  setting output voltages typical, the output of power good comparator becomes high impedance after delay time. The PGOOD signal delay time is around  $1024/F_{\rm osc}$ . In shutdown mode the power good output is actively pulled low.

For example, 1MHz switching frequency applications, the PGOOD delay time is around 1ms.

#### **Thermal Shutdown**

When the junction temperature rises up around 160°C, the internal soft start voltage is held low, the internal high side and low side MOSFETs are turned off and the output voltage will fall to zero. Once the junction temperature goes below hysteresis temperature around 10°C, the regulator will restart. (refer to Figure 8).

### **Linear Mode Operation (100% duty)**

The SC4620 can allows 100% duty cycle operation. The Vout is.

$$V_{\text{OUT}} = V_{\text{IN}} - (R_{\text{L}} + R_{\text{DSH}}) \times I_{\text{OUT}}$$

where

R<sub>1</sub>: Output inductor DC resistance.

R<sub>DSH</sub>: Internal high side P-MOSFET resistance. (refer to Figure 11).

As Vin drops gradually and close to Vout, the buck regulator will go into 100% duty cycle ratio. A matter needing

attention is internal high side PMOS has minimum off time limitation and is related to duty cycle rate. This condition makes the working duty cycle perform at randon with the output ripple increasing and a poor transient response. Above phenomenon can be improved by larger output capacitor and smaller output inductor. Users need to verify whether above application condition has opposite influence on entire circuit.

#### **Over Current Protection**

A over current setting is programmed by an external resistor ( $R_{\rm ISET}$ ). It goes through internal sense resistor and generates a voltage.

$$V2 = V_{cc} - I \times R_{Onsense}$$

where

I: The current is generated by R<sub>ISET</sub>, and it is amplified by internal current amplifier.

$R_{\text{onsense}}$ : Internal sense resistor.

Output inductor current goes through internal high side P-MOSFET and generate a voltage.

$$V1 = V_{IN} - I_L \times R_{DSH(ON)}$$

where

I<sub>1</sub>: Output inductor current.

$R_{DSH(ON)}$ : High side P-MOSFET conduction resistance.

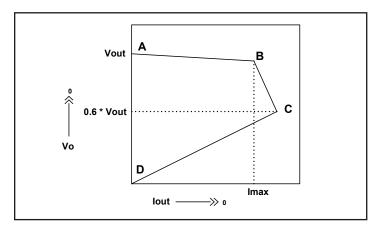

After the high side PMOS turn on around 30ns, the OCP comparator will compare between V2 and V1. When the converter detects an over current condition (V2 > V1) as shown in Figure 16, the SC4620 proceeds into the cycle by cycle protection mode (Point B to Point C), which responds to minor over current cases and the output voltage is monitored.

If the over current and low output voltage (set at 60% of nominal output voltage) occur at the same time, the SS pin is pull low by an internal switch and the comp pin is pulled low and the devices stops switching. Assume start from FB = 0V, FB and SS voltage rise forward 0.5V. Once SS voltage exceeds 0.4V, the hiccup comparator becomes enabled. The hiccup period is around  $2^{17}/F_{\rm osc}$ . (Point C to Point D).

For example, with a switching frequency application of

### Application information (Cont.)

550kHz, the hiccup period is around 238ms. (refer to Figure 7).

A poor layout will make OCP trip point shift and is not easily to calculate by  $R_{\mbox{\tiny ISET}}$ . This is because it is affected by ground bounce, spiker voltage between Vin pin and PH pin, and internal parameter tolerance. Users can refer to Figure 14, it shows how to set maximum output current by  $R_{\mbox{\tiny ISET}}$ .

Figure 16. Over Current Protection Characteristic

#### **Inductor Selection**

For a typical SC4620 application, the inductor selection is mainly based on its value, saturation current and DC resistance. The inductor should be able to handle the peak current without saturating and its copper resistance in the winding should be as low as possible to minimize its resistive power loss.

The inductor value can be determined according to its operating point and the switching frequency as follows:

$$L = \frac{V_{\text{out}} \times (V_{\text{IN}} - V_{\text{out}})}{V_{\text{IN}} \times f_{\text{S}} \times \Lambda I \times I_{\text{omax}}}$$

where

fs = switching frequency.

$\Delta I$  = ratio of the peak to peak inductor current to the maximum output load current.

The peak to peak inductor current is:

$$I_{P-P} = \Delta I \times I_{OMAX}$$

After the required inductor value is selected, the proper selection of the core material is based on the peak inductor current and efficiency requirements. The core must be able to handle the peak inductor current  $I_{\text{PEAK}}$  without saturation and produce low core loss during the high frequency operation and is given as follows:

$$I_{PEAK} = I_{IOMAX} + \frac{I_{P-P}}{2}$$

The power loss for the inductor includes its core loss and copper loss. If possible, the winding resistance should be minimized to reduce any copper loss of the inductor, (the core loss can be found in the manufacturer's datasheet).

The inductor's copper loss can be estimated as follows:

$$P_{\text{COOPER}} = I^2_{\text{LRMS}} \times R_{\text{WINDING}}$$

where

$I_{LRMS}$  is the RMS current in the inductor.

This current can be calculated as follows:

$$I_{LRMS} = I_{OMAX} \times \sqrt{1 + \frac{1}{3}} \times \Delta I^2$$

#### **Output Capacitor Selection**

Basically there are two major factors to consider in selecting the type and quantity of the output capacitors. The first one is the required ESR (Equivalent Series Resistance) which should be low enough to reduce the voltage deviation from its nominal one during its load changes. The second one is the required capacitance, which should be high enough to hold up the output voltage. Before the SC4620 regulates the inductor current to a new value during a load transient, the output capacitor delivers all the additional current needed by the load.

The ESR and ESL of the output capacitor, the loop parasitic inductance between the output capacitor and the load combined with inductor ripple current are all major contributors to the output voltage ripple.

#### **Input Capacitor Selection**

The input capacitor selection is based on its ripple current level, required capacitance and voltage rating. This capacitor must be able to provide the ripple current by the

### Application Information (Cont.)

switching actions. For the continuous conduction mode, the RMS value of the input capacitor can be calculated from:

$$I_{\text{cin(rms)}} = I_{\text{omax}} \times \sqrt{\frac{V_{\text{out}} \times (V_{\text{in}} - V_{\text{out}})}{V_{\text{in}}^{2}}}$$

This current gives the capacitor's power loss as follows:

$$P_{cin} = I_{cin(rms)}^2 \times R_{cin(rsr)}$$

This capacitor's RMS loss can be a significant part of the total loss in the converter and reduces the overall converter er efficiency. The input ripple voltage mainly depends on the input capacitor's ESR and its capacitance for a given load, input voltage and output voltage. Assuming that the input current of the converter is constant, the required input capacitance for a given voltage ripple can be calculated by:

$$C_{\text{IN}} = I_{\text{OMAX}} \times \frac{D \times (1 - D)}{f_{\text{S}} \times (\Delta V_{\text{I}} - I_{\text{OMAX}} \times R_{\text{CIN(ESR)}})}$$

where

$D = V_0/V_1$ , duty ratio.

$\Delta V_{l}$  = the given input voltage ripple.

### **Loop Compensation Design**

For a DC/DC converter, it is usually required that the converter has a loop gain of a high cross-over frequency for fast load response, high DC and low frequency gain for low steady state error, and enough phase margin for its operating stability. Often one can not have all these properties at the same time. The purpose of the loop compensation is to arrange the poles and zeros of the compensation network to meet the requirements for a specific application.

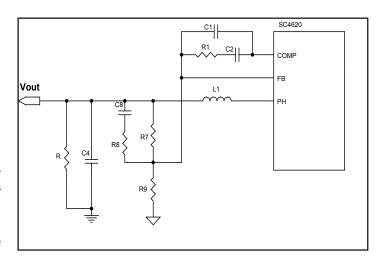

The SC4620 has an internal error amplifier and requires the compensation network to connect among the COMP pin and FB pin, GND, and the output as shown in Figure 17. The compensation network includes C1, C2, R1, R7, R8 and C8. R9 is used to program the output voltage according to:

$$V_{\circ} = 0.5 \times (1 + \frac{R_7}{R_0})$$

Figure 17. Compensation Network Provides 3 Poles and 2 Zeros

For voltage mode step down applications as shown in Figure 17, the power stage transfer function is:

$$G_{VD}(s) = V_1 \frac{1 + \frac{s}{\frac{1}{R_c \cdot C_4}}}{1 + s \frac{L_1}{R} + s^2 L_1 C_4}$$

where

R = load resistance

$R_c = C4$ 's ESR.

The compensation network will have these characteristics:

$$G_{\text{COMP}}\left(s\right) = \frac{\omega_{l}}{s} \cdot \frac{1 + \frac{s}{\omega_{Z1}}}{1 + \frac{s}{\omega_{P1}}} \cdot \frac{1 + \frac{s}{\omega_{Z2}}}{\cdot 1 + \frac{s}{\omega_{P2}}}$$

### Application Information (Cont.)

where

$$\omega_{I} = \frac{1}{R_{7} \cdot (C_{1} + C_{2})}$$

$$\omega_{z_1} = \frac{1}{R_1 \cdot C_2}$$

$$\omega_{Z2} = \frac{1}{(R_7 + R_8) \cdot C_8}$$

$$\omega_{\rm P1} = \frac{C_1 + C_2}{R_1 \cdot C_1 \cdot C_2}$$

$$\omega_{_{\mathrm{P}2}}=\frac{1}{R_{_{8}}\cdot C_{_{8}}}$$

After the compensation, the converter will have the following loop gain:

$$T(s) = G_{PWM} \cdot G_{COMP}(s) \cdot G_{VD}(s)$$

$$=\frac{\frac{1}{V_{M}}\cdot\omega_{l}\cdot V_{l}}{s}\cdot\frac{1+\frac{s}{\omega_{z1}}}{1+\frac{s}{\omega_{p_{1}}}}\cdot\frac{1+\frac{s}{\omega_{z2}}}{\cdot1+\frac{s}{\omega_{p_{2}}}}\cdot\frac{1+\frac{s}{\frac{1}{R_{C}\cdot C_{4}}}}{1+s\frac{L_{1}}{R}+s^{2}L_{1}C}$$

where

$G_{PWM} = PWM gain.$

$V_{\rm M} = 1.0V$ , ramp peak to valley voltage of SC4620.

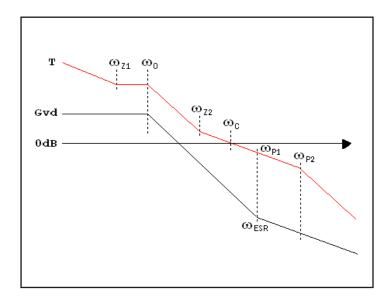

The design guidelines for the SC4620 applications are as follows:

- 1. Set the loop gain crossover corner frequency  $\omega_c$  for given switching corner frequency  $\omega_s$  =  $2\pi fs$ ,

- 2. Place an integrator at the origin to increase DC and low frequency gains.

- 3. Select  $\omega_{\rm Z1}$  and  $\omega_{\rm Z2}$  such that they are placed near  $\omega_{\rm 0}$  to damp the peaking and the loop gain has a -20dB/dec rate to go across the OdB line for obtaining a wide bandwidth.

- 4. Cancel the zero from C4's ESR by a compensator pole  $\omega_{\text{P4}}$  ( $\omega_{\text{P4}} = \omega_{\text{ESP}} = 1/(R_{\text{C}}C_{\text{A}})$ ).

- $\omega_{P1}$  ( $\omega_{P1} = \omega_{ESR} = 1/(R_{c}C_{4})$ ). 5. Place a high frequency compensator pole  $\omega_{P2}$  ( $\omega_{P2} = \pi fs$ ) to get the maximum attenuation of the switching ripple and high frequency noise with the adequate phase lag at  $\omega_{c}$ .

The compensated loop gain will be as given as show in Figure 18.

Figure 18. Asymptotic Diagrams of Power Stage and Loop Gain

### Application Information (Cont.)

#### **Layout Guidelines**

In order to achieve optimal thermal and noise immunity for high frequency converters, special attention must be paid to the PCB layout. The goal of layout optimization is to minimize the high di/dt loops and reduce ground bounce.

Output voltage setting, line regulation, stability, switching frequency and OCP trip point shifted are affected by a poor layout. The following guidelines should be used to ensure proper functions of the converters.

- 1. Both Power ground (PGND) and signal ground (AGND) are separated.

- 2. A ground plane is recommended to minimize noise and copper losses, and maximize heat dissipation.

- Start the PCB layout by placing the power components first. Arrange the power circuit to achieve a clean power flow route.

- 4. Minimize all high di/dt loops. These loops pass high di/dt current. Make sure the trace width is wide enough to reduce copper losses in this loop. Ground bounce happen to magnetic flux changed and it is proportional to a magnetic filed which goes through high di/dt loops.

- 5. The input ceramic capacitor ( $C_{IN}$ ) should be close to  $PV_{IN}$  pins and PGND pins.

- 6. Both input ceramic capacitor gnd and output ceramic capacitor gnd are at same port.

- 7. A RC snubber circuit between PV<sub>IN</sub> and PH pins is helpful for stability operation. Be careful with power derating of snubber circuit.

- 8. The  $\rm V_{\rm cc}$  bypass capacitor should be placed next to the  $\rm V_{\rm cc}$  and AGND pins.

- 9. The OCP setting resistor ( $R_{\rm ISET}$ ) and filter capacitor ( $C_{\rm ISET}$ ) should be placed next to the ISET and AGND pins.

- Feedback divider connects to output connector by Kelvin connection and far away from the noise sources such as switching node and switching components.

- 11. A multilayer chip beads between AGND and PGND will reduce the ground bounce injected to the "quiet" circuit. It's helpful for stability operation.

- 12. A large copper area underneath the SC4624 IC is necessary for heat sinking purpose. And multiple layers of large copper area connected through vias can be used for better thermal performance. The size of the vias as the connection between multiple layers should not be too large or solder may seep through

the big vias to the bottom layer during the re-flow process.

# Application Information (Cont.)

$5V_{_{\mathrm{IN}}}$ ,  $1V_{_{\mathrm{OUT}}}$ , 2.5A, all ceramic capacitors ( application circuit #1 )

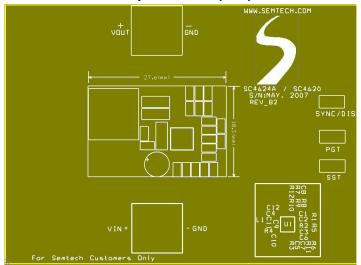

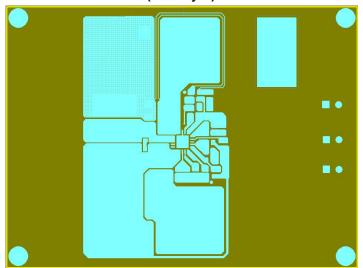

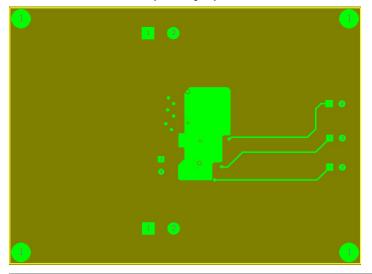

## **PCB** Layout

## Component Side (TOP)

(TOP layer)

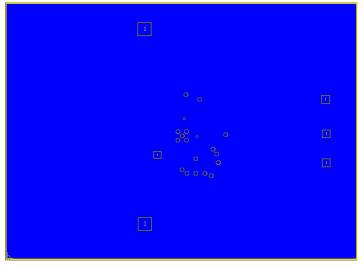

(Bottom layer)

(IN2 layer)

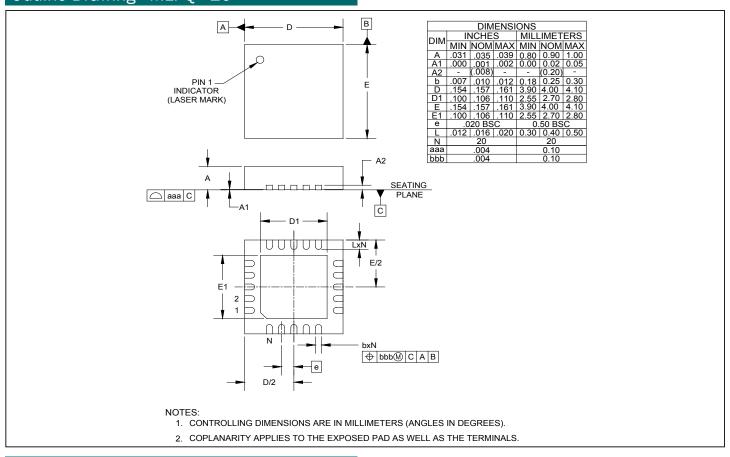

## Outline Drawing - MLPQ - 20

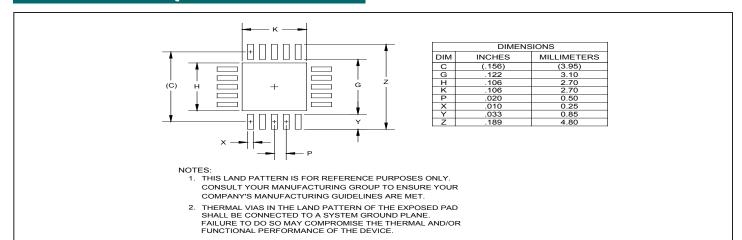

### Land Pattern - MLPQ - 20

### **Contact Information**

Semtech Corporation

Power Management Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com