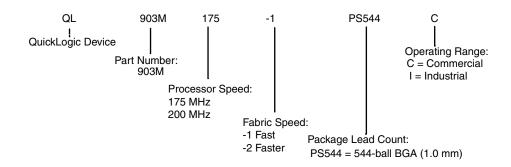

# QL903M QuickMIPS™ Data Sheet

# QuickMIPS Embedded Standard Product (ESP) Family

# **Device Highlights CPU Core**

- 32-bit MIPS 4Kc processor runs up to 200 MHz (260 Dhrystone MIPS)

- 1.3 Dhrystone MIPS per MHz

- MDU supports MAC instructions for DSP functions

- 16 KB of instruction cache (4-way set associative)

- 16 KB of data cache (4-way set associative), lockable on a per line basis

# **SDRAM Memory Controller**

- Support for PC-100 type SDRAMs, up to 256 MB total

- Two chip selects

- · Operates at up to one-half CPU pipeline speed

- Support for x16 and x32 external memory bus configurations

# I/O Peripheral Controller

- Direct support for SRAM, EPROM and Flash

- 8-bit, 16-bit and 32-bit device widths supported

- Eight independent chip selects

#### **PCI Controller**

- 32-bit v2.2 compatible

- Up to 66 MHz operation

- Supports host and satellite configurations

- Dedicated DMA channels for transmit and receive bus transactions

- Support for external bus master arbitration (through FPGA library provided by QuickLogic)

# **Two Ethernet Controllers**

- Two 10/100 MACs

- Provides MII connection to external transceivers/devices

#### **Two UARTs**

- One with modem control signals

- Both with IRDA-compliant signals

# Four General Purpose 16-bit Timer/Counters

- 16-bit prescaler to increase timer/counter delay

- Four modes of operation: decrement, increment, interval, and Pulse Width Modulation (PWM)

- Operation from the System Bus clock or a clock source supplied from the Programmable Fabric

# **System SRAM**

16 KB accessible by all System Bus masters or the Programmable Fabric

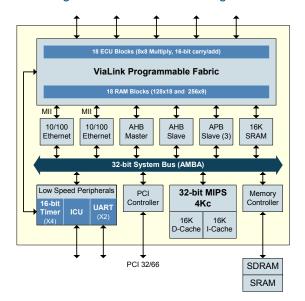

Figure 1: QL903M Block Diagram

# **High Performance 32-bit System Bus (AMBA Bus)**

- Operates at one-half, one-third, or one-fourth of CPU pipeline speed

- One 32-bit AHB master port/one 32-bit AHB slave port to programmable Fabric

- Three 32-bit APB slave ports in the programmable Fabric

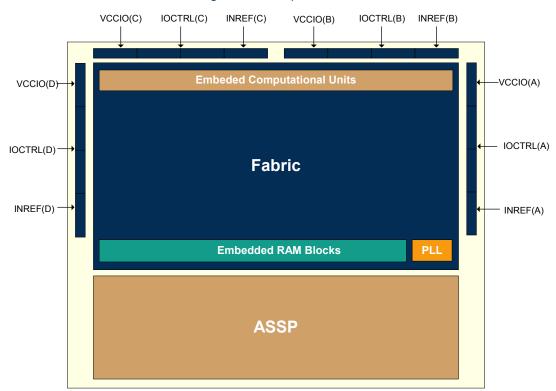

# Flexible Programmable Fabric

- 1152 logic cells (316 K system gates)

- 124 I/O pins

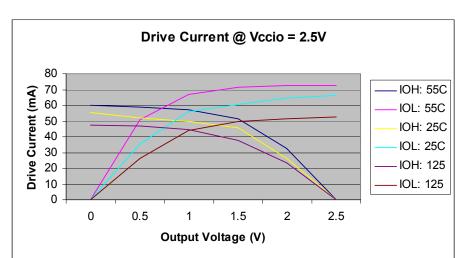

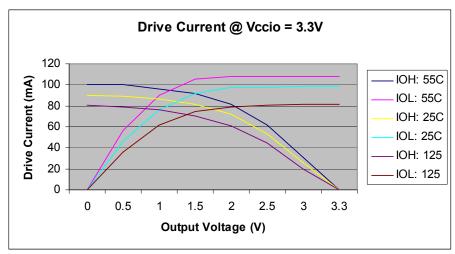

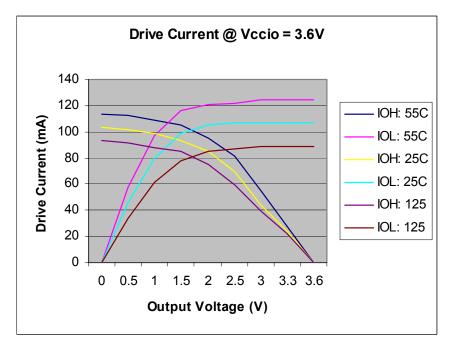

- 1.95 V Vcc, 1.8/2.5/3.3 V drive capable I/O

- 2,510 dedicated flip-flops

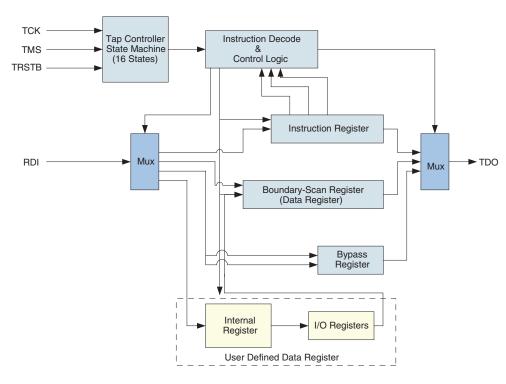

- IEEE 1149.1 boundary scan testing compliant

#### **Dual-Port SRAM Modules**

- Eighteen 2,304 bit Dual-Port High Performance SRAM Blocks

- 41,472 embedded RAM bits

- RAM/ROM/FIFO Wizard for automatic configuration

- Configurable and cascadable

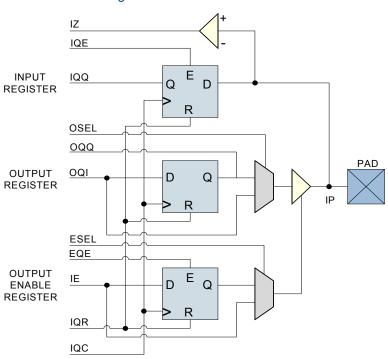

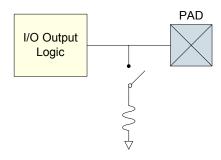

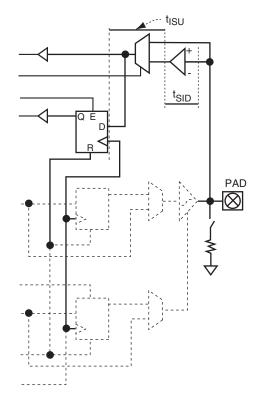

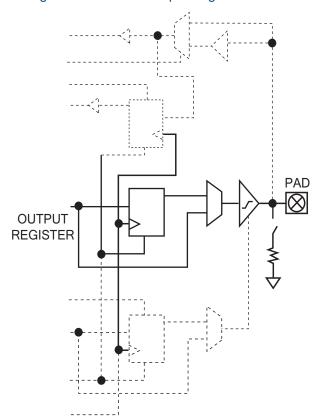

# Programmable I/O

- High performance I/O cell with fast clock-to-out time

- Programmable Slew Rate Control

- Programmable I/O Standards:

- LVTTL, LVCMOS, LVCMOS18, PCI, GTL+, SSTL2, and SSTL3

- Independent I/O Banks capable of supporting multiple standards in one device

- ▶ I/O Register Configurations: Input, Output, Output Enable (OE)

#### Advanced Clock Network

- Multiple dedicated Low Skew Clock Networks

- High drive input-only networks

- Quadrant-based segmentable clock networks

- User-programmable Phase Locked Loop (PLL) circuit

# **Embedded Computational Units (ECUs)**

Eighteen hardwired DSP building blocks with integrated Multiply, Add, and Accumulate functions.

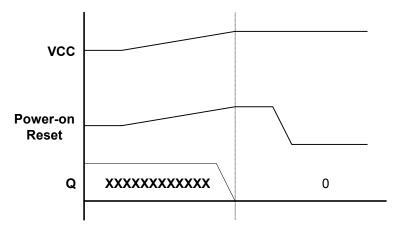

# **Security Features**

The QuickLogic products come with secure ViaLink® technology that protects intellectual property from design theft and reverse engineering. No external configuration memory is needed for the Fabric. The device is instant-on at power-up.

# **QuickWorks Design Software**

The QuickWorks® package provides the most complete ESP and Field Programmable Gate Array (FPGA) software solution from design entry to logic synthesis, to place and route, and simulation. The package provides a solution for designers who use third party tools from Cadence, Mentor, Synopsys, and other third-party tools for design entry, synthesis, or simulation.

#### **Process Data**

The QL903M is fabricated on a  $0.18\,\mu$ , six layer metal CMOS process. The core voltage is  $1.95\,V\,V_{CC}$  supply and the I/Os are up to  $3.3\,V$  compliant. The QL903M is available in commercial and industrial temperature grades.

# QL903M Architectural Overview

The QL903M chip can be thought of as having two distinct sides, an Application Specific Standard Product (ASSP) side and a Programmable Fabric side. The ASSP side contains the standard cell circuitry of the device such as the MIPS 4Kc CPU and the Ethernet MACs, and the Fabric side contains all of the programmable logic elements (e.g., logic cells and dual-port RAMs) of the device.

#### **ASSP Side**

This section discusses the various circuits in the ASSP portion of the QL903M device.

#### **CPU Core**

The MIPS32 4Kc processor core is a high-performance, low-power, 32-bit MIPS RISC core capable of speeds up to 200 MHz. The 4Kc core contains a fully-associative translation lookaside buffer (TLB) based Memory Management Unit (MMU) and a pipelined MDU.

The core executes the MIPS32 instruction set architecture (ISA). It supports all application code in the MIPS I, II, III, and IV instruction sets. It also supports kernel code for the R4000 processor and above. The MIPS32 ISA contains special multiply-accumulate, conditional move, prefetch, wait, and zero/one detect instructions. The MMU contains a three-entry instruction TLB (ITLB), a three-entry data TLB (DTLB), and a 16 dual-entry joint TLB (JTLB) with variable page sizes.

The 4Kc multiply-divide unit (MDU) supports a maximum issue rate of one 32x16 multiply (MUL/MULT/MULTU), multiply-add (MADD/MADDU), or multiply-subtract (MSUB/MSUBU) operation per clock, or one 32x32 MUL, MADD, or MSUB every other clock.

#### **Instruction and Data Caches**

The instruction and data caches are both 16 Kbytes in size. Each cache is organized as four-way set associative. The data cache has lockout capability per cache line. On a cache miss, loads are blocked only until the first critical word becomes available. The pipeline resumes execution while the remaining words are being written to the cache. Both caches are virtually indexed and physically tagged. Virtual indexing allows the cache to be indexed in the same clock in which the address is generated rather than waiting for the virtual-to physical address translation in the MMU.

#### **EJTAG Interface**

The basic Enhanced JTAG (EJTAG) features provide CPU run control with stop, single stepping and re-start, and software breakpoints through the SDBBP instruction. In addition, instruction and data virtual address hardware breakpoints, and connection to an external EJTAG probe through the Test Access Port (TAP) is included.

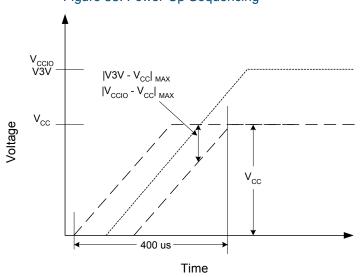

#### **ASSP PLL**

On the ASSP side of the QL903M there is a single clock input that provides an input clock reference for the MIPS core, the System Bus, and all ASSP peripherals (other than the PCI Controller, which is independently driven by the PCI\_CLK input). This clock input (CPU\_PLL\_CLKIN) is the input to a PLL that is fixed at an 8 times clock multiplication rate. For example, if the clock rate applied to CPU\_PLL\_CLKIN is 25 MHz, the resultant clock that drives the MIPS core is 200 MHz. **Table 1** shows the maximum input clock rates for CPU\_PLL\_CLKIN based upon the ASSP speed grade of the given QL903M device.

Table 1: Maximum Input Frequency for CPU\_PLL\_CLKIN and MIPS Core Frequency

Based on QL903M ASSP Speed Grade

| QuickMIPS Device<br>Part Number Prefix | Maximum Input Frequency for CPU_PLL_CLKIN | Resultant Maximum<br>MIPS Core Frequency |  |

|----------------------------------------|-------------------------------------------|------------------------------------------|--|

| QL903M175                              | 21.875 MHz                                | 175 MHz                                  |  |

| QL903M200                              | 25.000 MHz                                | 200 MHz                                  |  |

The System Bus clock can run at a maximum rate of one-half the MIPS core clock frequency. Other ratios (one-third and one-fourth) are also possible and controlled by the CPU\_PLL\_DIV(1) and CPU\_PLL\_DIV(0) inputs as shown in **Table 2**.

Table 2: MIPS Core Clock Rate to System Bus Clock Rate (hclk) Ratio Based on CPU\_PLL\_DIV(1) and CPU\_PLL\_DIV(0) Signals

| CPU_PLL_DIV(1) | CPU_PLL_DIV(0) | Ratio<br>MIPS Core Clock Rate :<br>System Bus Clock Rate (hclk) | System Bus Clock<br>(hclk) Duty Cycle |

|----------------|----------------|-----------------------------------------------------------------|---------------------------------------|

| 0              | X              | 2:1                                                             | 50%                                   |

| 1              | 1              | 3:1                                                             | 33% <sup>a</sup>                      |

| 1              | 0              | 4:1                                                             | 50%                                   |

a. In 3:1 mode, the System bus clock duty cycle is not symmetric. This affects the internal System Bus clock as well as hclk and the SDRAM clock source (SD\_CLKOUT). Therefore, care must be taken so that minimum clock pulse widths are not violated when these clock signals are used to drive externally connected devices.

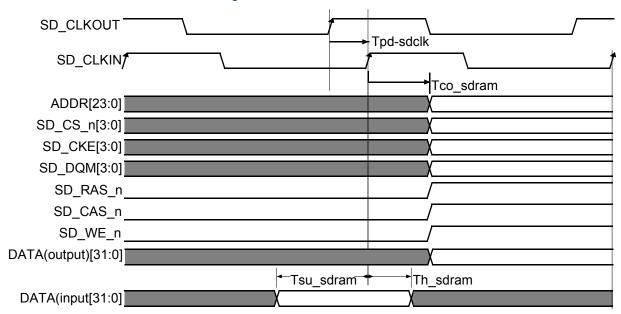

# **SDRAM Memory Controller**

The QL903M SDRAM Memory Controller (SDMC) provides all the necessary logic to connect to a wide variety of industry standard SDRAMs for use by the CPU, Ethernet Controllers, PCI Controller, and Programmable Fabric. The SDMC supports a minimum SDRAM size of 16 Mbytes and a maximum SDRAM size of 256 Mbytes.

The SDRAM Controller controls the SDRAM on the external bus. On receiving an access request, the SDRAM Controller decides on the appropriate commands to send to the SDRAM memory. The DRAM Bank Controller sequences all of the commands required to complete a read or write request to an SDRAM memory location with timing controlled by the CAS Delay and RAS Delay values.

The bus interface is a slave on the System Bus; it contains the control register block. The bus interface produces read, write, refresh and mode register write requests to the SDRAM control engine, and software supplied configuration information.

Data is transferred to and from the SDRAM as unbroken quad words. This data packet size is convenient for cache line fills and buffered writes. For accesses smaller than a quad word, extra read data is ignored by the SDRAM Controller; for writes, the SD\_DQM(3:0) pins are used to force the SDRAMs to ignore invalid data. For access sizes larger than a quad word, multiple quad word accesses are issued to the SDRAM control engine.

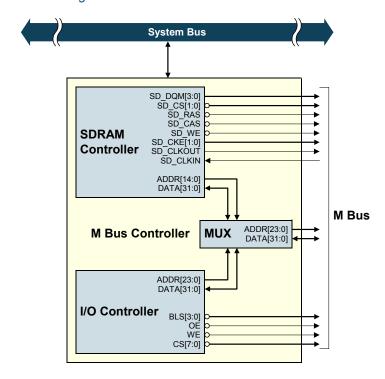

# I/O Peripheral Controller

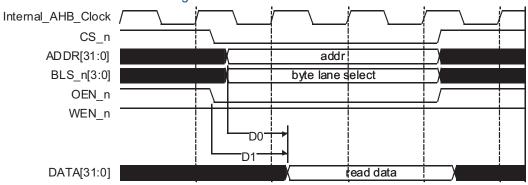

This section describes access to I/O and memory devices on the external M Bus (with the exception of SDRAM). The I/O Peripheral Controller (**Figure 2**) generates strobes and signals that can be used to interface the M Bus with common asynchronous peripheral devices.

The QL903M Peripheral Controller Unit (PCU) provides decoded strobe signals to control external peripherals such as SRAM, flash, real time clock (RTC) and memory mapped I/O devices. It supports 8-bit, 16-bit, and 32-bit widths with programmable wait states and bus turnaround time based on memory speed. The PCU provides the following functionality:

- Decoding of memory access in the local CPUs memory map to generate chip selects or strobes.

- Control of wait states for decoded regions. A total of eight chip select signals are available. Chip select seven is used as the boot ROM chip select.

The M Bus is a shared resource between the SDRAM Controller and I/O Controller. The M Bus is assigned to one of these two controllers by an internal arbiter. There is one turn-around cycle when switching from one controller to the other.

Figure 2: SDRAM and I/O Controllers

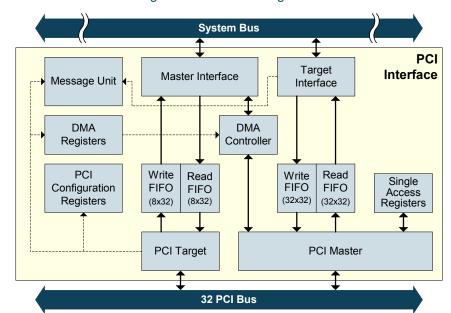

#### **PCI Controller**

The QuickMIPS PCI Interface is a 32-bit, 66 MHz, Revision 2.2 compliant interface as specified by the PCI Local Bus Specification. This section provides a detailed description of the PCI Controller functionality.

**Figure 3** shows a simplified block diagram of the PCI Controller. The PCI Controller is a bridge between the on-chip System Bus and the external PCI bus. There are two main modes of operation of the PCI function, each utilizing several resources:

- PCI Target

- PCI Target access to System Address Space

- PCI Target to PCI configuration registers

- PCI Target to extended registers (DMA and message/mailbox)

- PCI Master

- System Address Space to PCI access

- System-to-PCI and PCI-to-System DMA

- PCI master read/write generated through the single access register

Figure 3: PCI Block Diagram

The PCI Controller can be used as a system host or as a secondary master:

- System Host: The QL903M PCI interface is connected to the root PCI bus segment (Bus 0) and the onchip CPU performs bus enumeration to determine how all PCI Base Address Registers are configured. The SDRAM controlled by the QL903M is used as the main memory.

- The Single Access Controller can be used for performing enumeration upon system boot, and then to perform I/O operations to I/O mapped PCI devices.

- The System Bus to PCI Memory Aperture can be used by host drivers to control memory mapped PCI devices (PIO).

- The DMA Controller provides the most efficient way to transfer large blocks of data between system memory and external PCI target devices (such as video controllers, etc.).

- Secondary Master: The QL903M is enumerated by an external PCI host CPU.

- The PCI configuration registers of the QL903M are recognized by the host CPU and enumerated accordingly.

- The DMA Controller can be used to efficiently move data between local QL903M-controlled SDRAM and the host memory.

- The Single Access Controller can be used to transfer small amounts of data in and out of the host memory space.

- The message unit can be used as an inter-CPU communication mechanism for a host driver to synchronize with a local driver running on the QL903M CPU.

- The PCI to local System Bus aperture can be used to allow the host CPU or other PCI agent to access QL903M memory directly.

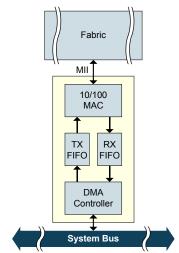

#### **Ethernet Controllers**

The QL903M has two Ethernet Media Access Controllers (MACs) embedded in the ASSP portion of the device. The Ethernet Controllers incorporate the essential protocol requirements for operation of Ethernet/IEEE 802.3 compliant nodes, and provide interfaces between the host subsystem and the Media Independent Interface (MII). Each 10/100 MAC can operate in 10 Mbps or 100 Mbps mode based on the transmit and receive clocks provided (2.5/25 MHz). The controllers contain transmit and receive FIFOs and embedded DMA control. **Figure 4** shows a block diagram of the QL903M Ethernet Controller.

Figure 4: Ethernet Controller Block Diagram

The DMA Controller is responsible for exchanging data between the FIFOs and the system memory. DMA operation is controllable through a set of control and status registers.

Each 10/100 MAC operates in half-duplex mode and full-duplex modes. When operating in the half-duplex mode, the 10/100 MAC core is fully compliant to Section 4 of ISO/IEC 8802-3 (ANSI/IEEE Standard) and ANSI/IEEE 802.3. When operating in the full-duplex mode, the 10/100 MAC core is compliant to the IEEE 802.3x standard for full-duplex operations. Each 10/100 MAC is also compatible with Home PNA 1.1.

The 10/100 MAC core provides programmable enhanced features designed to minimize host supervision, bus utilization, and pre- or post-message processing. These features include the ability to disable retires after a collision, dynamic FCS generation on a frame-by-frame basis, automatic pad field insertion and deletion to enforce minimum frame size attributes, automatic retransmission and detection of collision frames.

The 10/100 MAC core can sustain transmission or reception of minimal-sized back-to-back packets at full line speed with an inter-packet gap (IPG) of 9.6  $\mu$ s for 10-Mb/s and 0.96  $\mu$ s for 100-Mb/s.

Data to/from the MAC is buffered in transmit/receive FIFOs. In the case of data received by the Ethernet MAC, the data is drained from the receive FIFO by the DMA Controller and stored to the specified target (typically the data is stored in SDRAM). For Ethernet transmit, the DMA Controller reads data from memory (SDRAM typically) and pushes it into the transmit FIFO. DMA operation is controllable through a set of control and status registers.

With the exception of the M1\_RXCLK, M2\_RXCLK, M1\_TXCLK and M2\_TXCLK signals, the MII interface is located on the ASSP/Fabric boundary internal to the device. If the designer wants to use one or both of the Ethernet MACs, the signal ports on this interface must be brought out to Fabric IO pins in the top-level Fabric design. **Table 3** shows the recommended Fabric IO pin locations for the MII interface pins.

Table 3: MII Interface Signals and Recommended Fabric IO Pin Locations

| MII Interface Signal | MII Interface<br>Direction <sup>a</sup> | Fabric Pin Signal    | Fabric Pin Type | Fabric Pin Location |

|----------------------|-----------------------------------------|----------------------|-----------------|---------------------|

| M1_COL               | I                                       | M1_COL               | I               | F1                  |

| M1_CRS               | I                                       | M1_CRS               | I               | G2                  |

| M1_MDC               | 0                                       | M1_MDC               | 0               | F3                  |

| M1_MDI               | I                                       |                      |                 |                     |

| M1_MDO               | 0                                       | M1_MDIO <sup>b</sup> | I/O/Z           | K4                  |

| M1_MDO_EN_N          | 0                                       |                      |                 |                     |

| M1_RXD(0)            | I                                       | M1_RXD(0)            | I               | F2                  |

| M1_RXD(1)            | I                                       | M1_RXD(1)            | I               | E1                  |

| M1_RXD(2)            | I                                       | M1_RXD(2)            | I               | E2                  |

| M1_RXD(3)            | I                                       | M1_RXD(3)            | I               | D1                  |

| M1_RXDV              | I                                       | M1_RXDV              | I               | L4                  |

| M1_RXER              | I                                       | M1_RXER              | I               | D2                  |

| M1_TXD(0)            | 0                                       | M1_TXD(0)            | 0               | L3                  |

| M1_TXD(1)            | 0                                       | M1_TXD(1)            | 0               | C1                  |

| M1_TXD(2)            | 0                                       | M1_TXD(2)            | 0               | L5                  |

| M1_TXD(3)            | 0                                       | M1_TXD(3)            | 0               | B1                  |

| M1_TXEN              | 0                                       | M1_TXEN              | 0               | E3                  |

| M2_COL               | I                                       | M2_COL               | I               | K22                 |

| M2_CRS               | I                                       | M2_CRS               | I               | L24                 |

| M2_MDC               | 0                                       | M2_MDC               | 0               | C25                 |

| M2_MDI               | I                                       |                      |                 |                     |

| M2_MDO               | 0                                       | M2_MDIO <sup>b</sup> | I/O/Z           | E25                 |

| M2_MDO_EN_N          | 0                                       |                      |                 |                     |

| M2_RXD(0)            | I                                       | M2_RXD(0)            | I               | B26                 |

| M2_RXD(1)            | I                                       | M2_RXD(1)            | I               | L23                 |

| M2_RXD(2)            | 1                                       | M2_RXD(2)            | I               | E24                 |

| M2_RXD(3)            | I                                       | M2_RXD(3)            | I               | C24                 |

| M2_RXDV              | I                                       | M2_RXDV              | I               | F24                 |

| M2_RXER              | I                                       | M2_RXER              | I               | L22                 |

| M2_TXD(0)            | 0                                       | M2_TXD(0)            | 0               | M24                 |

| M2_TXD(1)            | 0                                       | M2_TXD(1)            | 0               | C26                 |

| M2_TXD(2)            | 0                                       | M2_TXD(2)            | 0               | M23                 |

| M2_TXD(3)            | 0                                       | M2_TXD(3)            | 0               | D26                 |

| M2_TXEN              | 0                                       | M2_TXEN              | 0               | M22                 |

a. MII Interface direction is specified with respect to the ASSP portion of the device. I designates an input to the ASSP and O designates an output from the ASSP.

b. The M1\_MDIO and M2\_MDIO signals require the instantiation of a bipad\_25um macro. See **Figure 5** for more details.

The pin assignments in **Table 3** represent connections to IO banks A and D of the Fabric. If the Ethernet MACs are connected in this fashion, these two banks must be configured for 3.3 V operation. See **Table 17** for more details.

As **Table 3** indicates, the Mn\_MDIO pin is bi-directional. The signal on this pin is made up of three MII interface signals. Mn\_MDI and Mn\_MDO are the data input and output signals respectively, and Mn\_MDO\_EN\_N is the tri-state buffer enable signal that turns on the pin output driver. Mn\_MDO\_EN\_N is active low, and must be made active high by running it through a logic cell inverter before connecting it to the bipad 25um macro. **Figure 5** shows how these connections are made to the bipad 25um macro.

Connect to inverted copy of Mn\_MDO\_EN\_N EN

Connect to Mn\_MDO A

Connect to Mn\_MDI Q

Mn\_MDI Q

Figure 5: bipad 25um Macro and Connections to MII Interface Signals

The remainder of the MII signals are simple inputs or outputs and can be connected to the Fabric IO pins directly without the instantiation of any specific macros.

# **System SRAM**

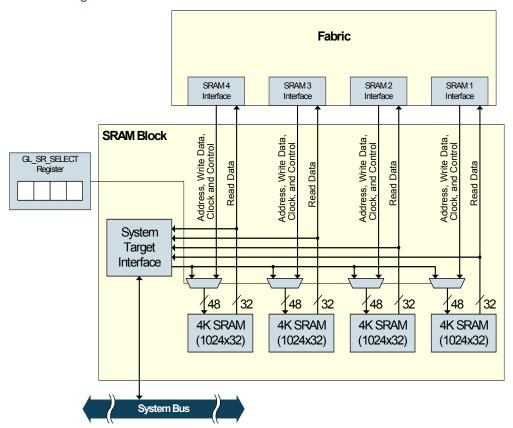

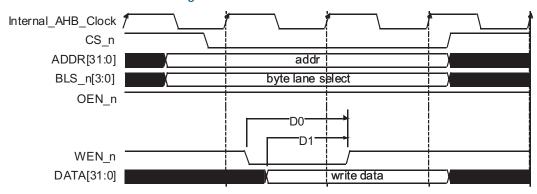

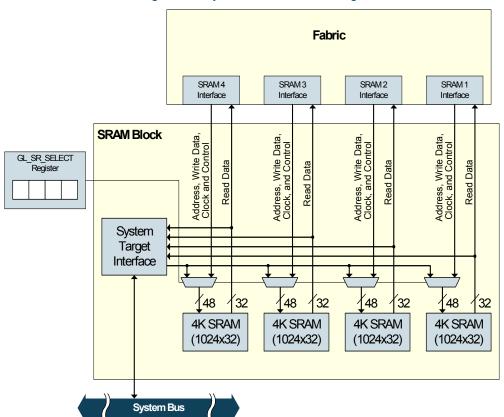

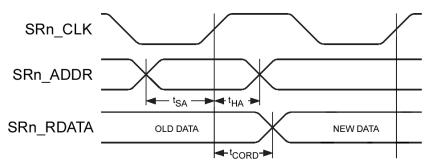

The QL903M contains 16 K bytes of SRAM internal to the ASSP portion of the device. This SRAM is divided into four equal sections of 4 KB each (each arranged as 32-bit x 1024 words), and each section can be configured to be connected to the System Bus (specifically, AHB) or connected to the Fabric directly.

When connected to the AHB, the SRAM (an AHB slave) can be accessed by any AHB master. Furthermore, the 4Kc core can use this internal SRAM for data or instruction storage. The SRAM supports 32-bit, 16-bit, or single byte accesses.

When connected to the Fabric, the SRAM can be accessed directly by any Fabric design without suffering the overhead of accessing it through the AHB interface. In addition, the Fabric has a master AHB interface, which it may also use to access the SRAM. However, in some high-speed applications, it may be necessary for the Fabric to have exclusive access to the SRAM memory. The Fabric interface of the SRAM block facilitates this function, and is described below. **Figure 6** shows the connection scheme of the four memory banks between the Fabric and the AHB.

Figure 6: SRAM Connection Scheme between the Fabric and AHB

Each SRAM block is single ported, and is connected to the Fabric or AHB through a selection MUX. For each SRAM block, the address bus, control signals, clock, and data write bus are all multiplexed by a register bit that is accessible through the System Bus. Therefore, any AHB master may control the switch of a given SRAM block between the AHB and the Fabric interface.

Because each SRAM clock is also switched by the selection MUX, it is possible for the Fabric to drive each SRAM block with a separate clock. However, when an SRAM block is connected to the AHB interface, the System Bus clock (hclk) is always used to drive the block.

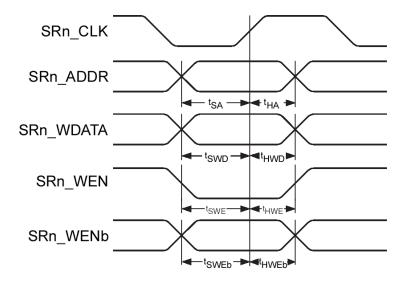

Refer to Table 51 for descriptions of all the System SRAM signals that interface to the Fabric.

# **Interrupt Controller**

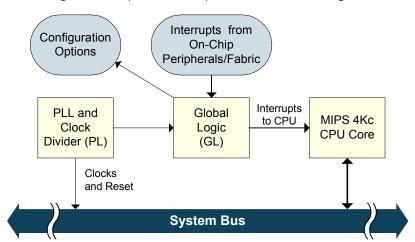

This section describes the function of the QL903M Interrupt Controller Unit (ICU). **Figure 7** shows a block diagram of the Interrupt Controller.

Figure 7: Simplified Interrupt Controller Block Diagram

The QL903M has 9 on-chip peripheral interrupts and 7 external interrupts (including on NMI), for a total of 16 interrupt sources. These 16 interrupt sources are combined into 7 interrupts by the interrupt controller and fed to the CPU core.

External interrupts must be asserted for at least two clock periods in order to be recognized as an interrupt. All interrupts are level triggered.

Each interrupt has an Emulation Enable Register bit and an Emulation Interrupt Value Register bit in the Interrupt Controller. The primary use for the Emulation registers is for testing purposes. The interrupt enable bits are stored in the GL\_EMUL\_EN register. The emulation interrupt value for each possible interrupt is stored in the GL\_INT\_EMUL register.

Each interrupt has an enable bit in the Global Individual Interrupt Enable (GL\_IND\_INT\_EN) register in the Interrupt Controller. Each interrupt also has a status bit in the Global Individual Interrupt Status (GL\_IND\_INT\_STATUS) register in the Interrupt Controller.

The Global CPU Interrupt Enable register (GL\_CPU\_INT\_EN) enables masking of the interrupt groups after they have been grouped together.

The Interrupt Controller has no programmability for priority. That is, there is no hardware priority encoder. Priority is provided as a function of software.

# **High Performance 32-Bit System Bus (AMBA Bus)**

The purpose of this section is to describe the AMBA<sup>1</sup> bus operation for the purposes of implementing user circuits in the Programmable Fabric. All circuits in the ASSP portion of the QL903M chip communicate with the Programmable Fabric primarily through the AMBA bus interfaces (Advanced Microcontroller Bus Architecture from ARM). Circuits implemented in the Programmable Fabric must be designed according to the AMBA Specification, Revision 2.0. The devices within the QL903M are interconnected through the Advanced High-performance Bus (AHB) or the Advanced Peripheral Bus (APB). Refer to the AMBA Specification, Revision 2.0, for more detailed information about the AHB and APB.

#### **Advanced High-Performance Bus (AHB)**

The AHB is the high-performance variant of the AMBA specification. It supports multiple bus masters and provides high bandwidth operation. The AHB implementation in the QL903M is 32 bits wide. All signals are synchronous to the rising clock edge of the bus clock (hclk).

The key features of the QL903M AHB include:

- Burst transfers

- Single-cycle bus master handover

- 32-bit bus runs at up to half the CPU clock frequency

- Multiple bus masters

- Arbitration through an AHB arbiter

- Address decoding through an AHB decoder

**Table 4** lists the master and slave devices that connect to the AHB.

AHB Masters

MIPS 4Kc CPU

System SRAM

PCI

Ethernet Controller 1

Ethernet Controller 2

32-bit Master Interface to Programmable Fabric

SDRAM and I/O Peripheral Controllers

Interrupt Controller

AHB to APB Bridge

Table 4: Master and Slave Devices on the AHB

The QL903M AHB supports multiple bus masters as well as bus slaves. Only one bus master can use the bus at a given time. The bus master provides address and control information when performing read and write operations. In response to the read or write operation from the bus master within a given address range, a bus slave provides information regarding the status of the data transfer (success, failure, or wait). The AHB arbiter ensures that only one bus master is initiating data transfers. The AHB decoder decodes the address of each transfer and provides a select signal for the slave that is involved in the transfer.

1. AMBA is a trademark of ARM Ltd.

#### **AHB Arbitration**

The internal arbiter of the QL903M provides either fixed arbitration priority or round robin rotating priority. Preemption occurs only after a burst of four. Consequently, when a low priority master is in control of the bus and a higher priority master requests access, the lower priority device will lose its grant after a burst of four before another master takes control. This minimizes the loss of performance that happens when bursts are preempted.

This preemption only happens when the designated AHB master is performing bursts of undefined lengths. If the AHB master is performing a burst of a defined (fixed) length, the burst will complete without interruption by the arbiter.

The ARB\_FAIR\_EN bit in the GL\_INT\_EMUL register determines the priority scheme.

When fixed priority is chosen, the priority of AHB masters is as follows (highest to lowest):

- 1. MIPS 4Kc CPU

- 2. Ethernet Controller 1

- 3. Ethernet Controller 2

- **4.** PCI Controller

- 5. Programmable Fabric

#### **Advanced Peripheral Bus (APB)**

The APB is a simplified bus that is ideal for implementing device control registers and other non-burst transfers. The APB is a 32-bit wide bus that runs at the same frequency as AHB. The APB only accommodates slaves, does not support burst transfers, and does not support advanced slave response operations such as retries or wait state insertion. The APB on the QL903M is supported through an AHB-to-APB bridge. Three separately decoded APB regions are available for APB devices implemented in the Fabric. **Table 5** lists the slave devices on the APB.

Table 5: Slave Devices on the APB

| APB Slaves                                           |

|------------------------------------------------------|

| Two UARTs                                            |

| Four 16-bit Timers/Counters                          |

| Three 32-bit slave interfaces to Programmable Fabric |

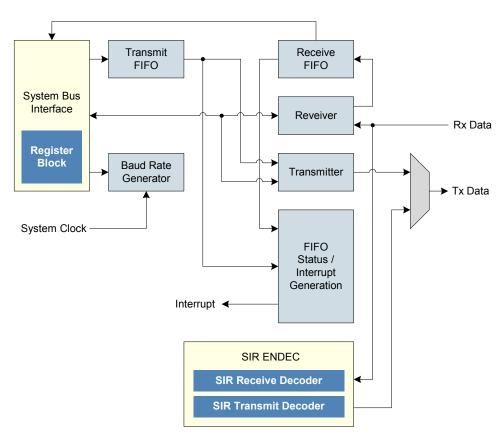

#### **UARTs**

The QL903M chip contains two UARTs. Each UART provides a full-duplex asynchronous receiver and transmitter and has programmable Baud rates. The UARTs contain an IrDA Serial Infrared (SIR) Encoder/Decoder (ENDEC). One UART also has modem control signals. The serial output is software selectable between IrDA and generic serial modes. **Figure 8** shows a block diagram of the UART.

Figure 8: UART Block Diagram

The key features of the UARTs are as follows:

- Programmable Baud rate generation of up to 1/16 System Bus clock rate

- FIFO enable or disable

- 5, 6, 7, or 8 data bits

- 1 or 2 stop bits

- Odd and even, stick or no parity

- Parity, framing, and overrun error detection

- Line break generation and detection

- Loopback

- Interrupt generation

- IrDA SIR ENDEC block providing:

- Programmable use of IrDA SIR or UART input/output

- Support of IrDA SIR ENDEC functions for data rates up to 115.2 kilobits/second half-duplex

- ▶ Support of normal 3/16 and low-power (1.41 to 2.23µs) bit durations

- Programmable internal clock generator allowing division of reference clock by 1 to 512 for low-power mode bit duration

The System Bus (APB interface) generates read and write decodes for accesses to status/control registers and transmit/receive FIFO memories. The Register Block stores data written or to be read across the APB interface. The Baud Rate Generator contains free-running counters that generate a clock that is 16 times the transmit/receive bit rate.

The transmit FIFO is an 8-bit wide, 16-entry deep FIFO memory buffer. CPU data written across the APB interface is stored in the FIFO until read out by the transmit logic. The transmit FIFO can be disabled to act like a one-byte holding register. The receive FIFO is a 12-bit wide, 16-entry deep FIFO memory buffer. Received data and corresponding error bits, are stored in the receive FIFO by the receive logic until read out by the CPU across the APB interface. The receive FIFO can be disabled to act like a one-byte holding register.

The transmitter performs parallel-to-serial conversion on the data read from the transmit FIFO. Control logic outputs the serial bit stream beginning with a start bit, data bits, Least Significant Bit (LSB), a parity bit, and then stop bits according to the programmed configuration in control registers. The receiver performs serial-to-parallel conversion on the received bitstream after a valid start pulse has been detected. Overrun, parity, frame error checking, and line break detection are also performed, and the data with associated overrun, parity, framing, and break error bits is written to the receive FIFO.

The Interrupt Generator outputs a single, combined interrupt to the QL903M Interrupt Controller.

The SIR Transmit Encoder modulates the Non-Return-to-Zero (NRZ) transmit bitstream output from the QL903M chip. The IrDA SIR physical layer specifies use of a Return To Zero, Inverted (RZI) modulation scheme that represents logic 0 as an infrared light pulse. The modulated output pulse stream is transmitted to an external output driver and infrared Light Emitting Diode (LED).

The SIR Receive Decoder demodulates the return-to-zero bit stream from the infrared detector and outputs the received NRZ serial bitstream to the QL903M UART received data input. The decoder input is normally HIGH (marking state) in the idle state. The transmit encoder output has the opposite polarity to the decoder input.

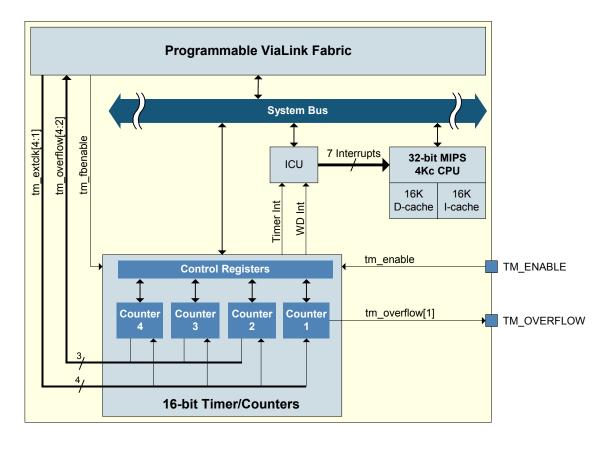

# **General Purpose 16-bit Timer/Counters**

The QL903M chip has four independent 16-bit timer/counter modules. The configuration registers for these modules are accessible through the System Bus (APB).

The System Bus clock (hclk), or an external clock supplied from the Fabric, drive the clock inputs on the timer/counter modules. These counters operate in one of four modes: decrement, increment, interval, or Pulse Width Modulation (PWM).

Each timer/counter module has the capability to generate system interrupts on various events.

One timer/counter is configured, by default, as a watchdog timer after a system reset. This watchdog timer has its own system interrupt output.

**Figure 9** shows a functional block diagram of the timer module.

Figure 9: Timer Functional Block Diagram

The key features of each timer/counter module are as follows:

- Up to 100 MHz operation.

- 32-bit data path on the System Bus.

- 16-bit timer/counter.

- 16-bit pre-scaler to increase timer/counter delay.

- Four modes of operation: decrement, increment, interval and PWM.

- Operation from the System Bus clock (hclk) or an external clock from the Fabric.

- Two external hardware timer enable signals can be used to start/stop the timer/counter. One of these signals can be supplied from the Fabric and the other is a dedicated input pin on the chip.

- Three match interrupts, one interval interrupt and one overflow interrupt.

- Six control registers to control various counter functions, including enable/disable, load, and reset.

The timer/counters are controlled by a set of control registers. Each timer/counter module has six control registers. By contrast, one interrupt register is used to control and convey the status of the interrupts from all the modules.

One counter (Counter 4) is configured, by default, to be used as a watchdog timer after the system reset. This watchdog timer has its own system interrupt output, and it can be reconfigured by software for use as a standard timer/counter.

#### **Fabric Side**

This section discusses the various circuit elements in the Fabric portion of the QL903M device.

#### **Logic Cells**

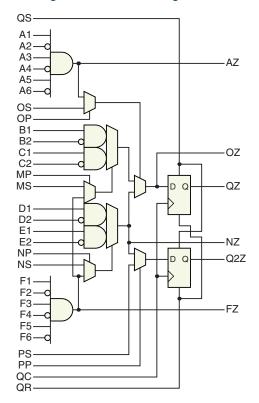

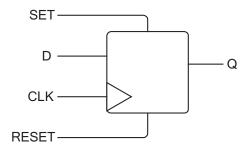

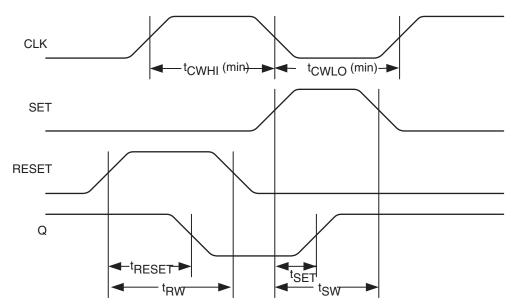

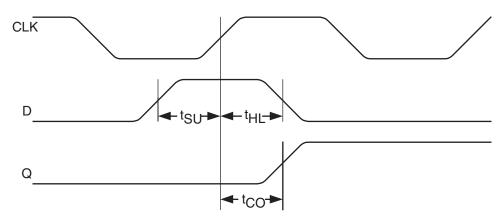

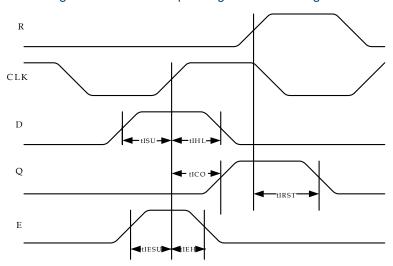

The QL903M logic cell structure presented in **Figure 10** is a dual register, multiplexor-based logic cell. It is designed for wide fan-in and multiple, simultaneous output functions. Both registers share CLK, SET, and RESET inputs. The second register has a two-to-one multiplexer controlling its input. The register can be loaded from the NZ output or directly from a dedicated input.

**NOTE:** The input PP is not an "input" in the classical sense. It is a static input to the logic cell and selects which path (NZ or PS) is used as an input to the Q2Z register. All other inputs are dynamic and can be connected to multiple routing channels.

The complete logic cell consists of two 6-input AND gates, four two-input AND gates, seven two-to-one multiplexers, and two D flip-flops with asynchronous SET and RESET controls. The cell has a fan-in of 30 (including register control lines), fits a wide range of functions with up to 17 simultaneous inputs, and has six outputs (four combinatorial and two registered). The high logic capacity and fan-in of the logic cell accommodates many user functions with a single level of logic delay while other architectures require two or more levels of delay.

Figure 10: QL903M Logic Cell

#### **Dual-Port SRAM Modules**

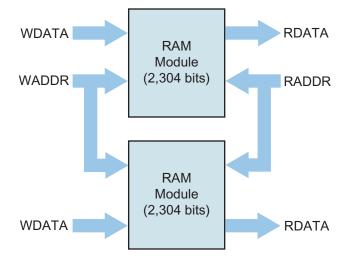

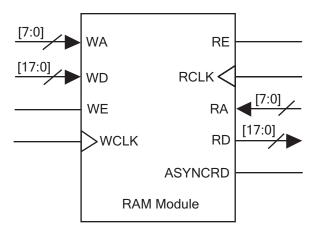

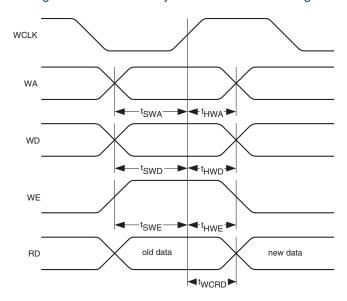

The QL903M includes up to 18 dual-port 2,304-bit RAM modules (shown in **Figure 11**) for implementing RAM, ROM, and FIFO functions. Each module is user-configurable into two different block organizations and can be cascaded vertically to increase their effective depth or horizontally to increase their effective width as shown in **Figure 12**.

MODE[1:0] ASYNCRD

WA[7:0] RA[7:0]

WD[17:0] RD[17:0]

WE RE

WCLK RCLK

2,304-bit Module

Figure 11: 2,304-bit RAM Module

Using two mode pins, designers can configure each module into 128 x 18 (Mode 0) or 256 x 9 (Mode1).

Figure 12: Cascaded RAM Modules

The RAM modules are dual-port, with completely independent READ and WRITE ports and separate READ and WRITE clocks. The READ ports support asynchronous and synchronous operation, while the WRITE ports support synchronous operation. Each port has 18 data lines and 8 address lines, allowing word lengths of up to 18 bits and address spaces of up to 256 words. Depending on the mode selected, however, some higher order data lines or the highest order address line may not be used.

The Write Enable (WE) line acts as a clock enable for synchronous write operation. The Read Enable (RE) acts as a clock enable for synchronous READ operation (ASYNCRD input low). The RE and RCLK inputs are ignored when ASYNCRD is tied high.

Designers can cascade multiple RAM modules to increase the depth or width allowed in single modules by connecting corresponding address lines together and dividing the words between modules.

A similar technique can be used to create depths greater than 256 words. In this case address signals higher than the eighth bit are encoded onto the write enable (WE) input for WRITE operations. The READ data outputs are multiplexed together using encoded higher READ address bits for the multiplexer SELECT signals.

The RAM blocks can be loaded with data generated internally (typically for RAM or FIFO functions) or with data from an external PROM (typically for ROM functions).

#### **Dual-Port SRAM Module Signals**

The dual-port RAM module signal descriptions are shown in **Table 6**.

Table 6: Dual-Port RAM Module Signal Descriptions

| Signal Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WCLK        | I   | Write Clock. Clock input for the write port of the RAM module. All write port input signals are synchronous with this clock.                                                                                                                                                                                                                                                                                                                                                                                              |

| WE          | I   | Write Enable. Sampled on the rising edge of WCLK, when WE is high, data is written into the RAM module at the specified write address.                                                                                                                                                                                                                                                                                                                                                                                    |

| WA(7:0)     | I   | <b>Write Address.</b> Sampled on the rising edge of WCLK, this is the write address for the data to be written into the RAM module. WA(7:0) is ignored when WE is low. Note that some higher order bits of WA(7:0) may not be used depending on the selected mode for the RAM module (see MODE(1:0) signal description).                                                                                                                                                                                                  |

| WD(17:0)    | I   | <b>Write Data.</b> Sampled on the rising edge of WCLK, this is the data to be written into the RAM module. WD(17:0) is ignored when WE is low. Note that some higher order bits of WD(17:0) may not be used depending on the selected mode for the RAM module (see MODE(1:0) signal description).                                                                                                                                                                                                                         |

| RCLK        | I   | Read Clock. This is the clock input for the read port of the RAM module. If ASYNCRD is low, all read port I/O signals are synchronous with this clock. If ASYNCRD is high, RCLK is ignored.                                                                                                                                                                                                                                                                                                                               |

| RE          | I   | Read Enable. Sampled on the rising edge of RCLK, when RE is high, data is read from the RAM module at the specified read address. If ASYNCRD is high, this RE is ignored.                                                                                                                                                                                                                                                                                                                                                 |

| RA(7:0)     | I   | Read Address. This is the read address for data to be read from the RAM module. If ASYNCRD is low, RA(7:0) is sampled only on the rising edge of RCLK while RE is high. If ASYNCRD is high, RA(7:0) is continuously sampled by the RAM module and RE has no effect. Note that some higher order bits of RA(7:0) may not be used depending on the selected mode for the RAM module (see MODE(1:0) signal description).                                                                                                     |

| RD(17:0)    | 0   | Read Data. This is the read output data from the RAM module. If the RAM module is in synchronous read mode (ASYNCRD low), valid read data is output immediately following the rising edge of RCLK which sampled RE as high. If the RAM module is in asynchronous read mode (ASYNCRD high), valid read data is output immediately after any change in the read address. Note that some higher order bits of RD(17:0) may not be used depending on the selected mode for the RAM module (see MODE(1:0) signal description). |

| ASYNCRD     | I   | Asynchronous Read Input. This signal, when high, indicates to the RAM block that the read port should operate asynchronously. When low, all read port I/O signals are synchronous with RCLK. This signal can only be tied to '1' or '0' inside the Fabric.                                                                                                                                                                                                                                                                |

| MODE(1:0)   | I   | Mode for RAM Module. These bits configure the width and depth of the RAM module (for both the read and write ports) and can only be tied to '1' or '0' inside the Fabric. The possible RAM module modes are:  MODE(1:0) = "00" : 128 x 18 (locations x data bits)  MODE(1:0) = "01" : 256 x 9 (locations x data bits)  MODE(1:0) = "1X" : Reserved                                                                                                                                                                        |

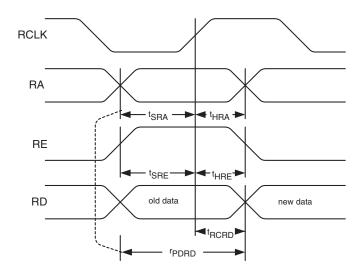

# **Embedded Computational Units (ECUs)**

Traditional Programmable Logic architectures do not implement arithmetic functions efficiently or effectively these functions require high logic cell usage while garnering only moderate performance results.

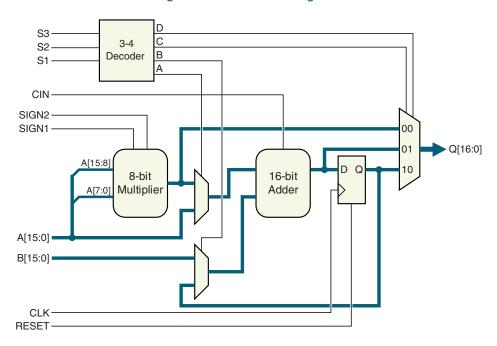

The QL903M architecture allows for functionality above and beyond that achievable using programmable logic devices. By embedding a dynamically reconfigurable computational unit, the QL903M device can address various arithmetic functions efficiently. This approach offers greater performance than traditional programmable logic implementations. The embedded block is implemented at the transistor level as shown in Figure 13.

Figure 13: ECU Block Diagram

#### **ECU Signals**

**Table 7** defines the ECU I/O signals. For more information on the operation of the ECU, see QuickLogic Application Note 52 at <a href="http://www.quicklogic.com/images/appnote52.pdf">http://www.quicklogic.com/images/appnote52.pdf</a>.

Table 7: ECU I/O Signals

| Signal Name | I/O | Description                                                                                                                                                           |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         | I   | Clock Input. Input clock for the ECU output register.                                                                                                                 |

| RESET       | I   | Reset Input. Active high reset input for the ECU output register.                                                                                                     |

| S1          | I   | <b>ECU Control S1.</b> One of three instruction signals that define the configuration mode of the ECU (see <b>Table 8</b> ).                                          |

| S2          | I   | <b>ECU Control S2.</b> One of three instruction signals that define the configuration mode of the ECU (see <b>Table 8</b> ).                                          |

| S3          | I   | <b>ECU Control S3.</b> One of three instruction signals that define the configuration mode of the ECU (see <b>Table 8</b> ).                                          |

| CIN         | I   | Carry Input. 1-bit Carry In for 16-bit adder operations.                                                                                                              |

| SIGN1       | I   | Sign Input for Multiplier A Input. When SIGN1 = '1', A(7:0) is treated as signed or two's complement binary. When SIGN1 = '0' A(7:0) is treated as unsigned binary.   |

| SIGN2       | I   | Sign Input for Multiplier B Input. When SIGN2 = '1', B(15:8) is treated as signed or two's complement binary. When SIGN2 = '0' B(15:8) is treated as unsigned binary. |

| A(15:0)     |     | <b>Augend Input.</b> 16-bit augend input of the 16-bit adder when the ECU is in any of the adder configuration modes.                                                 |

| A(15:8)     | I   | Multiplicand Input. 8-bit multiplicand input when the ECU is in any of the multiplier configuration modes.                                                            |

| A(7:0)      |     | Multiplier Input. 8-bit multiplier input when the ECU is in any of the multiplier configuration modes.                                                                |

| B(15:0)     | I   | Addend Input. 16-bit addend input when ECU is in any of the adder configuration modes.                                                                                |

| Q(16:0)     | 0   | <b>ECU Output.</b> This is the 17-bit output of the ECU. The interpretation of the value of Q(16:0) depends on the setting of S1, S2, S3, SIGN1, and SIGN2.           |

The QL903M ECU blocks are placed next to the SRAM circuitry for efficient memory/instruction fetch and addressing for DSP algorithmic implementations.

Up to eighteen 8-bit MAC functions can be implemented per cycle for a total of 1.8 billion MACs/s when clocked at 100 MHz. Additional multiply-accumulate functions can be implemented in the programmable logic.

The instruction modes for the ECU block are dynamically re-programmable through the programmable logic as shown in **Table 8**.

Table 8: ECU Mode Select Criteria

| In | Instruction |    | Operation                          |  |  |

|----|-------------|----|------------------------------------|--|--|

| S1 | S2          | S3 | Operation                          |  |  |

| 0  | 0           | 0  | Multiply                           |  |  |

| 0  | 0           | 1  | Multiply-Add                       |  |  |

| 0  | 1           | 0  | Accumulate                         |  |  |

| 0  | 1           | 1  | Add                                |  |  |

| 1  | 0           | 0  | Multiply (registered) <sup>a</sup> |  |  |

| 1  | 0           | 1  | Multiply- Add (registered)         |  |  |

| 1  | 1           | 0  | Multiply - Accumulate              |  |  |

| 1  | 1           | 1  | Add (registered)                   |  |  |

a. B (15:0) set to zero.

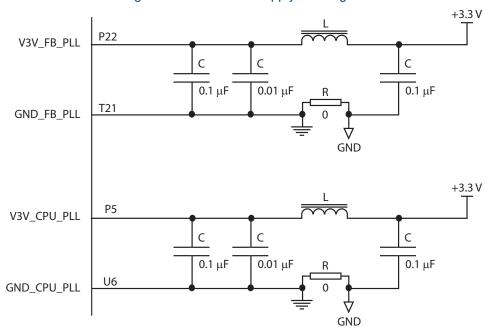

#### **Fabric PLL**

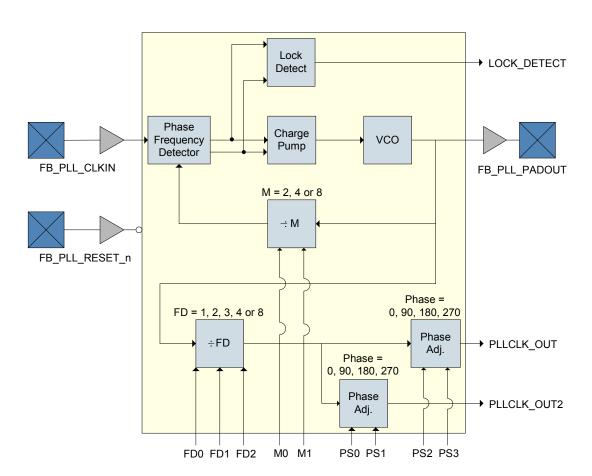

Instead of requiring extra components, designers simply need to instantiate the QL903M Fabric PLL model (described in this section). The Fabric PLL built into the QL903M supports a wider range of frequencies than many other PLLs. The PLL also has the ability to support different ranges of frequency multiplications or divisions, driving the Fabric at a faster or slower rate than the incoming clock frequency.

Figure 14 illustrates the QL903M Fabric PLL.

Figure 14: QL903M Fabric PLL Block Diagram

The QL903M Fabric PLL is driven by the FB\_PLL\_CLKIN input pin. This input is used by the PLL as a clock reference for the Voltage Controlled Oscillator (VCO) internal to the PLL circuit. Using the M1 and M0 inputs to the PLL block, the designer may choose a frequency multiplier value for the VCO. The PLL output pin, FB\_PLL\_PADOUT runs at the VCO operational frequency. Table 9 shows the minimum and maximum input  $(\boldsymbol{F}_{in})$  and output  $(\boldsymbol{F}_{pad})$  frequency for each possible VCO multiplier mode.

Table 9: Frequency Ranges for Fabric PLL Input Pad (FB\_PLL\_CLKIN), Output Pad (FB\_PLL\_PADOUT) and VCO

| M1 | МО | VCO Mode                      | FB_PLL_CLKIN<br>(F <sub>in</sub> )<br>Input Frequency Range | FB_PLL_PADOUT<br>(F <sub>vco</sub> and F <sub>pad</sub> )<br>Pad Output Frequency Range |  |

|----|----|-------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| 0  | 0  | 2x                            | 50.0 to 150.0 MHz                                           | 100 to 300 MHz                                                                          |  |

| 0  | 1  | 4x                            | 25.0 to 75.0 MHz                                            | 100 to 300 MHz                                                                          |  |

| 1  | 0  | 8x                            | 12.5 to 37.5 MHz                                            | 100 to 300 MHz                                                                          |  |

| 1  | 1  | Reserved – should not be used |                                                             |                                                                                         |  |

In addition to the Fabric PLL output pin, the PLL can also drive two clock networks in the Fabric. These two additional outputs, PLLCLK\_OUT and PLLCLK\_OUT2 offer further control over frequency and phase by adding an output frequency divider and phase adjustment control. PLLCLK\_OUT and PLLCLK\_OUT2 can be configured for different output phases, but they both operate at the same frequency. **Table 10** shows the Fabric clock network PLLCLK\_OUT resultant output frequency ( $F_{fab}$ ), duty cycle and phase based on the FD2, FD1, FD0, PS3 and PS2 inputs.

Table 10: Frequency, Duty Cycle and Phase Values for Fabric PLL Output PLLCLK\_OUT

|     | Fabric Output PLLCLK_OUT |     |                               |                      |                      |          |          |      |   |   |      |   |   |    |

|-----|--------------------------|-----|-------------------------------|----------------------|----------------------|----------|----------|------|---|---|------|---|---|----|

| FD2 | FD1                      | FD0 | (F <sub>fab</sub> ) Frequency | Duty Cycle           | PS3                  | PS2      | Phase    |      |   |   |      |   |   |    |

| 0   | 0                        | 0   | F <sub>vco</sub>              | 50%                  | Х                    | Х        | 0°       |      |   |   |      |   |   |    |

|     |                          |     |                               |                      | 0                    | 0        | 180°     |      |   |   |      |   |   |    |

| 0   | 0                        | 1   | E /2                          | 50%                  | 0                    | 1        | 270°     |      |   |   |      |   |   |    |

| U   | U                        | l   | F <sub>vco</sub> /2           | 50 %                 | 1                    | 0        | 0°       |      |   |   |      |   |   |    |

|     |                          |     |                               |                      | 1                    | 1        | 90°      |      |   |   |      |   |   |    |

| 0   | 1                        | 0   | F <sub>VCO</sub> / 3          | 33%                  | Х                    | Х        | 0°       |      |   |   |      |   |   |    |

|     | 1 1                      |     |                               |                      |                      |          |          |      |   |   |      | 0 | 0 | 0° |

| 0   |                          | 4   |                               | 50%                  | 0                    | 1        | 90°      |      |   |   |      |   |   |    |

| U   |                          |     | Į.                            | F <sub>VCO</sub> / 4 | F <sub>VCO</sub> / 4 | FVCO / 4 | FVCO / 4 | 50 % | 1 | 0 | 180° |   |   |    |

|     |                          |     |                               |                      | 1                    | 1        | 270°     |      |   |   |      |   |   |    |

|     |                          |     |                               |                      | 0                    | 0        | 270°     |      |   |   |      |   |   |    |

| 4   |                          | X   | E /0                          | F09/                 | 0                    | 1        | 0°       |      |   |   |      |   |   |    |

| ļ . | ^                        |     | 50%                           | 1                    | 0                    | 90°      |          |      |   |   |      |   |   |    |

|     |                          |     |                               |                      | 1                    | 1        | 180°     |      |   |   |      |   |   |    |

NOTE: PLLCLK\_OUT phase shown in the Table 10 is based on the period 1/F<sub>fab</sub>.

**NOTE:** An output phase of 0° indicates that the rising edge of PLLCLK\_OUT will be aligned with the rising edge of FB\_PLL\_CLKIN.

**NOTE:** To maintain the phase values shown in **Table 10**,  $F_{VCO}$  should not exceed 200 MHz. If  $F_{VCO}$  is set above 200 MHz, the phase of PLLCLK\_OUT will have no guaranteed relation to FB\_PLL\_CLKIN.

**Table 11** shows the Fabric clock network PLLCLK\_OUT2 resultant output frequency ( $F_{fab}$ ), duty cycle and phase based on the FD2, FD1, FD0, PS1 and PS0 inputs.

Table 11: Frequency, Duty Cycle and Phase Values for Fabric PLL Output PLLCLK\_OUT2

| Fabric Output PLLCLK_OUT2 |     |                        |                               |                          |     |      |       |   |   |    |

|---------------------------|-----|------------------------|-------------------------------|--------------------------|-----|------|-------|---|---|----|

| FD2                       | FD1 | FD0                    | (F <sub>fab</sub> ) Frequency | Duty Cycle               | PS1 | PS0  | Phase |   |   |    |

| 0                         | 0   | 0                      | F <sub>vco</sub>              | 50%                      | Х   | Х    | 0°    |   |   |    |

|                           |     |                        |                               |                          | 0   | 0    | 180°  |   |   |    |

| 0                         | 0   | 1                      | E /2                          | 50%                      | 0   | 1    | 270°  |   |   |    |

|                           | 0   | ı                      | F <sub>vco</sub> /2           | 30 /6                    | 1   | 0    | 0°    |   |   |    |

|                           |     |                        |                               |                          | 1   | 1    | 90°   |   |   |    |

| 0                         | 1   | 0                      | F <sub>VCO</sub> / 3          | 33%                      | Х   | Х    | 0°    |   |   |    |

|                           | 1   | 1 F <sub>VCO</sub> / 4 |                               |                          |     |      |       | 0 | 0 | 0° |

| 0                         |     |                        | F /4                          | 50%                      | 0   | 1    | 90°   |   |   |    |

|                           | I   |                        | 30 /6                         | 1                        | 0   | 180° |       |   |   |    |

|                           |     |                        |                               |                          | 1   | 1    | 270°  |   |   |    |

|                           |     |                        |                               |                          | 0   | 0    | 270°  |   |   |    |

| 4                         | 1 X | X F <sub>VCO</sub> / 8 | E /0                          | F <sub>VCO</sub> / 8 50% | 0   | 1    | 0°    |   |   |    |

| '                         |     |                        | FVCO / 6                      |                          | 1   | 0    | 90°   |   |   |    |

|                           |     |                        |                               |                          | 1   | 1    | 180°  |   |   |    |

NOTE: PLLCLK\_OUT2 phase shown in the Table 11 is based on the period 1/F<sub>fab</sub>.

NOTE: An output phase of 0° indicates that the rising edge of PLLCLK\_OUT2 will be aligned with the rising edge of FB\_PLL\_CLKIN.

**NOTE:** To maintain the phase values shown in **Table 11**,  $F_{VCO}$  should not exceed 200 MHz. If  $F_{VCO}$  is set above 200 MHz, the phase of PLLCLK\_OUT2 will have no guaranteed relation to FB\_PLL\_CLKIN.

#### **Fabric PLL Signals**

**Table 12** summarizes the key signals of the QL903M Fabric PLL.

Table 12: Fabric PLL I/O Signals

| Signal Name    | I/O | Description                                                                                                                                                                                                                                                                                                                  |

|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FB_PLL_CLKIN   | ı   | Input clock signal. See Table 50 for more details.                                                                                                                                                                                                                                                                           |

| FB_PLL_RESET_n | ı   | Active low reset. See Table 50 for more details.                                                                                                                                                                                                                                                                             |

| FB_PLL_PADOUT  | 0   | PLL output off chip. See Table 50 for more details.                                                                                                                                                                                                                                                                          |

| PLLCLK_OUT     | 0   | PLL output to Fabric (1 of 2). This is the PLL output clock driven to the Fabric clock network. This output runs at the $F_{fab}$ frequency described in <b>Table 10</b> . Furthermore, this output is also phase adjustable. The output frequency and phase is determined by the M(1:0), FD(2:0) and PS(3:2) inputs.        |

| PLLCLK_OUT2    | 0   | PLL output to Fabric (2 of 2). This is the PLL output clock driven to the Fabric clock network. This output runs at the F <sub>fab</sub> frequency described in <b>Table 11</b> . Furthermore, this output is also phase adjustable. The output frequency and phase is determined by the M(1:0), FD(2:0) and PS(1:0) inputs. |

Table 12: Fabric PLL I/O Signals (Continued)

| Signal Name | I/O | Description                                                                                                                                          |

|-------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK_DETECT | 0   | Active high lock detection signal. This signal is output to the Fabric and goes high when the PLL VCO is locked to the input clock reference.        |

| M(1:0)      | I   | VCO frequency multiplier input. These inputs are statically driven high or low by the Fabric. See <b>Table 9</b> for their effect on PLL operation.  |

| FD(2:0)     | I   | Fabric output frequency divide input. These inputs are statically driven high or low by the Fabric. See Table 10 for their effect on PLL operation.  |

| PS(3:2)     | I   | Phase select input for Fabric output. These inputs are statically driven high or low by the Fabric. See Table 10 for their effect on PLL operation.  |

| PS(1:0)     | I   | Phase select input for Fabric output2. These inputs are statically driven high or low by the Fabric. See Table 11 for their effect on PLL operation. |

NOTE: Because FB\_PLL\_CLKIN, FB\_PLL\_RESET\_n, and FB\_PLL\_PADOUT have appropriate INPAD and OUTPADs included, you do not have to add these pads to your design.

#### Advanced Clock Networks

The QL903M device has a large number of extremely advanced and highly flexible clock networks. These consist of three basic types of networks; a Global Network and a Dedicated Network (for low-skew applications), and an I/O Control/Hi-Drive Network (for high-fanout, multi-load applications).

#### **Global and Dedicated Low-Skew Networks**

The Global and Dedicated Networks are low-skew networks typically used to drive clock signals throughout the entire device. In addition, the Global Network can also be used to globally drive other high-fanout signals with low skew (e.g., flip-flop set or reset signals). Both networks are segmented, separated on a per-quadrant basis. (Unlike the QuickLogic Eclipse architecture, the QL903M has only two quadrants.) Figure 15 shows a simplified view of the low-skew clock network architecture in the QL903M device.

Upper Left Upper Right 2222 Global and **Dedicated Networks** CLK Pin

reliminary

Figure 15: Low Skew Clock Architecture

**Table 13** shows the number of Global and Dedicated Networks available per quadrant in the QL903M.

Table 13: Number of QL903M Low-Skew Clock Networks

| Clock Network Type | Quadrant               |                        | Total |

|--------------------|------------------------|------------------------|-------|

|                    | Upper Left             | Upper Right            | iolai |

| Global             | 8<br>(5 are Quad-Nets) | 8<br>(5 are Quad-Nets) | 16    |

| Dedicated          | 1                      | 1                      | 2     |

| Total              | 9                      | 9                      | 18    |

As Table 13 shows, there are a total of nine low-skew networks per quadrant in the QL903M, making a total of eighteen in the entire device. Each quadrant contains eight Global Networks and one Dedicated Network.

The Global Network and Dedicated Network differ slightly in performance and flexibility. The Dedicated Network offers superb low-skew and minimal pin to logic element delay performance, but can only drive the clock inputs of specific Fabric elements. The Global Network offers more flexibility to drive a variety of inputs in the Fabric as well as internal ASSP port inputs, but at a slight increase in skew and delay. Table 14 outlines all allowable input destinations for each clock network type.

Table 14: Allowable Inputs Destinations for Global and Dedicated Networks

| Element        | Inputs That Can be Driven by<br>the Global Clock Network | Inputs That Can be Driven by the Dedicated Clock Network |  |

|----------------|----------------------------------------------------------|----------------------------------------------------------|--|

| Logic Cells    | QC                                                       | QC                                                       |  |

|                | A2                                                       |                                                          |  |

|                | F1                                                       |                                                          |  |

|                | QS                                                       |                                                          |  |

|                | QR                                                       |                                                          |  |

| RAM Modules    | WCLK                                                     | WCLK                                                     |  |

|                | RCLK                                                     |                                                          |  |

|                | RE                                                       | RCLK                                                     |  |

|                | WE                                                       | HOLK                                                     |  |

| ECHO           | CLK                                                      |                                                          |  |

| ECUs           | RESET                                                    | <del>-</del>                                             |  |

| I/O Cells      | IQC                                                      | IQC                                                      |  |

|                | IQR                                                      |                                                          |  |

|                | EQE                                                      |                                                          |  |

|                | IQE                                                      |                                                          |  |

|                | IE                                                       |                                                          |  |

| ASSP Interface | All Inputs                                               | -                                                        |  |

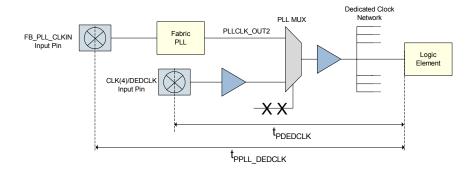

Each quadrant consists of an element called the PLLMUX that drives the Global Networks and the Dedicated Network in the quadrant. The PLLMUX selects between external CLK input pins and clock signals that are driven from other elements internal to the device such as the Fabric PLL and the ASSP System Bus clock (hclk). Figure 16 shows a simplified schematic diagram of the CLK input pins, the PLLMUX elements and the associated clock networks.

Global Clock Network PLL MUX hclk Element CLK(2) Input Pin XX  $t_{PGCK}$ t<sub>BGCK</sub> Global Clock Network PLL MUX PLLCLK\_OUT Logic Element CLK(3) Input Pin XXt<sub>PGCK</sub>  $t_{BGCK}$ Global Clock Network PLL MUX No Connection Logic Element CLK(5) Input Pin  $t_{PGCK}$  $t_{BGCK}$ **Dedicated Clock** PLL MUX Network PLLCLK\_OUT2 Logic Element CLK(4)/DEDCLK Input Pin

Figure 16: Low Skew Clock Structure Schematic Based Upon PLLMUX Elements (1 of 2 Quadrants)

XX

$\mathbf{t}_{\text{PDEDCLK}}$

If either of the Fabric PLL outputs or hclk are utilized in a given quadrant of the Fabric design, the QuickWorks software automatically configures the corresponding PLLMUX to select the internal clock input. Each quadrant consists of four PLLMUX elements of which one input is tied to a specific CLK input pin as shown in **Table 15**.

Table 15: PLLMUX Input Signals and Output Type (Per Quadrant)

| Input         |                  | Output Type             |  |

|---------------|------------------|-------------------------|--|

| Pin           | Internal Signals | Output Type             |  |

| CLK(2)        | hclk             | Global clock network    |  |

| CLK(3)        | PLLCLK_OUT       | Global clock network    |  |

| CLK(4)/DEDCLK | PLLCLK_OUT2      | Dedicated clock network |  |

| CLK(5)        | -                | Global clock network    |  |

As **Table 15** indicates, once a PLLMUX is used to drive an internal signal onto the Global or Dedicated Networks, the corresponding CLK input pin is blocked from entering that quadrant.

**NOTE:** If either of the Fabric PLL outputs or hclk are utilized in the Fabric design, and external clock pins are also utilized, the designer should choose clock input pins on the device that do not conflict with these corresponding PLLMUX elements.

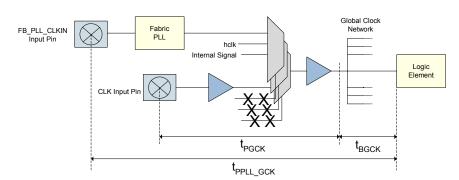

#### **Quad-Net Network (Subset of the Global Network)**

In each quadrant, the remaining five Global Networks are also referred to as Quad-Net Networks. Quad-Nets are networks that can be driven by input CLK pins or by signals that are generated internally to the Fabric. Quad-Nets are driven by an element in the Fabric called the HSCKMUX. **Figure 17** shows a simplified schematic diagram of the CLK input pins, the HSCKMUX elements and the associated Quad-Net networks.

Global Clock Network HSCKMUX (Quad-Net) Any Fabric Signal Logic Element CLK(0) Input Pin XX $t_{PGCK}$  $t_{BGCK}$ Global Clock Network **HSCKMUX** (Quad-Net) Any Fabric Signal Logic Element CLK(1) Input Pin -XX $t_{\text{PGCK}}$  $t_{BGCK}$ Global Clock Network HSCKMUX (Quad-Net) Any Fabric Signal Logic Element CLK(6) Input Pin XXt<sub>PGCK</sub> t<sub>BGCK</sub> Global Clock Network (Quad-Net) HSCKMUX Any Fabric Signal XX $t_{PGCK}$  $t_{\text{BGCK}}$ Global Clock Network HSCKMUX (Quad-Net) Any Fabric Signal Logic Element CLK(8) Input Pin

Figure 17: Low Skew Clock Structure Schematic Based Upon HSCKMUX Elements (1 of 2 Quadrants)

XX

$t_{BGCK}$

$t_{PGCK}$

By instantiating the gclkbuff\_25um macro with a given Fabric signal as its input, the designer can program an HSCKMUX to drive this signal on a Quad-Net (the QuickWorks tool automatically chooses which HSCKMUX to use). Each quadrant consists of five HSCKMUX elements of which one input is tied to a specific CLK input pin as shown in **Table 16**.

| Input  |                  | Output Type                     |  |

|--------|------------------|---------------------------------|--|

| Pin    | Internal Signals | Output Type                     |  |

| CLK(0) | Any Signal       | Global clock network (Quad-Net) |  |

| CLK(1) | Any Signal       | Global clock network (Quad-Net) |  |

| CLK(6) | Any Signal       | Global clock network (Quad-Net) |  |

| CLK(7) | Any Signal       | Global clock network (Quad-Net) |  |

| CLK(8) | Any Signal       | Global clock network (Quad-Net) |  |

Table 16: HSCKMUX Input Signals and Output Type (Per Quadrant)

As **Table 16** indicates, once an HSCKMUX is used to drive an internal signal onto the Quad-Net Network, the corresponding CLK input pin is blocked from entering that quadrant.

NOTE: If the sum of utilized clock input pins from **Table 16** and the number of instantiated gclkbuff\_25um macros is greater than five, the QuickWorks software may be unable to successfully resolve the conflicts between the CLK input pins and the internally generated clock input signals. This is dependant on several factors, but in most cases can be attributed to the size and complexity of the Fabric design.

#### I/O Control/Hi-Drive Network

The I/O Control/Hi-Drive Network is used primarily to drive high-fanout (typically other than clock or reset) signals throughout the device. Each bank of I/Os has two input-only pins entitled IOCTRL that can be programmed to drive the IQC (flip-flop clock), IQR (flip-flop reset), EQE & IQE (flip-flop enables), and IE (output enable) inputs of each I/O cell in that bank. These input-only pins also simultaneously serve as high drive inputs to any logic element input located in the adjacent quadrant. In addition, the I/O Control/Hi-Drive Network can be driven by the internal logic by instantiating the io\_buff\_25um macro. The QL903M has a total of eight IOCTRL input pins which are also shared with the io\_buff\_25um macros (i.e., if a io\_buff\_25um macro is utilized at a specific location, the corresponding IOCTRL input pin is ignored by the device. The performance of this network is presented in **Table 35**.

#### **General Routing Network**

QL903M devices are delivered with six types of routing resources as follows: short (sometimes called segmented) wires, dual wires, quad wires, express wires, distributed networks, and default wires. Short wires span the length of one logic cell, always in the vertical direction. Dual wires run horizontally and span the length of two logic cells. Short and dual wires are predominantly used for local connections. Default wires supply  $V_{CC}$  and GND (Logic '1' and Logic '0') to each column of logic cells.

Quad wires have passive link interconnect elements every fourth logic cell. As a result, these wires are typically used to implement intermediate length or medium fan-out nets.

Express lines run the length of the programmable logic uninterrupted. Each of these lines has a higher capacitance than a quad, dual, or short wire, but less capacitance than shorter wires connected to run the length of the device. The resistance will also be lower because the express wires don't require the use of "pass" links. Express wires provide higher performance for long routes or high fan-out nets.