$oldsymbol{A}$  plus make your production a-plus

# VOICE OTP IC aP8821 - 21"voice otp

# APLUS INTEGRATED CIRCUITS INC.

#### **Address:**

3 F-10, No. 32, Sec. 1, Chenggung Rd., Taipei, Taiwan 115, R.O.C.

(115)台北市南港區成功路一段 32 號 3 樓之 10.

TEL: 886-2-2782-9266 FAX: 886-2-2782-9255

**WEBSITE**: <a href="http://www.aplusinc.com.tw">http://www.aplusinc.com.tw</a>

Sales E-mail:

sales@aplusinc.com.tw

**Technology E-mail:**

service@aplusinc.com.tw

# 21 sec VOICE OTP

#### Features

- 21 Sec Voice Length at 6 KHz

- Combination of voice building blocks extends the duration of playback

- Voice data re-use saves memory space

- Maximum 14 voice groups

- 4 trigger pins, S1 to S4 for the 4 voice groups (group1 ~ 4)

- SBT for sequential playblack for the rest of voice groups & CPU mode trigger

- CPU trigger mode for all 14 voice groups

- Holdable, Unholdable, Edge, Level triggering option

- Debounce time : 21ms ( Key mode ) / 85us (CPU mode ) - 6K sampling rate

- IRP interrupt pin for master reset

- 3 programmable Outputs for STP stop pulse, BUSY and LED

- Built-in oscillator with a single external resistor to determine the sampling rate

- Built-in D/A converter, EPROM

- ADPCM data compression provides high sound quality

- Optional POP noise elimination function

- C<sub>OUT</sub> pin drives speaker with a transistor

- V<sub>OUT1</sub> and V<sub>OUT2</sub> drives buzzer or speaker directly

- Auto-power down

- 2.4V 4.8V single power supply operation

- Low standby current (<5uA at 3V)

- Development Tools Support

# **■** General Description

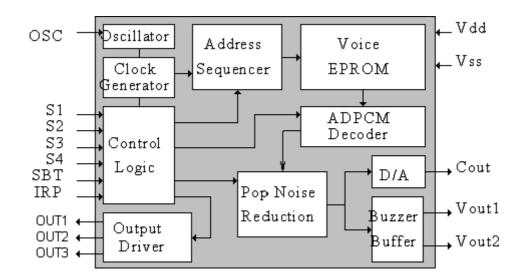

**aP8821** is a high quality voice synthesizer capable of varying playback duration. A proprietary ADPCM algorithm is used. The audio message is stored in a 512K bits on-chip EPROM which can store up to 21 seconds of voice data at 6 KHz sample rate.

The **aP8821** eliminates the need of complicated circuitry in voice playback but still achieves high voice quality for different kind of sounds. Combinations in sections achieve longer playback duration.

A pair of PWM output pins, V<sub>OUT1</sub> and V<sub>OUT2</sub> provides direct drive to buzzer or speaker.

A current output pin,  $C_{OUT}$ , enables the device to drive a speaker through a low cost NPN transistor. No complex filtering or amplifier circuit is needed. An automatic ramp-down function eliminates undesired noise at the end of playback.

### **■** Group of sections

The voice memory of the **aP8821** can be subdivided into 126 memory blocks. Any combination of playback of these memory blocks will form an individual voice group. A maximum of 14 groups are available with triggering S1 to S4 pins together with the SBT pin sequential playback pin.

# ■ Group Configuration

Data within each group are combinations of different fixed memory blocks of up to 126 blocks. They are the fundamental building blocks for arranging playback without limiting sequencing. This provides flexibility and allows data to be re-used, beneficial for applications with many repeated sounds or words.

An example of group configuration is illustrated below:

| Group no. | Section entry                         |  |  |  |  |  |

|-----------|---------------------------------------|--|--|--|--|--|

| Group 1   | Block 1 + Block 2 + Block 3 Block 109 |  |  |  |  |  |

| Group 2   | Block 3 + Block 2                     |  |  |  |  |  |

| Group 3   | Block 10 + Block 11 + Block 12        |  |  |  |  |  |

| Group 4   | Block 10 + Block 10 + Block 5         |  |  |  |  |  |

The entries of blocks for each group is truly random and without limitation. However, there is a limit in the total number of entries for 14 voice groups, which is 960 entries in **aP8821**. It is acceptable to allocate all entries into only one group or distribute out to other groups. It depends on how many groups of messages are required.

#### Programmable Options

Each groups in **aP8821** can have independent options. They include:

- Edge or Level trigger

- Unholdable or Holdable trigger

- Re-triggerable or non-retriggerable

- Outputs are programmable to LED1, LED2, BUSY and STOP pulse

Options that affect all voice groups are called whole chip options. They include:

- Key trigger mode or CPU trigger mode

- Ramp enable or Ramp disable

# Output Selections

There are three independent output pins OUT1, OUT2 and OUT3, available for four combinations of LED1, LED2, STOP and BUSY signals for each voice group.

|    | OUT1 | OUT2 | OUT3  |

|----|------|------|-------|

| 1. | LED2 | LED1 | BUSY  |

| 2. | STOP | LED1 | LED2  |

| 3. | LED1 | BUSY | STOP  |

| 4. | LED1 | BUSY | /BUSY |

LED1 and LED2 are complemented outputs flashing at a fix interval. STOP pulse gives a long enough positive pulse at the end of the playback for each group with option to enable or disable it.

BUSY is active high depends on voice Block setting. That means BUSY signal can be set to high when some voice Blocks are being played but set to low for the others.

### **■** Software Support

All those Options and Output selections can be set with a dedicated OTP compiler and programmer software supplied by APLUS.

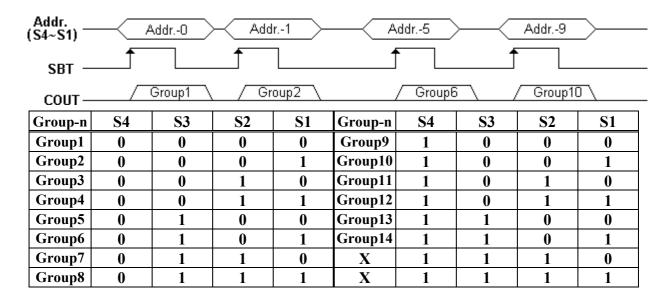

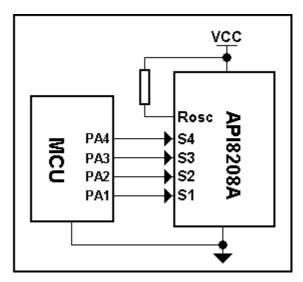

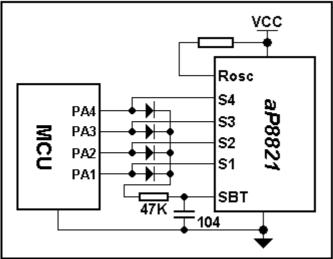

#### ■ Key trigger mode and CPU trigger mode

In Key trigger mode, S1 to S4 will trigger four voice groups. The rest of the voice groups can only be triggered by SBT sequential trigger pin.

In CPU trigger mode, binary data is input to S4~S1. A high pulse is input to SBT pin with pulse width equal to or longer than the debounce time to strobe the data to initial the playblack. Data patterns "1110" and "1111" is not allowed.

# **■** Block Diagram

# ■ Absolute Maximum Rating

| Symbol                            | Rating                                 | Unit                   |

|-----------------------------------|----------------------------------------|------------------------|

| V <sub>DD</sub> - V <sub>SS</sub> | -0.5 ~ +5.0                            | V                      |

| V <sub>IN</sub>                   | $V_{SS} - 0.3 < V_{IN} < V_{DD} + 0.3$ | V                      |

| V <sub>OUT</sub>                  | $V_{SS} < V_{OUT} < V_{DD}$            | V                      |

| T (Operating)                     | -10 ~ +60                              | $^{\circ}\!\mathbb{C}$ |

| T (Storage)                       | -55 ~ +125                             | $^{\circ}\!\mathbb{C}$ |

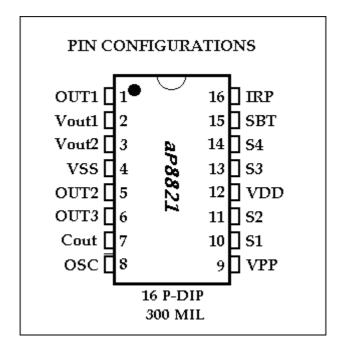

# ■ Pin Description

| Pin No. | Name            | I/O/P | Function                                                              |  |

|---------|-----------------|-------|-----------------------------------------------------------------------|--|

| 1       | OUT3            | О     | Programmable output 3                                                 |  |

| 2       | $V_{OUT1}$      | О     | PWM audio signal output 1 for buzzer & speaker                        |  |

| 3       | $V_{ m OUT2}$   | О     | PWM audio signal output 2 for buzzer & speaker                        |  |

| 4       | V <sub>SS</sub> | P     | Power ground                                                          |  |

| 5       | OUT1            | О     | Programmable output 1                                                 |  |

| 6       | OUT2            | О     | Programmable output 2                                                 |  |

| 7       | $C_{OUT}$       | О     | Current output from internal DAC for speaker playback                 |  |

| 8       | OSC             | I     | Oscillator resistor pin to control sampling frequency                 |  |

| 9       | VPP             | P     | Program power,<br>must connect to VDD when playback                   |  |

| 10      | S1              | I     | Trigger switch 1 / CPU Addr.1( LSB ), internal pull low, active high  |  |

| 11      | S2              | I     | Trigger switch 2 / CPU Addr.2, internal pull low, active high         |  |

| 12      | $V_{ m DD}$     | P     | Positive power supply                                                 |  |

| 13      | S3              | I     | Trigger switch 3 / CPU Addr.3, internal pull low, active high         |  |

| 14      | S4              | I     | Trigger switch 4 / CPU Addr.4 ( MSB ), internal pull low, active high |  |

| 15      | SBT             | I     | Key Sequential/CPU trigger, internal pull low, active high            |  |

| 16      | IRP             | Ι     | Interrupt to stop playback, internal pull low, active high            |  |

Note: The following pins are used to program data into the memory: pin 4, 5, 6, 8, 9, 12,15 and 16.

# **■ DC Characteristics**

| Symbol            | Parameter                         | Min. | Тур. | Max. | Unit       | Condition                                                                               |

|-------------------|-----------------------------------|------|------|------|------------|-----------------------------------------------------------------------------------------|

| V <sub>DD</sub>   | Operating Voltage                 | 2.4  | 3.0  | 4.8  | V          |                                                                                         |

| $I_{SB}$          | Standby current                   | _    | 1    | 5    | μ <b>A</b> | V <sub>DD</sub> =3.0V, I/O open                                                         |

| I <sub>OP</sub>   | Operating current                 | _    |      | 15   | mA         | V <sub>DD</sub> =3.0V, I/O open                                                         |

| V <sub>IH</sub>   | "H" Input Voltage                 | 2.5  | 3.0  | 3.5  | V          | V <sub>DD</sub> =3.0V                                                                   |

| $V_{\mathrm{IL}}$ | "L" Input Voltage                 | -0.3 | 0    | 0.5  | V          | V <sub>DD</sub> =3.0V                                                                   |

| $I_{OH}$          | V <sub>OUT</sub> low O/P Current  | _    | 70   |      | mA         | V <sub>DD</sub> =3.0V, Vout=0.3V                                                        |

| $I_{OL}$          | V <sub>OUT</sub> high O/P Current | _    | -40  |      | mA         | V <sub>DD</sub> =3.0V, Vout=2.5V                                                        |

| I <sub>CO</sub>   | C <sub>OUT</sub> O/P Current      | _    | -3   |      | mA         | V <sub>DD</sub> =3.0V,V <sub>COUT</sub> =1.0V                                           |

| $I_{OH}$          | O/P high Current                  | _    | -8   |      | mA         | V <sub>DD</sub> =3.0V, V <sub>OH</sub> =2.5V                                            |

| I <sub>OL</sub>   | O/P low Current                   | _    | 8    |      | mA         | V <sub>DD</sub> =3.0V, V <sub>OL</sub> =0.3V                                            |

| ΔF/F              | Frequency Stability               | -5   |      | +5   | %          | $\frac{\operatorname{Fosc}(2.7V) - \operatorname{Fosc}(3.4V)}{\operatorname{Fosc}(3V)}$ |

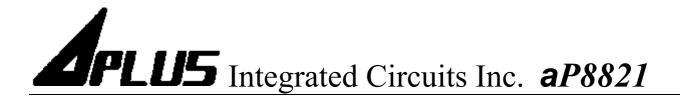

# **■** Timing Diagram

| 4. Edge, Unholdable, Non-retriggerable a. Trigger is shorter than a Group output | b. Trigger is longer than a Group output |

|----------------------------------------------------------------------------------|------------------------------------------|

| sı                                                                               |                                          |

| S2                                                                               |                                          |

| cour Group2 Group1                                                               | √ Group2 \                               |

| STP                                                                              | Π                                        |

| LED                                                                              |                                          |

| 5. Edge Holdable a. Trigger is shorter than a Group output                       | b. Trigger is longer than a Group output |

| sı                                                                               |                                          |

| S2                                                                               |                                          |

| COUT Group2 Group1                                                               | Group2                                   |

| LED                                                                              |                                          |

| 6. Single Button Trigger(SBT), Sequential                                        |                                          |

| a. Edge Unholdable                                                               |                                          |

| SBT                                                                              |                                          |

| COUT Group 1 Group 2                                                             | // Group N Group 1                       |

| b. Edge Holdable SBT                                                             |                                          |

| COUT Group 1 Group 2 where N is up to 14.                                        | // Group N / Group 1                     |

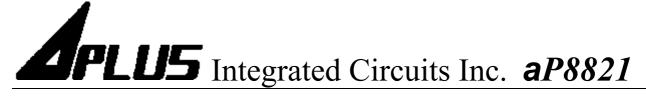

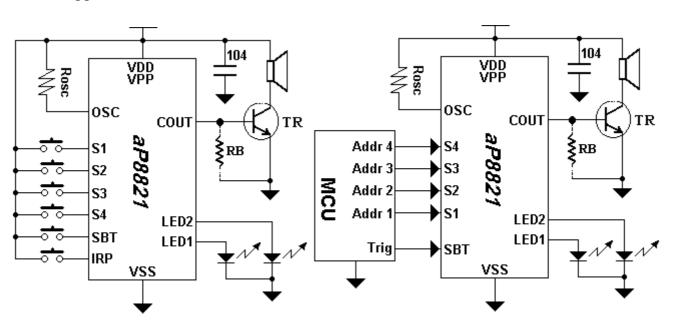

# ■ Application Circuits

# 1. Typical Application

Fig. 1 a Fig. 1 b

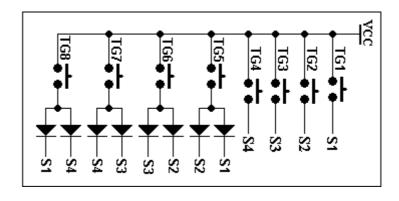

# 2. LED Application

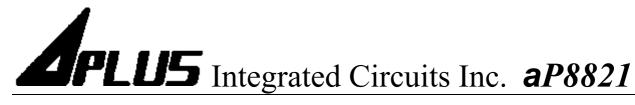

# 3. CPU Mode control

Fig. 2

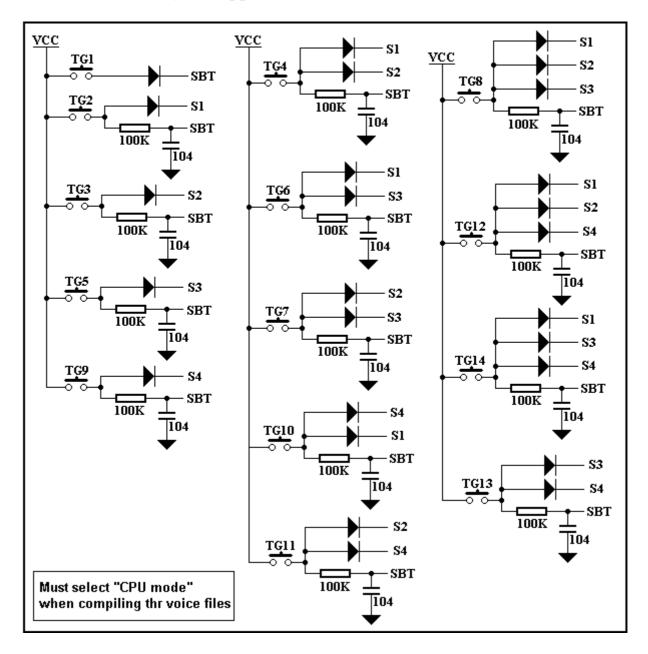

# 4. aP8821 Individually key application:

#### • API8208A ALONE KEY TRIGGER APPLICATION:

## 5. aP8821 & API8208A MCU CONTROL APPLICATION COMPARE:

|     | A DI 0200 A |    |    |                     |             | aD9921 (CDII Mada) |    |    |    |          |

|-----|-------------|----|----|---------------------|-------------|--------------------|----|----|----|----------|

|     | API8208A    |    |    | aP8821 ( CPU Mode ) |             |                    |    |    | T  |          |

|     | S4          | S3 | S2 | S1                  |             | S4                 | S3 | S2 | S1 | SBT      |

|     |             |    |    |                     | TG1         | 0                  | 0  | 0  | 0  | <u>_</u> |

| TG1 | 0           | 0  | 0  | 1                   | TG2         | 0                  | 0  | 0  | 1  | <u>_</u> |

| TG2 | 0           | 0  | 1  | 0                   | TG3         | 0                  | 0  | 1  | 0  | <u>_</u> |

| TG3 | 0           | 1  | 0  | 0                   | TG5         | 0                  | 1  | 0  | 0  | Ţ        |

| TG4 | 1           | 0  | 0  | 0                   | TG9         | 1                  | 0  | 0  | 0  | Ţ        |

| TG5 | 0           | 0  | 1  | 1                   | TG4         | 0                  | 0  | 1  | 1  | <u>_</u> |

| TG6 | 0           | 1  | 1  | 0                   | TG7         | 0                  | 1  | 1  | 0  | <u>_</u> |

| TG7 | 1           | 1  | 0  | 0                   | <b>TG13</b> | 1                  | 1  | 0  | 0  | <u>_</u> |

| TG8 | 1           | 0  | 0  | 1                   | <b>TG10</b> | 1                  | 0  | 0  | 1  | <u>_</u> |

|     |             |    |    |                     | TG4         | 0                  | 0  | 1  | 1  | <u>_</u> |

|     |             |    |    |                     | TG5         | 0                  | 1  | 0  | 0  | <u>_</u> |

|     |             |    |    |                     | TG8         | 0                  | 1  | 1  | 1  | <u>_</u> |

|     |             |    |    |                     | TG11        | 1                  | 0  | 1  | 0  | <u>_</u> |

|     |             |    |    |                     | TG12        | 1                  | 0  | 1  | 1  | <u>_</u> |

|     |             |    |    |                     | TG14        | 1                  | 1  | 0  | 1  | Ţ        |

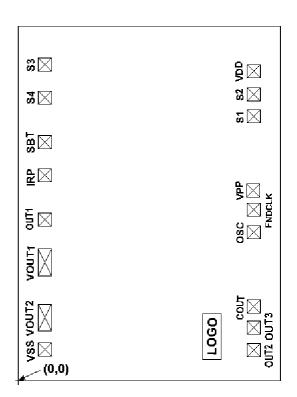

# APLUS Integrated Circuits Inc. aP8821

| Pin | Name       | X    | Y    |

|-----|------------|------|------|

| 1   | OUT1       | 180  | 1100 |

| 2   | VOUT1      | 180  | 800  |

| 3   | VOUT2      | 180  | 430  |

| 4   | VSS        | 180  | 213  |

| 5   | OUT2       | 1600 | 208  |

| 6   | OUT3       | 1600 | 360  |

| 7   | COUT       | 1600 | 507  |

| 8   | OSC        | 1600 | 1014 |

| 9   | VPP        | 1600 | 1300 |

| 10  | <b>S</b> 1 | 1600 | 1800 |

| 11  | S2         | 1600 | 1955 |

| 12  | VDD        | 1600 | 2114 |

| 13  | S3         | 180  | 2160 |

| 14  | S4         | 180  | 1932 |

| 15  | SBT        | 180  | 1630 |

| 16  | IRP        | 180  | 1402 |

Note: Substrate must be connected to  $V_{SS}$ Pad size =  $90um \times 90um$