# **Triple Differential Driver** With Output Pull-Down

AD8133

#### **FEATURES**

Triple high speed fully differential driver 225 MHz - 3 dB large signal bandwidth Easily drives 1.4 V p-p video signal into source-terminated 100 Ω UTP cable

1600 V/µs slew rate

Fixed internal gain of 2

Internal common-mode feedback network

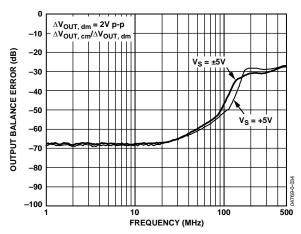

Output balance error -60 dB @ 50 MHz

Differential input and output

Differential-to-differential or single-ended-to-differential operation

Adjustable output common-mode voltage Output pull-down feature for line isolation Low distortion: 64 dB SFDR @ 10 MHz on 5 V supply,  $R_{L,dm} = 200 \Omega$

Low offset: 4 mV typical output referred on 5 V supply

Low power: 26 mA @ 5 V for three drivers Wide supply voltage range: +5 V to ±5 V

Available in space-saving packaging: 4 mm × 4 mm LFCSP

#### APPLICATIONS

KVM (keyboard-video-mouse) networking UTP (unshielded twisted pair) driving Differential signal multiplexing

#### **GENERAL DESCRIPTION**

The AD8133 is a major advancement beyond using discrete op amps for driving differential RGB signals over twisted pair cable. The AD8133 is a triple, low cost differential or singleended input to differential output driver, and each amplifier has a fixed gain of 2 to compensate for the attenuation of line termination resistors. The AD8133 is specifically designed for RGB signals but can be used for any type of analog signals or high speed data transmission. The AD8133 is capable of driving either Category 5 unshielded twisted pair (UTP) cable or differential printed circuit board transmission lines with minimal signal degradation.

The outputs of the AD8133 can be set to a low voltage state to be used with series diodes for line isolation, allowing easy differential multiplexing over the same twisted pair cable. The AD8133 driver can be used in conjunction with the AD8129 and AD8130 differential receivers.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

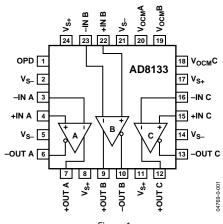

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

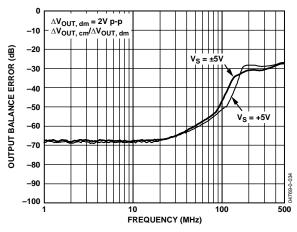

Figure 2. Output Balance vs. Frequency

Manufactured on Analog Devices' next generation XFCB bipolar process, the AD8133 has a large signal bandwidth of 225 MHz and a slew rate of 1600 V/µs. The AD8133 has an internal common-mode feedback feature that provides output amplitude and phase matching that is balanced to -60 dB at 50 MHz, suppressing harmonics and minimizing radiated electromagnetic interference (EMI).

The output common-mode level is easily adjustable by applying a voltage to the V<sub>OCM</sub> input pin. The V<sub>OCM</sub> input can also be used to transmit signals on the output common-mode voltages.

The AD8133 is available in a 24-lead LFCSP package and can operate over the temperature range of -40°C to +85°C.

## AD8133

## **TABLE OF CONTENTS**

| Specifications                                       | 3  |

|------------------------------------------------------|----|

| Absolute Maximum Ratings                             | 5  |

| Thermal Resistance                                   | 5  |

| ESD Caution                                          | 5  |

| Pin Configuration and Function Descriptions          | 6  |

| Typical Performance Characteristics                  | 7  |

| Theory of Operation                                  | 12 |

| Definition of Terms                                  | 12 |

| Analyzing an Application Circuit                     | 12 |

| Closed-Loop Gain                                     | 12 |

| Calculating an Application Circuit's Input Impedance | 13 |

| Input Common-Mode Voltage Range in Single-Supply     |    |

| Applications                                         | 13 |

|   | Driving a Capacitive Load                           | 13 |

|---|-----------------------------------------------------|----|

|   | Output Pull-Down (OPD)                              | 13 |

|   | Output Common-Mode Control                          | 13 |

| A | pplications                                         | 14 |

|   | Driving RGB Video Signals Over Category-5 UTP Cable | 14 |

|   | Output Pull-Down                                    | 15 |

|   | KVM Networks                                        | 15 |

|   | Layout and Power Supply Decoupling Considerations   | 15 |

|   | Amplifier-to-Amplifier Isolation                    | 15 |

|   | Exposed Paddle (EP)                                 | 15 |

| О | Outline Dimensions                                  | 16 |

|   | Ordering Guide                                      | 16 |

#### **REVISION HISTORY**

7/04—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{\text{S}} = \pm 5 \text{V}, V_{\text{OCM}} = 0 \text{ V @ 25°C}, R_{\text{L, dm}} = 200 \text{ }\Omega, \text{unless otherwise noted.} \\ T_{\text{MIN}} \text{ to } T_{\text{MAX}} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}.$

Table 1.

| Parameter                                          | Conditions                                                                                          | Min                   | Тур                         | Max                            | Unit   |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|-----------------------------|--------------------------------|--------|

| DIFFERENTIAL INPUT PERFORMANCE                     |                                                                                                     |                       |                             |                                |        |

| DYNAMIC PERFORMANCE                                |                                                                                                     |                       |                             |                                |        |

| –3 dB Small Signal Bandwidth                       | $V_0 = 0.2 \text{ V p-p}$                                                                           |                       | 450                         |                                | MHz    |

| –3 dB Large Signal Bandwidth                       | $V_0 = 2 \text{ V p-p}$                                                                             |                       | 225                         |                                | MHz    |

| Bandwidth for 0.1 dB Flatness                      | $V_0 = 0.2 \text{ V p-p}$                                                                           |                       | 60                          |                                | MHz    |

|                                                    | $V_0 = 2 V p-p$                                                                                     |                       | 55                          |                                | MHz    |

| Slew Rate                                          | $V_0 = 2 \text{ V p-p}, 25\% \text{ to } 75\%$                                                      |                       | 1600                        |                                | V/µs   |

| Settling Time to 0.1%                              | $V_0 = 2 \text{ V Step}$                                                                            |                       | 15                          |                                | ns     |

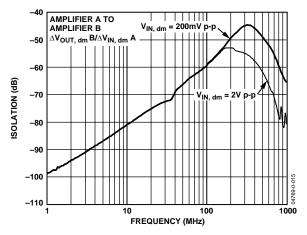

| Isolation between Amplifiers                       | f = 10 MHz, between Amplifiers A and B                                                              |                       | 81                          |                                | dB     |

| DIFFERENTIAL INPUT CHARACTERISTICS                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                             |                       |                             |                                |        |

| Input Common-Mode Voltage Range                    |                                                                                                     |                       | -5 to +5                    |                                | V      |

| Input Resistance                                   | Differential                                                                                        |                       | 1.5                         |                                | kΩ     |

| mpathesistance                                     | Single-Ended Input                                                                                  |                       | 1.13                        |                                | kΩ     |

| Input Capacitance                                  | Differential                                                                                        |                       | 1                           |                                | pF     |

| DC CMRR                                            | $\Delta V_{OUT, dm}/\Delta V_{IN, cm}$ , $\Delta V_{IN, cm} = \pm 1 \text{ V}$                      |                       | -50                         |                                | dB     |

| DIFFERENTIAL OUTPUT CHARACTERISTICS                | □ v ∪∪1, am/ □ v IN, cm, □ v IN, cm — □ I v                                                         |                       | - 50                        |                                | ub ub  |

| Differential Signal Gain                           | $\Delta V_{OUT, dm}/\Delta V_{IN, dm}; \Delta V_{IN, dm} = \pm 1 \text{ V}$                         | 1.925                 | 1.960                       | 2.000                          | V/V    |

| _                                                  |                                                                                                     | V <sub>S-</sub> + 1.9 | 1.900                       | 2.000<br>V <sub>S+</sub> – 1.6 | V      |

| Output Voltage Swing                               | Each Single-Ended Output                                                                            |                       | . 4                         |                                | _      |

| Output Offset Voltage                              | T 4- T                                                                                              | -24                   | +4                          | +24                            | mV     |

| Output Offset Drift                                | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                |                       | ±30                         |                                | μV/°C  |

| Output Balance Error                               | $\Delta V_{OUT, cm}/\Delta V_{IN, dm}$ , $\Delta V_{OUT, dm} = 2 \text{ V p-p, f} = 50 \text{ MHz}$ |                       | -60<br>-70                  |                                | dB     |

| (270)                                              | DC                                                                                                  |                       | <b>–70</b>                  | -58                            | dB     |

| Output Voltage Noise (RTO)                         | f = 1 MHz                                                                                           |                       | 25                          |                                | nV/√Hz |

| Output Short-Circuit Current                       |                                                                                                     |                       | 90                          |                                | mA     |

| V <sub>OCM</sub> to V <sub>O, cm</sub> PERFORMANCE |                                                                                                     |                       |                             |                                |        |

| V <sub>OCM</sub> DYNAMIC PERFORMANCE               |                                                                                                     |                       |                             |                                |        |

| –3 dB Bandwidth                                    | $\Delta V_{OCM} = 100 \text{ mV p-p}$                                                               |                       | 330                         |                                | MHz    |

| Slew Rate                                          | $V_{OCM} = -1 \text{ V to } +1 \text{ V, } 25\% \text{ to } 75\%$                                   |                       | 1000                        |                                | V/µs   |

| DC Gain                                            | $\Delta V_{OCM} = \pm 1 V$                                                                          | 0.980                 | 0.995                       | 1.005                          | V/V    |

| V <sub>OCM</sub> INPUT CHARACTERISTICS             |                                                                                                     |                       |                             |                                |        |

| Input Voltage Range                                |                                                                                                     |                       | ±3.1                        |                                | V      |

| Input Resistance                                   |                                                                                                     |                       | 70                          |                                | kΩ     |

| Input Offset Voltage                               |                                                                                                     | -15                   | -6                          | +15                            | mV     |

| Input Offset Voltage Drift                         | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                |                       | ±50                         |                                | μV/°C  |

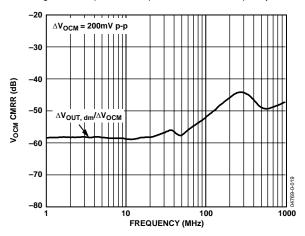

| DC CMRR                                            | $\Delta V_{OUT, dm}/\Delta V_{OCM}$ , $\Delta V_{OCM} = \pm 1 \text{ V}$                            |                       | -42                         |                                | dB     |

| POWER SUPPLY                                       |                                                                                                     |                       |                             |                                |        |

| Operating Range                                    |                                                                                                     | +4.5                  |                             | ±6                             | V      |

| Quiescent Current                                  |                                                                                                     |                       | 28                          | 29                             | mA     |

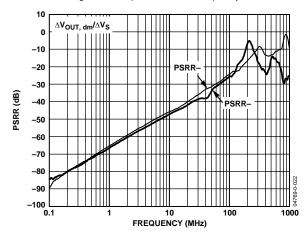

| PSRR                                               | $\Delta V_{OUT, dm}/\Delta V_S$ ; $\Delta V_S = \pm 1 \text{ V}$                                    |                       | -84                         | -76                            | dB     |

| OUTPUT PULL-DOWN PERFORMANCE                       |                                                                                                     |                       |                             |                                |        |

| OPD Input Low Voltage                              |                                                                                                     |                       | $V_{S-}$ to $V_{S+} - 4.15$ |                                | ٧      |

| OPD Input High Voltage                             |                                                                                                     |                       | $V_{S+} - 3.15$ to $V_{S+}$ |                                | V      |

| OPD Input Bias Current                             |                                                                                                     |                       | 67                          | 90                             | μΑ     |

| OPD Assert Time                                    |                                                                                                     |                       | 100                         |                                | ns     |

|                                                    | <b>i</b>                                                                                            | I                     |                             |                                |        |

| OPD De-Assert Time                                 |                                                                                                     |                       | 100                         |                                | ns     |

## AD8133

$V_{\text{S}} = 5 \text{ V}, V_{\text{OCM}} = 2.5 \text{ V} @ 25^{\circ}\text{C}, R_{\text{L,dm}} = 200 \ \Omega, unless \ otherwise \ noted. T_{\text{MIN}} \ to \ T_{\text{MAX}} = -40^{\circ}\text{C} \ to \ +85^{\circ}\text{C}.$

Table 2.

| Parameter                              | Conditions                                                                                          | Min                    | Тур                                       | Max                    | Unit   |

|----------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------|------------------------|--------|

| DIFFERENTIAL INPUT PERFORMANCE         |                                                                                                     |                        |                                           |                        |        |

| DYNAMIC PERFORMANCE                    |                                                                                                     |                        |                                           |                        |        |

| -3 dB Small Signal Bandwidth           | $V_0 = 0.2 \text{ V p-p}$                                                                           |                        | 400                                       |                        | MHz    |

| –3 dB Large Signal Bandwidth           | $V_0 = 2 V p-p$                                                                                     |                        | 200                                       |                        | MHz    |

| Bandwidth for 0.1 dB Flatness          | $V_0 = 0.2 \text{ V p-p}$                                                                           |                        | 50                                        |                        | MHz    |

| Slew Rate                              | $V_0 = 2 \text{ V p-p}, 25\% \text{ to } 75\%$                                                      |                        | 1400                                      |                        | V/µs   |

| Settling Time to 0.1%                  | $V_0 = 2 \text{ V Step}$                                                                            |                        | 14                                        |                        | ns     |

| Isolation Between Amplifiers           | f = 10 MHz, between Amplifiers A and B                                                              |                        | 75                                        |                        | dB     |

| DIFFERENTIAL INPUT CHARACTERISTICS     |                                                                                                     |                        |                                           |                        |        |

| Input Common-Mode Voltage Range        |                                                                                                     |                        | 0 to 5                                    |                        | V      |

| Input Resistance                       | Differential                                                                                        |                        | 1.5                                       |                        | kΩ     |

| •                                      | Single-Ended Input                                                                                  |                        | 1.13                                      |                        | kΩ     |

| Input Capacitance                      | Differential                                                                                        |                        | 1                                         |                        | рF     |

| DC CMRR                                | $\Delta V_{OUT, dm}/\Delta V_{IN, cm}$ , $\Delta V_{IN, cm} = \pm 1 \text{ V}$                      |                        | -50                                       |                        | dB     |

| DIFFERENTIAL OUTPUT CHARACTERISTICS    |                                                                                                     |                        |                                           |                        |        |

| Differential Signal Gain               | $\Delta V_{OUT, dm}/\Delta V_{IN, dm}$ ; $\Delta V_{IN, dm} = \pm 1 \text{ V}$                      | 1.925                  | 1.960                                     | 2.000                  |        |

| Output Voltage Swing                   | Each Single-Ended Output                                                                            | V <sub>S</sub> -+ 1.25 |                                           | V <sub>S+</sub> – 1.15 | V      |

| Output Offset Voltage                  | J                                                                                                   | -24                    | +4                                        | +24                    | mV     |

| Output Offset Drift                    | TMIN to TMAX                                                                                        |                        | ±30                                       |                        | μV/°C  |

| Output Balance Error                   | $\Delta V_{OUT, cm}/\Delta V_{IN, dm}$ , $\Delta V_{OUT, dm} = 2 \text{ V p-p, f} = 50 \text{ MHz}$ |                        | -60                                       |                        | dB     |

|                                        | DC                                                                                                  |                        | -70                                       | -58                    | dB     |

| Output Voltage Noise (RTO)             | f = 1 MHz                                                                                           |                        | 25                                        |                        | nV/√Hz |

| Output Short-Circuit Current           |                                                                                                     |                        | 90                                        |                        | mA     |

| V <sub>OCM</sub> PERFORMANCE           |                                                                                                     |                        |                                           |                        |        |

| V <sub>OCM</sub> DYNAMIC PERFORMANCE   |                                                                                                     |                        |                                           |                        |        |

| –3 dB Bandwidth                        | $\Delta V_{OCM} = 100 \text{ mV p-p}$                                                               |                        | 290                                       |                        | MHz    |

| Slew Rate                              | $V_{OCM} = -1 \text{ V to } +1 \text{ V, } 25\% \text{ to } 75\%$                                   |                        | 700                                       |                        | V/µs   |

| DC Gain                                | $\Delta V_{OCM} = \pm 1 \text{ V, } T_{MIN} \text{ to } T_{MAX}$                                    | 0.980                  | 0.995                                     | 1.005                  | V/V    |

| V <sub>OCM</sub> INPUT CHARACTERISTICS |                                                                                                     |                        |                                           |                        | -,-    |

| Input Voltage Range                    |                                                                                                     |                        | 1.25 to 3.85                              |                        | V      |

| Input Resistance                       |                                                                                                     |                        | 70                                        |                        | kΩ     |

| Input Offset Voltage                   |                                                                                                     | <b>-15</b>             | +2                                        | +15                    | mV     |

| Input Offset Voltage Drift             | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                |                        | ±50                                       |                        | μV/°C  |

| DC CMRR                                | $\Delta V_{O, dm}/\Delta V_{OCM}$ ; $\Delta V_{OCM} = \pm 1 \text{ V}$                              |                        | _42                                       |                        | dB     |

| POWER SUPPLY                           | Syanii Senii Senii                                                                                  |                        |                                           |                        |        |

| Operating Range                        |                                                                                                     | +4.5                   |                                           | ±6                     | V      |

| Quiescent Current                      |                                                                                                     |                        | 26                                        | 27                     | mA     |

| PSRR                                   | $\Delta V_{OUT, dm}/\Delta V_s$ ; $\Delta V_s = \pm 1 V$                                            |                        | -84                                       | -76                    | dB     |

| OUTPUT PULL-DOWN PERFORMANCE           | _ : 551/aiii _ : 5/ _ : 5                                                                           |                        |                                           |                        |        |

| OPD Input Low Voltage                  |                                                                                                     |                        | V <sub>S-</sub> to V <sub>S+</sub> - 3.85 |                        | V      |

| OPD Input High Voltage                 |                                                                                                     |                        | $V_{S+} - 2.85 \text{ to } V_{S+}$        |                        | v      |

| OPD Input Bias Current                 |                                                                                                     |                        | 63                                        | 80                     | μA     |

| OPD Assert Time                        |                                                                                                     |                        | 100                                       | 50                     | ns     |

| OPD De-Assert Time                     |                                                                                                     |                        | 100                                       |                        | ns     |

| Output Voltage When OPD Asserted       | Each Output, OPD Input @ Vs+                                                                        |                        | V <sub>s-</sub> + 0.79                    | V <sub>S-</sub> + 0.82 | V      |

| Output voltage villen Or D Asserted    | Lacir Output, Or D input @ VST                                                                      | L                      | v 5- ⊤ U./ J                              | 42- ±, 0.02            | v      |

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                                    | Rating          |

|----------------------------------------------|-----------------|

| Supply Voltage                               | 12 V            |

| All V <sub>OCM</sub>                         | ±V <sub>S</sub> |

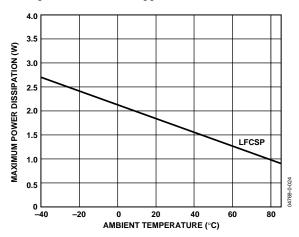

| Power Dissipation                            | See Figure 3    |

| Input Common-Mode Voltage                    | ±V <sub>S</sub> |

| Storage Temperature                          | −65°C to +125°C |

| Operating Temperature Range                  | −40°C to +85°C  |

| Lead Temperature Range<br>(Soldering 10 sec) | 300℃            |

| Junction Temperature                         | 150°C           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, i.e.,  $\theta_{JA}$  is specified for the device soldered in a circuit board in still air.

Table 4. Thermal Resistance with the Underside Pad Connected to the Plane

| Package Type/PCB Type | $\theta_{JA}$ | Unit |

|-----------------------|---------------|------|

| 24-Lead LFCSP/4-Layer | 70            | °C/W |

#### **Maximum Power Dissipation**

The maximum safe power dissipation in the AD8133 package is limited by the associated rise in junction temperature (T<sub>I</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the AD8133. Exceeding a junction temperature of 175°C for an extended period of time can result in changes in the silicon devices potentially causing failure.

The power dissipated in the package  $(P_{\rm D})$  is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the voltage between the supply pins  $(V_s)$  times the quiescent current (Is). The load current consists of differential and common-mode currents flowing to the loads, as well as currents flowing through the internal differential and common-mode feedback loops. The internal resistor tap used in the common-mode feedback loop places a  $4~{\rm k}\Omega$  differential load on the output. RMS output voltages should be considered when dealing with ac signals.

Airflow reduces  $\theta_{IA}$ . Also, more metal directly in contact with the package leads from metal traces, through holes, ground, and power planes reduces the  $\theta_{IA}$ . The exposed paddle on the underside of the package must be soldered to a pad on the PCB surface that is thermally connected to a copper plane in order to achieve the specified  $\theta_{IA}$ .

Figure 3 shows the maximum safe power dissipation in the package versus ambient temperature for the 24-lead LFCSP (70°C/W) package on a JEDEC standard 4-layer board with the underside paddle soldered to a pad that is thermally connected to a PCB plane.  $\theta_{JA}$  values are approximations.

Figure 3. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

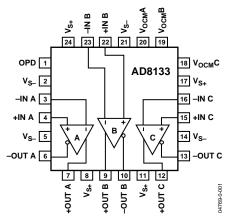

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. 24-Lead LFCSP

**Table 5. Pin Function Descriptions**

| Pin No.       | Mnemonic           | Description                                                                  |

|---------------|--------------------|------------------------------------------------------------------------------|

| 1             | OPD                | Output Pull-Down                                                             |

| 2, 5, 14, 21  | $V_{S-}$           | Negative Power Supply Voltage                                                |

| 3             | −IN A              | Inverting Input, Amplifier A                                                 |

| 4             | +IN A              | Noninverting Input, Amplifier A                                              |

| 6             | -OUT A             | Negative Output, Amplifier A                                                 |

| 7             | +OUT A             | Positive Output, Amplifier A                                                 |

| 8, 11, 17, 24 | $V_{S+}$           | Positive Power Supply Voltage                                                |

| 9             | +OUT B             | Positive Output, Amplifier B                                                 |

| 10            | –OUT B             | Negative Output, Amplifier B                                                 |

| 12            | +OUT C             | Positive Output, Amplifier C                                                 |

| 13            | -OUT C             | Negative Output, Amplifier C                                                 |

| 15            | +IN C              | Noninverting Input, Amplifier C                                              |

| 16            | −IN C              | Inverting Input, Amplifier C                                                 |

| 18            | V <sub>OCM</sub> C | Voltage Applied to This Pin Controls Output Common-Mode Voltage, Amplifier C |

| 19            | V <sub>OCM</sub> B | Voltage Applied to This Pin Controls Output Common-Mode Voltage, Amplifier B |

| 20            | V <sub>OCM</sub> A | Voltage Applied to This Pin Controls Output Common-Mode Voltage, Amplifier A |

| 22            | +IN B              | Noninverting Input, Amplifier B                                              |

| 23            | –IN B              | Inverting Input, Amplifier B                                                 |

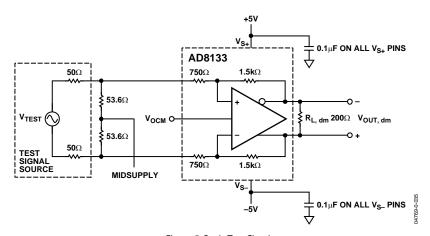

Figure 5. Basic Test Circuit

### TYPICAL PERFORMANCE CHARACTERISTICS

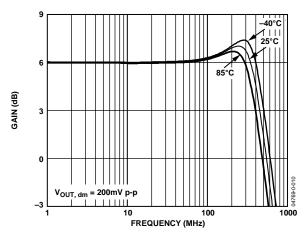

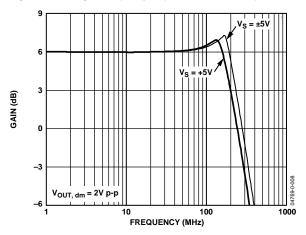

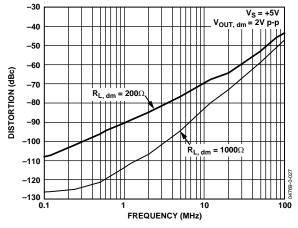

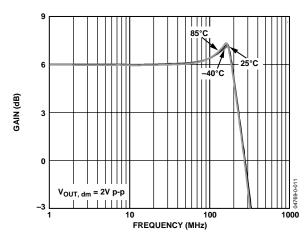

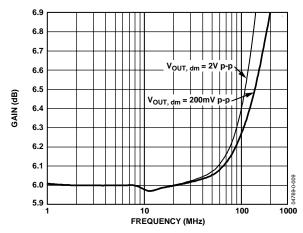

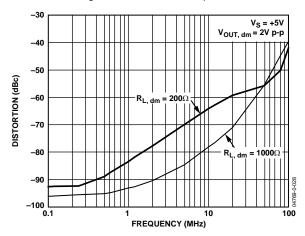

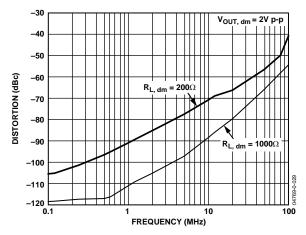

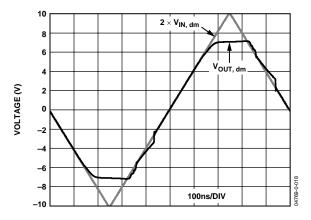

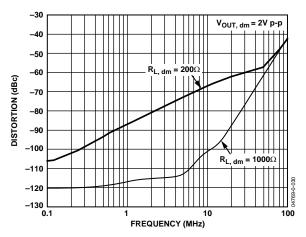

Unless otherwise noted,  $R_{L,dm} = 200~\Omega$ ,  $V_S = \pm 5~V$ ,  $T_A = 25^{\circ}C$ ,  $V_{OCM}A = V_{OCM}B = V_{OCM}C = 0~V$ . Refer to the basic test circuit in Figure 5 for the definition of terms.

Figure 6. Small Signal Frequency Response at Various Temperatures

Figure 7. Large Signal Frequency Response for Various Power Supplies

Figure 8. Second Harmonic Distortion at  $V_S = 5 V$  at Various Loads

Figure 9. Large Signal Frequency Response at Various Temperatures

Figure 10. 0.1 dB Flatness Response

Figure 11. Third Harmonic Distortion at  $V_S = 5 V$  at Various Loads

Figure 12. Second Harmonic Distortion at  $V_S = \pm 5 V$  at Various Loads

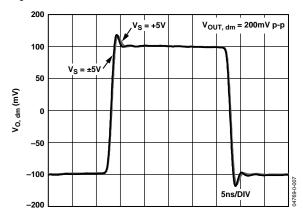

Figure 13. Small Signal Transient Response for Various Power Supply Voltages

Figure 14. Overdrive Recovery

Figure 15. Third Harmonic Distortion at  $V_S = \pm 5 V$  at Various Loads

Figure 16. Large Signal Transient Response for Various Power Supply Voltages

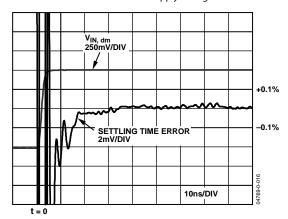

Figure 17. Settling Time (0.1%)

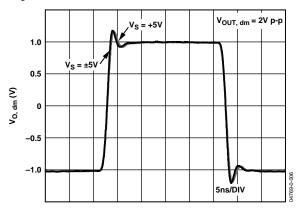

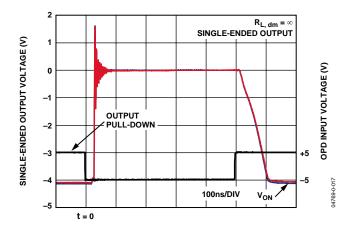

Figure 18. Output Pull-Down Response

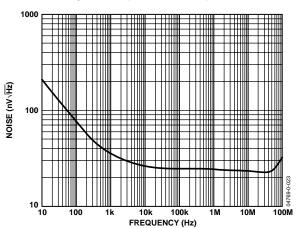

Figure 19. Output-Referred Voltage Noise vs. Frequency

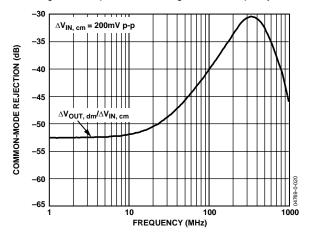

Figure 20. Common-Mode Rejection Ratio vs. Frequency

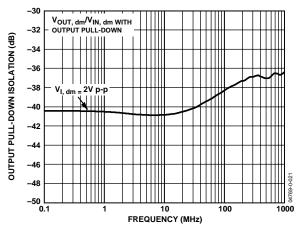

Figure 21. Output Pull-Down Isolation vs. Frequency

Figure 22. Output Balance vs. Frequency

Figure 23. Power Supply Rejection Ratio vs. Frequency

Figure 24. Amplifier-to-Amplifier Isolation vs. Frequency

Figure 25 V<sub>OCM</sub> CMRR vs. Frequency

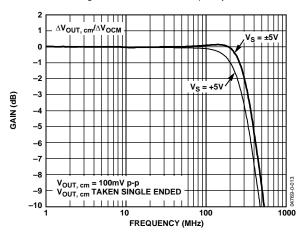

Figure 26. V<sub>OCM</sub> Frequency Response for Various Power Supply Voltages

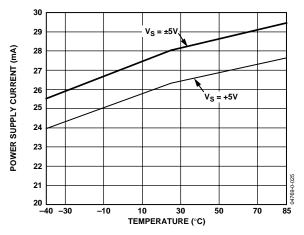

Figure 27. Power Supply Current vs. Temperature

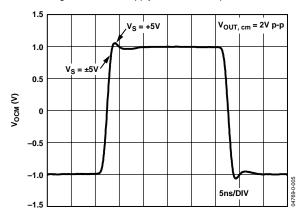

Figure 28. V<sub>OCM</sub> Large Signal Transient Response for Various Power Supply Voltages

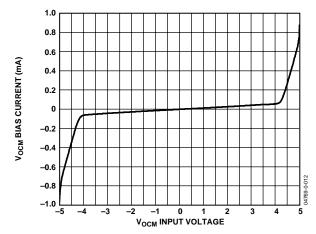

Figure 29. Vocm Bias Current vs. Vocm Input Voltage

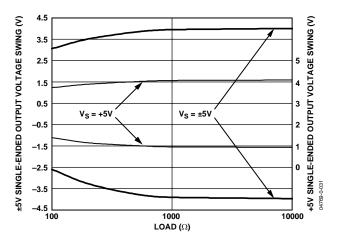

Figure 30. Output Saturation Voltage vs. Single-Ended Output Load

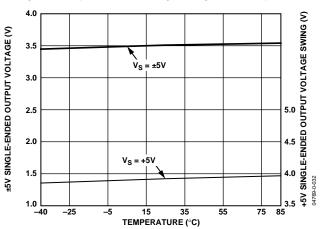

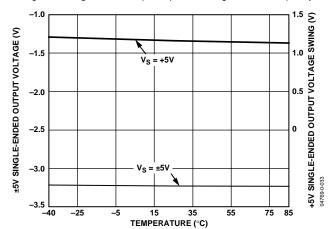

Figure 31. Positive Output Saturation Voltage vs. Temperature

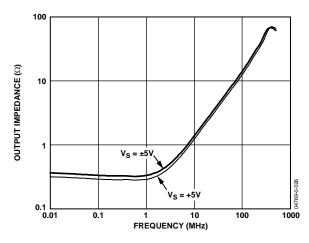

Figure 32. Single-Ended Output Impedance Magnitude vs. Frequency

Figure 33. Negative Output Saturation Voltage vs. Temperature

### THEORY OF OPERATION

Each differential driver in the AD8133 differs from a conventional op amp in that it has two outputs whose voltages move in opposite directions. Like an op amp, it relies on high open-loop gain and negative feedback to force these outputs to the desired voltages. The AD8133 drivers make it easy to perform single-ended-to-differential conversion, common-mode level shifting, and amplification of differential signals.

Previous differential drivers, both discrete and integrated designs, have been based on using two independent amplifiers and two independent feedback loops, one to control each of the outputs. When these circuits are driven from a single-ended source, the resulting outputs are typically not well balanced. Achieving a balanced output has typically required exceptional matching of the amplifiers and feedback networks.

DC common-mode level shifting has also been difficult with previous differential drivers. Level shifting has required the use of a third amplifier and feedback loop to control the output common-mode level. Sometimes, the third amplifier has also been used to attempt to correct an inherently unbalanced circuit. Excellent performance over a wide frequency range has proven difficult with this approach.

Each of the AD8133 drivers uses two feedback loops to separately control the differential and common-mode output voltages. The differential feedback, set by the internal resistors, controls only the differential output voltage. The internal common-mode feedback loop controls only the common-mode output voltage. This architecture makes it easy to arbitrarily set the output common-mode level by simply applying a voltage to the  $V_{\rm OCM}$  input. The output common-mode voltage is forced, by internal common-mode feedback, to equal the voltage applied to the  $V_{\rm OCM}$  input, without affecting the differential output voltage.

The AD8133 architecture results in outputs that are highly balanced over a wide frequency range without requiring external components or adjustments. The common-mode feedback loop forces the signal component of the output common-mode voltage to be zeroed. The result is nearly perfectly balanced differential outputs of identical amplitude that are exactly 180° apart in phase.

#### **DEFINITION OF TERMS**

#### **Differential Voltage**

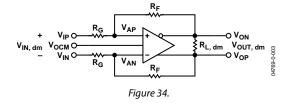

Differential voltage refers to the difference between two node voltages that are balanced with respect to each other. For example, in Figure 34 the output differential voltage (or equivalently output differential mode voltage) is defined as

$$V_{OUT,dm} = (V_{OP} - V_{ON})$$

Common-mode voltage refers to the average of two node voltages with respect to a common reference. The output common-mode voltage is defined as

$$V_{OUT,cm} = \frac{(V_{OP} + V_{ON})}{2}$$

#### **Output Balance**

Output balance is a measure of how well the differential output signals are matched in amplitude and how close they are to exactly 180° apart in phase. Balance is most easily determined by placing a well-matched resistor divider between the differential output voltage nodes and comparing the magnitude of the signal at the divider's midpoint with the magnitude of the differential signal. By this definition, output balance error is the magnitude of the change in output common-mode voltage divided by the magnitude of the change in output differential-mode voltage in response to a differential input signal.

$$Output \ Balance \ Error = \left| \frac{\Delta V_{OUT,cm}}{\Delta V_{OUT,dm}} \right|$$

#### **ANALYZING AN APPLICATION CIRCUIT**

The AD8133 uses high open-loop gain and negative feedback to force its differential and common-mode output voltages to minimize the differential and common-mode input error voltages. The differential input error voltage is defined as the voltage between the differential inputs labeled  $V_{\rm AP}$  and  $V_{\rm AN}$  in Figure 34. For most purposes, this voltage can be assumed to be zero. Similarly, the difference between the actual output common-mode voltage and the voltage applied to  $V_{\rm OCM}$  can also be assumed to be zero. Starting from these two assumptions, any application circuit can be analyzed.

#### **CLOSED-LOOP GAIN**

The differential mode gain of the circuit in Figure 34 can be described by the following equation.

$$\left| \frac{V_{OUT,dm}}{V_{IN,dm}} \right| = \frac{R_F}{R_G} = 2$$

where  $R_{\text{F}}$  = 1.5  $k\Omega$  and  $R_{\text{G}}$  = 750  $\Omega$  nominally.

# CALCULATING AN APPLICATION CIRCUIT'S INPUT IMPEDANCE

The effective input impedance of a circuit such as that in Figure 34 at  $V_{\rm IP}$  and  $V_{\rm IN}$  depends on whether the amplifier is being driven by a single-ended or differential signal source. For balanced differential input signals, the differential input impedance,  $R_{\rm IN, dm}$ , between the inputs  $V_{\rm IP}$  and  $V_{\rm IN}$  is simply

$$R_{IN,dm} = 2 \times R_G = 1.5 \text{k}\Omega$$

In the case of a single-ended input signal (for example, if  $V_{\rm IN}$  is grounded and the input signal is applied to  $V_{\rm IP}$ ), the input impedance becomes:

$$R_{IN,dm} = \left(\frac{R_G}{1 - \frac{R_F}{2 \times (R_G + R_F)}}\right) = 1.125 \,\mathrm{k}\Omega$$

The circuit's input impedance is effectively higher than it would be for a conventional op amp connected as an inverter because a fraction of the differential output voltage appears at the inputs as a common-mode signal, partially bootstrapping the voltage across the input resistor  $R_{\rm G}$ .

#### INPUT COMMON-MODE VOLTAGE RANGE IN SINGLE-SUPPLY APPLICATIONS

The inputs of the AD8133 are designed to facilitate level-shifting of ground referenced input signals on a single power supply. For a single-ended input, this would imply, for example, that the voltage at  $V_{\rm IN}$  in Figure 34 would be 0 V when the amplifier's negative power supply voltage was also set to 0 V.

It is important to ensure that the common-mode voltage at the amplifier inputs,  $V_{AP}$  and  $V_{AN}$ , stays within its specified range. Since voltages  $V_{AP}$  and  $V_{AN}$  are driven to be essentially equal by negative feedback, the amplifier's input common-mode voltage can be expressed as a single term,  $V_{ACM}$ .  $V_{ACM}$  can be calculated as follows

$$V_{ACM} = \frac{V_{OCM} + 2V_{ICM}}{3}$$

where  $V_{\text{\scriptsize ICM}}$  is the common-mode voltage of the input signal, i.e.,

$$V_{ICM} = \frac{V_{IP} + V_{IN}}{2} \; .$$

#### **DRIVING A CAPACITIVE LOAD**

A purely capacitive load can react with the output impedance of the AD8133 to reduce phase margin, resulting in high frequency ringing in the pulse response. The best way to minimize this effect is to place a small resistor in series with each of the amplifier's outputs to buffer the load capacitance.

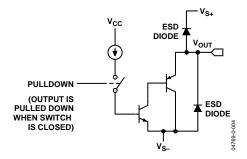

#### **OUTPUT PULL-DOWN (OPD)**

The AD8133 has an OPD pin that when pulled high significantly reduces the power consumed while simultaneously pulling the outputs to within less than 1 V of  $V_{S-}$  when used with series diodes (see the Applications section). The equivalent schematic of the output pull-down circuit is shown in Figure 35. (The ESD diodes shown in Figure 35 are for ESD protection and are distinct from the series diodes used with the output pull-down feature.) See Figure 18 and Figure 21 for the output pull-down transient and isolation performance plots. The threshold levels for the OPD pin are referenced to the positive power supply voltage and are presented in the Specifications tables. When the OPD pin is pulled high, the AD8133 enters the output low disable state.

Figure 35. Output Pull-Down Equivalent Circuit

#### **OUTPUT COMMON-MODE CONTROL**

The AD8133 allows the user to control each of the three common-mode output levels independently through the three  $V_{\text{OCM}}$  input pins. The  $V_{\text{OCM}}$  pins pass a signal to the common-mode output level of each of their respective amplifiers with 330 MHz of small signal bandwidth and an internally fixed gain of one. In this way, additional control and communication signals can be embedded on the common-mode levels as the user sees fit.

With no external circuitry, the level at the  $V_{\text{OCM}}$  input of each amplifier defaults to approximately midsupply. An internal resistive divider with an impedance of approximately  $100~k\Omega$  sets this level. To limit common-mode noise in dc common-mode applications, external bypass capacitors should be connected from each of the  $V_{\text{OCM}}$  input pins to ground.

### **APPLICATIONS**

# DRIVING RGB VIDEO SIGNALS OVER CATEGORY-5 UTP CABLE

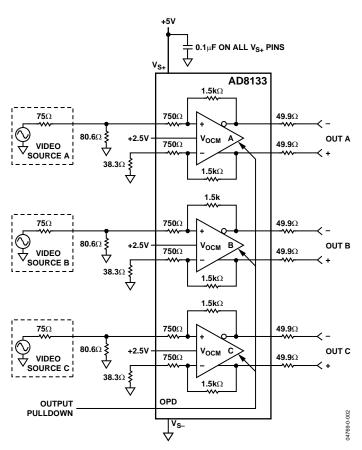

The foremost application of the AD8133 is driving RGB video signals over UTP cable in KVM networks. Single-ended video signals are easily converted to differential signals for transmission over the cable, and the internally fixed gain of 2 automatically compensates for the losses incurred by the source and load terminations. The common topologies used in KVM networks, such as daisy-chained, star, and point-to-point, are supported by the AD8133. Figure 36 shows the AD8133 in a triple single-ended-to-differential application when driven from a 75  $\Omega$  source, which is typical of how RGB video is driven over an UTP cable. In applications that use the OPD feature, the Schottky diodes are placed in series with each of the 49.9  $\Omega$  resistors in the outputs.

Figure 36. AD8133 in Single-Ended-to-Differential Application

#### **OUTPUT PULL-DOWN**

The output pull-down feature, when used in conjunction with series Schottky diodes, offers a convenient means to connect a number of AD8133 outputs together to form a video network. The OPD pin is a binary input that controls the state of the AD8133 outputs. Its binary input level is referenced to the most positive power supply (see the Specifications tables for the logic levels). When the OPD input is driven to its low state, the AD8133 output is enabled and operates in its normal fashion. In this state, the V<sub>OCM</sub> input can be used to provide a positive bias on the series diodes, allowing the AD8133 to transmit signals over the network. When the OPD input is driven to its high state, the outputs of the AD8133 are forced to a low voltage, irrespective of the level on the V<sub>OCM</sub> input, reverse-biasing the series diodes and thus presenting high impedance to the network. This feature allows a three-state output to be realized that maintains its high impedance state even when the AD8133 is not powered. This condition can occur in KVM networks where the AD8133s do not all reside in the same module, and some modules in the network are not powered.

It is recommended that the output pull-down feature only be used in conjunction with series diodes in such a way as to ensure that the diodes are reverse-biased when the output pull-down feature is asserted, since some loading conditions can prevent the output voltage from being pulled all the way down.

#### **KVM NETWORKS**

In daisy-chained KVM networks, the drivers are distributed along one cable and a triple receiver is located at one end. Schottky diodes in series with the driver outputs are biased such that the one driver that is transmitting video signals has its diodes forward-biased and the disabled drivers have their diodes reverse-biased. The output common-mode voltage, set by the  $V_{\text{OCM}}$  input, supplies the forward-biased voltage. When the output pull-down feature is asserted, the differential outputs are pulled to a low voltage, reverse-biasing the diodes.

In star networks, all cables radiate out from a central hub, which contains a triple receiver. The series diodes are all located at the receiver in the star network. Only one ray of the star is transmitting at a given time, and all others are isolated by the reverse-biased diodes. Diode biasing is controlled in the same way as in the daisy-chained network.

In the daisy-chained and star networks that use diodes for isolation, return paths are required for the common-mode currents that flow through the series diodes. A common-mode tap can be implemented at each receiver by splitting the 100  $\Omega$  termination resistor into two 50  $\Omega$  resistors in series. The diode currents are routed from the tap between the 50  $\Omega$  resistors back to the respective transmitters over one of the wires of the fourth twisted pair in the UTP cable. Series resistors in the common-mode return path are generally required to set the desired diode current.

In point-to-point networks, there is one transmitter and one receiver per cable, and the switching is generally implemented with a crosspoint switch. In this case, there is no need to use diodes or the output pull-down feature.

Diode and crosspoint switching are by no means the only type of switching that can be used with the AD8133. Many other types of mechanical, electromechanical, and electronic switches can be used.

# LAYOUT AND POWER SUPPLY DECOUPLING CONSIDERATIONS

Standard high speed PCB layout practices should be adhered to when designing with the AD8133. A solid ground plane is recommended and good wideband power supply decoupling networks should be placed as close as possible to the supply pins. Small surface-mount ceramic capacitors are recommended for these networks, and tantalum capacitors are recommended for bulk supply decoupling.

#### **AMPLIFIER-TO-AMPLIFIER ISOLATION**

The least amount of isolation between the three amplifiers exists between Amplifier A and Amplifier B. This is therefore viewed as the worst-case isolation and is what is reflected in the Specifications tables and Typical Performance Characteristics. Refer to the Basic Test Circuit shown in Figure 5 for the test conditions.

#### **EXPOSED PADDLE (EP)**

The LFCSP-24 package has an exposed paddle on the underside of its body. In order to achieve the specified thermal resistance, it must have a good thermal connection to one of the PCB planes. The exposed paddle must be soldered to a pad on the top of the board that is connected to an inner plane with several thermal vias.

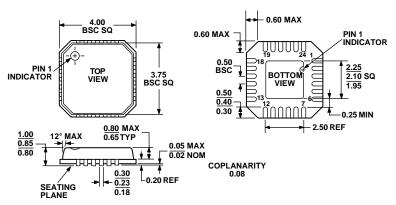

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-220-VGGD-2

Figure 37. 24-Lead Lead Frame Chip Scale Package [LFCSP], 4 mm× 4 mm (CP-24) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                        | Temperature Package | Package Description | Package Outline |

|------------------------------|---------------------|---------------------|-----------------|

| AD8133ACP-REEL               | −40°C to +85°C      | 24-Lead LFCSP       | CP-24           |

| AD8133ACP-REEL7              | -40°C to +85°C      | 24-Lead LFCSP       | CP-24           |

| AD8133ACPZ-REEL <sup>1</sup> | -40°C to +85°C      | 24-Lead LFCSP       | CP-24           |

| AD8133ACPZ-REEL71            | -40°C to +85°C      | 24-Lead LFCSP       | CP-24           |

<sup>&</sup>lt;sup>1</sup> Z = Pb-free part.