# **TUSB3410**USB To Serial Port Controller

# Data Manual

June 2002 MSP USB

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

## **Contents**

| Se | ection       | Title           |                                                                              |     |  |

|----|--------------|-----------------|------------------------------------------------------------------------------|-----|--|

| 1  | Introduction |                 |                                                                              | 1–1 |  |

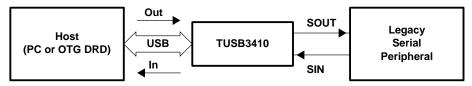

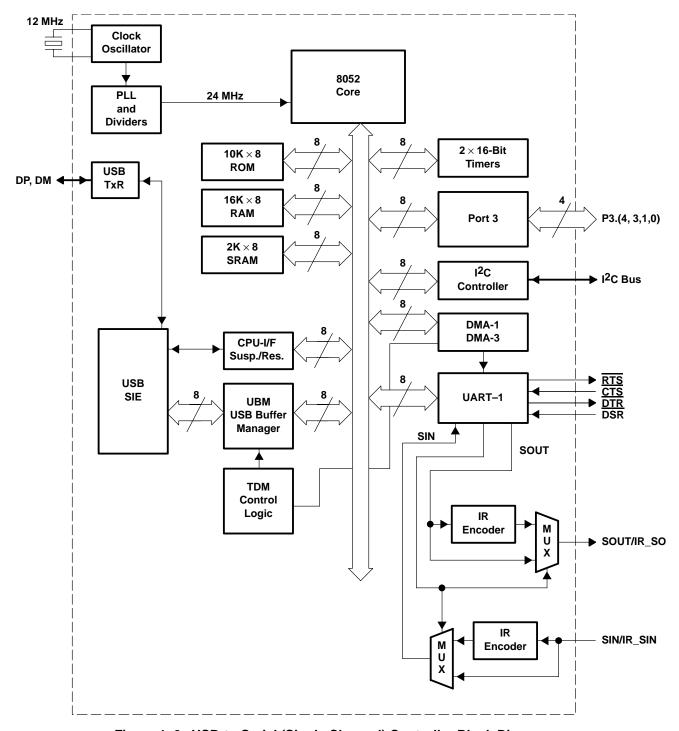

|    | 1.1          | Controlle       | r Description                                                                | 1–1 |  |

| 2  | Main I       | Features        |                                                                              | 2–1 |  |

|    | 2.1          | USB Fea         | itures                                                                       | 2–1 |  |

|    | 2.2          | General         | Features                                                                     | 2–1 |  |

|    | 2.3          | Enhance         | d UART Features                                                              | 2–1 |  |

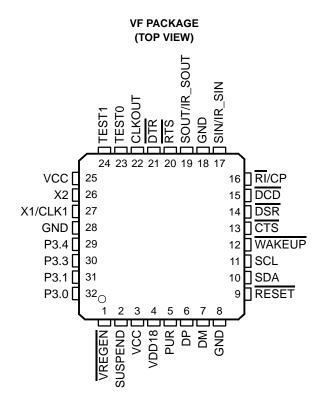

|    | 2.4          | Pinout In       | formation                                                                    | 2–2 |  |

| 3  | Detail       | ed Contro       | oller Description                                                            | 3–1 |  |

|    | 3.1          | Operating       | g Modes                                                                      | 3–1 |  |

|    | 3.2          | <b>USB</b> Inte | rface Configuration                                                          | 3–1 |  |

|    |              | 3.2.1           | External Memory Case                                                         | 3–1 |  |

|    |              | 3.2.2           | Host Download Case                                                           | 3–1 |  |

|    | 3.3          | USB Data        | a Movement                                                                   | 3–1 |  |

|    | 3.4          | Serial Po       | ort Setup                                                                    | 3–1 |  |

|    | 3.5          | Serial Po       | ort Data Modes                                                               | 3–2 |  |

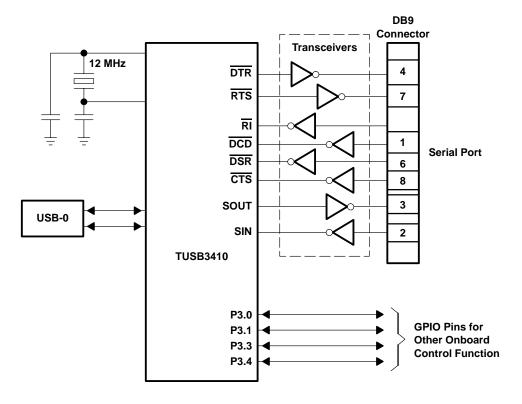

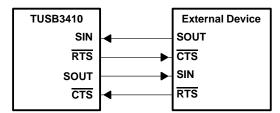

|    |              | 3.5.1           | RS-232 Data Mode                                                             | 3–2 |  |

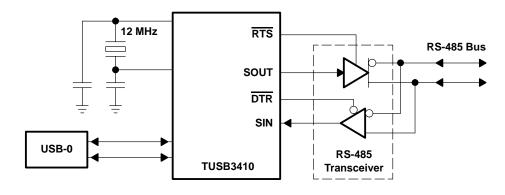

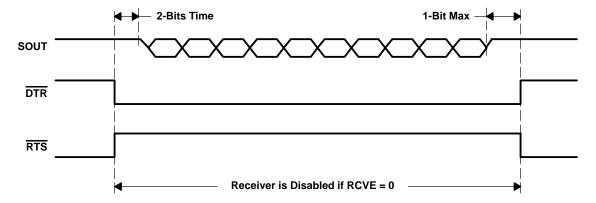

|    |              | 3.5.2           | RS-485 Data Mode                                                             | 3–2 |  |

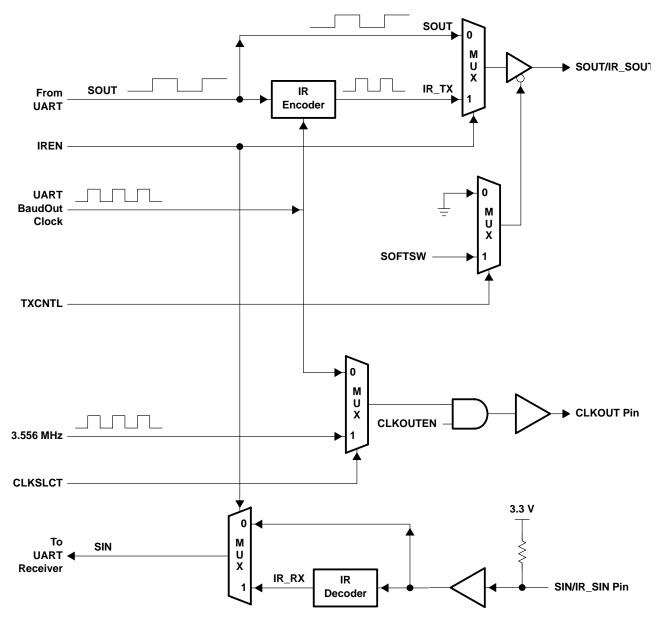

|    |              | 3.5.3           | IrDA Data Mode                                                               | 3–2 |  |

| 4  | MCU I        | Memory M        | flap (Internal Operation)                                                    | 4–1 |  |

|    | 4.1          | Miscellan       | neous Registers                                                              | 4–2 |  |

|    |              | 4.1.1           | ROMS: ROM Shadow Configuration Register (Addr:FF90)                          | 4–2 |  |

|    |              | 4.1.2           | Boot Operation (MCU Firmware Loading)                                        | 4–2 |  |

|    |              | 4.1.3           | WDCSR: Watchdog Timer, Control, and Status Register (Addr:FF93)              | 4–3 |  |

|    | 4.2          | Buffers +       | · Ì/O RAM Map                                                                |     |  |

|    | 4.3          |                 | Descriptor Block (EDB–1 to EDB–3)                                            |     |  |

|    |              | 4.3.1           | OEPCNF_n: Output Endpoint Configuration (n = 1 to 3) (Addr:FF08, FF10, FF18) | 4–6 |  |

|    |              | 4.3.2           | OEPBBAX_n: Output Endpoint X-Buffer Base Address (n = 1 to 3)                |     |  |

|    |              | 4.3.3           | OEPBCTX_n: Output Endpoint X Byte Count (n = 1 to 3)                         | 4–7 |  |

|    |              | 4.3.4           | OEPBBAY_n: Output Endpoint Y-Buffer Base Address (n = 1 to 3)                | 4–7 |  |

|    |              | 4.3.5           | OEPBCTY_n: Output Endpoint Y-Byte Count (n = 1 to 3)                         | 4–7 |  |

|    |              | 4.3.6           | OEPSIZXÝ_n: Output Endpoint X-/Y-Buffer Size (n =1 to 3)                     | 4–8 |  |

|   |      | 4.3.7    | IEPCNF_n: Input Endpoint Configuration (n = 1 to 3) (Addr:FF48, FF50, FF58) | 4–8  |

|---|------|----------|-----------------------------------------------------------------------------|------|

|   |      | 4.3.8    | IEPBBAX_n: Input Endpoint X-buffer Base Address (n = 1 to 3)                | 4–8  |

|   |      | 4.3.9    | IEPBCTX_n: Input Endpoint X-Byte Count (n = 1 to 3)                         | 4–9  |

|   |      | 4.3.10   | IEPBBAY_n: Input Endpoint Y-Buffer Base Address (n = 1 to 3)                | 4–9  |

|   |      | 4.3.11   | IEPBCTY_n: Input Endpoint Y-Byte Count (n = 1 to 3)                         | 4–9  |

|   |      | 4.3.12   | IEPSIZXY_n: Output Endpoint X-/Y-Buffer Size (n = 1 to 3)                   |      |

|   | 4.4  | Endpoint | -0 Descriptor Registers                                                     | 4–10 |

|   |      | 4.4.1    | IEPCNFG_0: Input Endpoint-0 Configuration Register (Addr:FF80)              |      |

|   |      | 4.4.2    | IEPBCNT_0: Input Endpoint-0 Byte Count Register (Addr:FF81)                 | 4–10 |

|   |      | 4.4.3    | OEPCNFG_0: Output Endpoint-0 Configuration Register (Addr:FF82)             |      |

|   |      | 4.4.4    | OEPBCNT_0: Output Endpoint-0 Byte Count Register (Addr:FF83)                |      |

| 5 | USB. |          |                                                                             | 5–1  |

|   | 5.1  | USB Reg  | gisters                                                                     |      |

|   |      | 5.1.1    | FUNADR: Function Address Register (Addr:FFFF)                               | 5–1  |

|   |      | 5.1.2    | USBSTA: USB Status Register (Addr:FFFE)                                     | 5–1  |

|   |      | 5.1.3    | USBMSK: USB Interrupt Mask Register (Addr:FFFD)                             | 5–2  |

|   |      | 5.1.4    | USBCTL: USB Control Register (Addr:FFFC)                                    | 5–3  |

|   |      | 5.1.5    | MODECNFG: Mode Configuration Register (Addr:FFFB)                           | 5–4  |

|   |      | 5.1.6    | Vendor ID/Product ID                                                        | 5–4  |

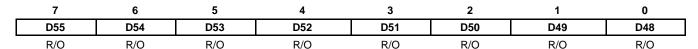

|   |      | 5.1.7    | SERNUM7: Device Serial Number Register (Byte 7) (Addr:FFEF)                 | 5–4  |

|   |      | 5.1.8    | SERNUM6: Device Serial Number Register (Byte 6) (Addr:FFEE)                 | 5–5  |

|   |      | 5.1.9    | SERNUM5: Device Serial Number Register (Byte 5) (Addr:FFED)                 | 5–5  |

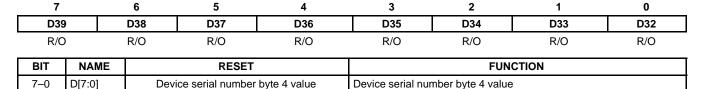

|   |      | 5.1.10   | SERNUM4: Device Serial Number Register (Byte 4) (Addr:FFEC)                 | 5–6  |

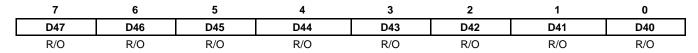

|   |      | 5.1.11   | SERNUM3: Device Serial Number Register (Byte 3) (Addr:FFEB)                 | 5–6  |

|   |      | 5.1.12   | SERNUM2: Device Serial Number Register (Byte 2) (Addr:FFEA)                 | 5–6  |

|   |      | 5.1.13   | SERNUM1: Device Serial Number Register (Byte 1) (Addr:FFE9)                 | 5–6  |

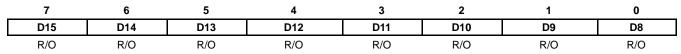

|   |      | 5.1.14   | SERNUM0: Device Serial Number Register (Byte 0) (Addr:FFE8)                 | 5–7  |

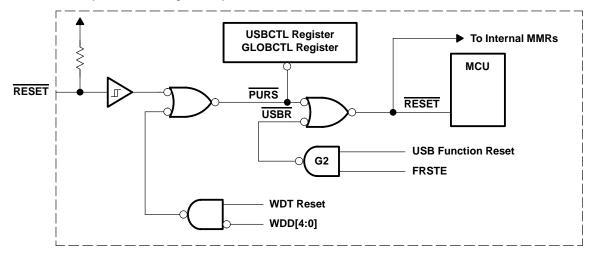

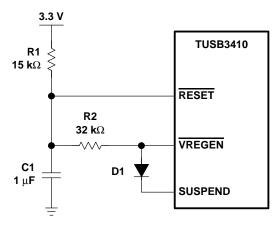

|   |      | 5.1.15   | Function Reset And Power-Up Reset Interconnect                              | 5–7  |

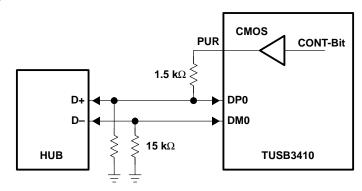

|   |      | 5.1.16   | Pullup Resistor Connect/Disconnect                                          | 5–8  |

| 6 | DMA    | Controller | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6–1        |

|---|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   | 6.1    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6–1        |

|   |        | 6.1.1      | DMACDR1: DMA Channel Definition Register (UART Transr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nit<br>5–2 |

|   |        | 6.1.2      | DMACSR1: DMA Control And Status Register (UART Trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   |        | 6.1.3      | DMACDR3: DMA Channel Definition Register (UART Received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|   |        | 6.1.4      | DMACSR3: DMA Control And Status Register (UART Recei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   | 6.2    | Bulk Data  | a I/O Using the EDB (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|   |        | 6.2.1      | IN Transaction (TUSB3410 to Host)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|   |        | 6.2.2      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6–6        |

| 7 | UART   |            | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7–1        |

|   | 7.1    | UART R     | egisters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7–1        |

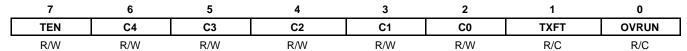

|   |        | 7.1.1      | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7–1        |

|   |        | 7.1.2      | The state of the s | 7–1        |

|   |        | 7.1.3      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7–2        |

|   |        | 7.1.4      | FCRL: UART Flow Control Register (Addr:FFA3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7–3        |

|   |        | 7.1.5      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7–4        |

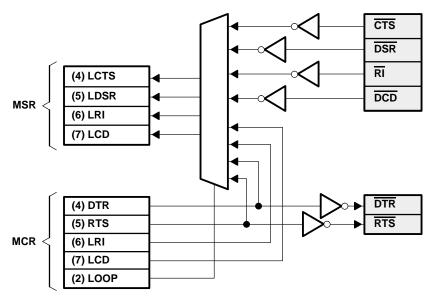

|   |        | 7.1.6      | MCR: Modem-Control Register (Addr:FFA4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7–5        |

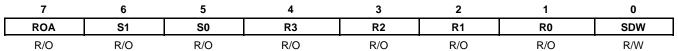

|   |        | 7.1.7      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7–6        |

|   |        | 7.1.8      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7–7        |

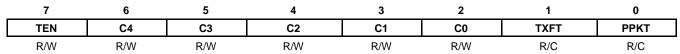

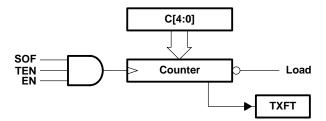

|   |        | 7.1.9      | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7–8        |

|   |        | 7.1.10     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7–8        |

|   |        | 7.1.11     | Baud-rate Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7–8        |

|   |        | 7.1.12     | XON: Xon Register (Addr:FFA9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|   |        | 7.1.13     | XOFF: Xoff Register (Addr:FFAA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   |        | 7.1.14     | MASK: UART Interrupt-Mask Register (Addr:FFAB) 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

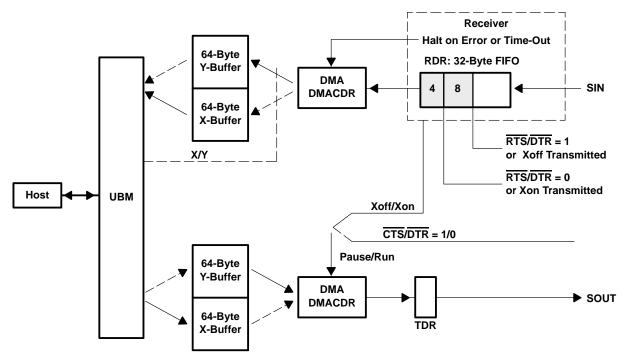

|   | 7.2    |            | ata Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|   |        | 7.2.1      | Receiver Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|   |        | 7.2.2      | Hardware Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|   |        | 7.2.3      | Auto RTS (Receiver Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|   |        | 7.2.4      | Auto CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|   |        | 7.2.5      | Xon/Xoff Receiver Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|   |        | 7.2.6      | Xon/Xoff Transmit Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| 8 | Expar  |            | O Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |