SLIS110 - APRIL 200

#### features

- **Dual-Channel Knock Sensor Interface**

- **Programmable Input Frequency Prescaler** (OSC<sub>IN</sub>)

- **Serial Interface With Microprocessor (SPI)**

- **Programmable Gain**

- **Programmable Band-Pass Filter Center** Frequency

- **External Clock Frequencies up to 24 MHz** - 4, 5, 6, 8, 10, 12, 16, 20, and 24 MHz

- **Programmable Integrator Time Constants**

- Operating Temperature Range -40°C to 125°C

#### applications

- **Engine Knock Detector Signal Processing**

- **Analog Signal Processing With Filter** Characteristics

# **DW PACKAGE** (TOP VIEW)

|                        |    |    | _          |       |

|------------------------|----|----|------------|-------|

| V <sub>DD</sub> $\Box$ | 1  | 20 |            | CH1P  |

| GND 🖂                  | 2  | 19 |            | CH1N  |

| V <sub>ref</sub> □□    | 3  | 18 |            | CH1FB |

| OUT 🗀                  | 4  | 17 | ·          | CH2FB |

| NC 🗀                   | 5  | 16 |            | CH2N  |

| NC 🗀                   | 6  | 15 | ; <b> </b> | CH2P  |

| INT/HOLD               | 7  | 14 |            | TEST  |

| CS □□                  | 8  | 13 |            | SCLK  |

| XIN 🗀                  | 9  | 12 |            | SDI   |

| XOUT 🗀                 | 10 | 11 |            | SDO   |

|                        |    |    |            |       |

# description

The TPIC8101 is a dual-channel signal processing IC for detection of premature detonation in combustion engine. The two sensor channels are selectable through the SPI bus. The knock sensor typically provides an electrical signal to the amplifier inputs. The sensed signal is processed through a programmable band-pass filter to extract the frequency of interest (engine knock or ping signals). The band-pass filter eliminates any engine background noise associated with combustion. The engine background noise is typically low in amplitude compared to the predetonation noise.

The detected signal is full-wave rectified and integrated by use of the INT/HOLD signal. The digital output from the integration stage is either converted to an analog signal, passed through an output buffer, or be read directly by the SPI.

This analog buffered output may be interfaced to an A/D converter and read by the microprocessor. The digital output may be directly interfaced to the microprocessor.

The data from the A/D enables the system to analyze the amount of retard timing for the next spark ignition timing cycle.

With the microprocessor closed-loop system, advancing and retarding the spark timing optimize the load/RPM conditions for a particular engine (data stored in RAM).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

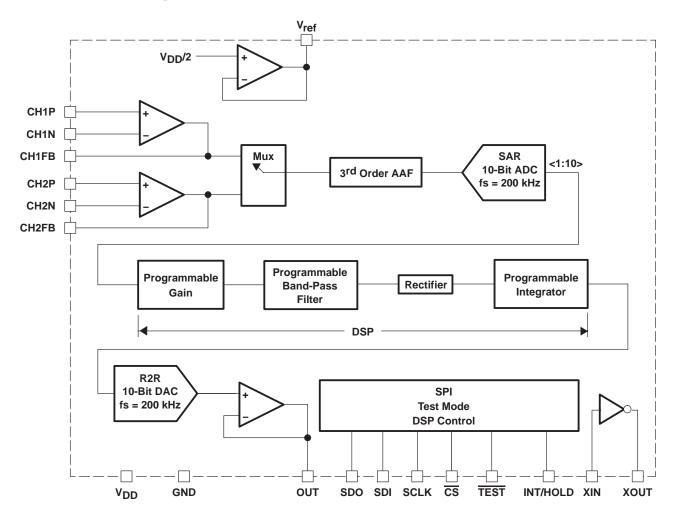

#### functional block diagram

# **Terminal Functions**

|                 | TERM | INAL                               |                                                                             |  |

|-----------------|------|------------------------------------|-----------------------------------------------------------------------------|--|

| NAME            | NO.  | TERMINAL TYPE<br>(PULLUP/PULLDOWN) | DESCRIPTION                                                                 |  |

| $V_{DD}$        | 1    | I                                  | 5-V input supply                                                            |  |

| GND             | 2    | I                                  | Ground connection                                                           |  |

| Vref            | 3    | 0                                  | Supply reference generator with external bypass capacitor                   |  |

| OUT             | 4    | 0                                  | Buffered integrator output                                                  |  |

| NC <sup>†</sup> | 5, 6 |                                    | No connection                                                               |  |

| INT/HOLD        | 7    | I / Pulldown                       | Selectable for integrate (high) or hold (low) mode (with internal pulldown) |  |

| CS              | 8    | I / Pullup                         | Chip select for SPI communications (active low with internal pullup)        |  |

| XIN             | 9    | I                                  | Inverter input for oscillator                                               |  |

| XOUT            | 10   | 0                                  | Inverter output for oscillator                                              |  |

| SDO             | 11   | 0                                  | Serial data output for SPI bus                                              |  |

| SDI             | 12   | I / Pullup                         | Serial data input line                                                      |  |

| SCLK            | 13   | I / Pullup                         | SPI clock                                                                   |  |

| TEST            | 14   | I / Pullup                         | Test mode (active low), open for normal operation                           |  |

| CH2P            | 15   | I                                  | Positive input for amplifier #2                                             |  |

| CH2N            | 16   | I                                  | Negative input for amplifier #2                                             |  |

| CH2FB           | 17   | 0                                  | Output of amplifier #2, for feedback connection                             |  |

| CH1FB           | 18   | 0                                  | Output of amplifier #1, for feedback connection                             |  |

| CH1N            | 19   | I                                  | Negative input for amplifier #1                                             |  |

| CH1P            | 20   | I                                  | Positive input for amplifier #1                                             |  |

<sup>†</sup> These terminals are to be used for test purposes only and are no connected in the system application. No signal traces should be connected to the NC terminals.

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Regulated input voltage (see Notes 1 and 2), V <sub>DD</sub>                                       |

|----------------------------------------------------------------------------------------------------|

| Output voltage (see Notes 1 and 2), VO0.3 V to 7 V                                                 |

| Input voltage (see Notes 1 and 2), V <sub>IN</sub>                                                 |

| DC input current on terminals CH1P, CH1N, CH2P, and CH2N (see Notes 1 and 2), I <sub>IN</sub> 2 mA |

| DC input voltage on terminals CH1P, CH1N, CH2P and CH2N (see Notes 1 and 2), V <sub>DCIN</sub>     |

| Thermal impedance junction to ambient, $\theta_{JA}$                                               |

| Continuous power dissipation, P <sub>D</sub>                                                       |

| Electrostatic discharge susceptibility (see Note 3), V <sub>(HBMESD)</sub>                         |

| Operating ambient temperature range, T <sub>A</sub> —40°C to 125°C                                 |

| Storage temperature range, T <sub>stq</sub> 65°C to 150°C                                          |

| Lead temperature (soldering, 10 sec), T <sub>LEAD</sub>                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. Absolute negative voltage on these terminals is not to go below -0.5 V.

- 3. The human body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each terminal.

# recommended operating conditions

|                                                                           | MIN  | MAX                        | UNITS |

|---------------------------------------------------------------------------|------|----------------------------|-------|

| Regulated input voltage, V <sub>DD</sub>                                  | -0.3 | 5.5                        | V     |

| Output voltage, VO                                                        | -0.3 | 5.5                        | V     |

| Input voltage, V <sub>IN</sub>                                            | 0.05 | V <sub>DD</sub> – 0.05     | V     |

| DC input current on terminals CH1P, CH1N, CH2P, and CH2N, I <sub>IN</sub> | -1   | 1                          | μΑ    |

| DC input voltage on terminals CH1P, CH1N, CH2P, and CH2N, VDCIN           |      | Vref, (V <sub>DD</sub> /2) | V     |

| Continuous power dissipation, PD                                          |      | 100                        | mW    |

NOTES: 1. All voltage values are with respect to GND.

# dc electrical characteristics, $V_{DD}$ = 5 V $\pm 5\%$ , input frequency before prescaler = 4 MHz to 20 MHz ( $\pm 0.5\%$ ), $T_A$ = $-40^{\circ}$ C to 125°C (unless otherwise specified)

|                        | PARAMETER                                              | TEST CONDITIONS                                                                                     | MIN                       | TYP                       | MAX                       | UNITS |

|------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| I <sub>DD(Q)</sub>     | Quiescent current                                      | V <sub>DD</sub> = 5 V                                                                               |                           | 7.5                       |                           | mA    |

| I <sub>DD(OP)</sub>    | Operating current                                      | V <sub>DD</sub> = 5 V, XIN = 8 MHz                                                                  |                           |                           | 20                        | mA    |

| V <sub>mid0</sub>      | Midpoint voltage                                       | V <sub>DD</sub> = 5 V, I <sub>Source</sub> = 2 mA                                                   | 2.3                       | 2.5                       | 2.55                      | V     |

| V <sub>mid1</sub>      | Midpoint voltage                                       | V <sub>DD</sub> = 5 V, I <sub>Sink</sub> = 2 mA                                                     | 2.4                       | 2.5                       | 2.7                       | V     |

| V <sub>mid2</sub>      | Midpoint voltage                                       | V <sub>DD</sub> = 5 V, I <sub>L</sub> = 0 mA                                                        | 2.4                       | 2.5                       | 2.6                       | V     |

| Rpull0                 | Internal pullup resistor CS, SDI, SCLK, TEST           | V <sub>IN</sub> = GND                                                                               | 30                        |                           |                           | kΩ    |

| Rpull1                 | Internal pulldown resistor INT/HOLD                    | $V_{IN} = V_{DD}$                                                                                   | 20                        |                           |                           | kΩ    |

| l <sub>lkg</sub>       | Input leakage current CS, SDI, SCLK, INT/HOLD, TEST    | Measured at GND and $V_{DD}$ ,<br>$V_{DD} = 5.5 V = V_{IN}$                                         |                           |                           | ±3                        | μΑ    |

| V <sub>IL</sub>        | Low-level input voltage INT/HOLD, CS, TEST, SDI, SCLK  |                                                                                                     |                           |                           | 30% of<br>V <sub>DD</sub> |       |

| VIH                    | High-level input voltage INT/HOLD, CS, TEST, SDI, SCLK |                                                                                                     | 70% of<br>V <sub>DD</sub> |                           |                           |       |

| VOL                    | Low-level output voltage SDO                           | I <sub>Sink</sub> = 4 mA, V <sub>DD</sub> = 5 V                                                     |                           |                           | 0.7                       | V     |

| Vон                    | High-level output voltage SDO                          | I <sub>Source</sub> = 100 μA, V <sub>DD</sub> = 5 V                                                 | 4.4                       |                           |                           | V     |

| I <sub>lkg(OL)</sub>   | Low-level leakage current SDO                          | Measured at GND and $V_{DD} = 5 \text{ V}$ , SDO in high impedance                                  | -10                       |                           | 10                        | μΑ    |

| VOL(XOUT)              | Low-level output voltage                               | I <sub>Sink</sub> = 500 μA, V <sub>DD</sub> = 4.5 V                                                 |                           |                           | 1.5                       | V     |

| V <sub>OH</sub> (XOUT) | High-level output voltage                              | I <sub>Source</sub> = 500 μA, V <sub>DD</sub> = 5 V                                                 | 4.4                       |                           |                           | V     |

| V <sub>hyst</sub>      | Hysteresis voltage INT/HOLD, CS, XIN, SDI, SCLK, TEST  |                                                                                                     | 0.4                       |                           |                           | V     |

| Input Amplit           | fiers                                                  |                                                                                                     |                           |                           |                           |       |

| Various                | CU1ED and CU2ED high lovel output valtage              | V <sub>DD</sub> = 5 V, I <sub>Source</sub> = 100 μA                                                 | V <sub>DD</sub> – 0.05    | V <sub>DD</sub> –<br>0.02 |                           | V     |

| VOH(1)                 | CH1FB and CH2FB high-level output voltage              | V <sub>DD</sub> = 5 V, I <sub>Source</sub> = 2 mA                                                   | V <sub>DD</sub> –<br>0.5  |                           |                           | V     |

| Volve                  | CH1FB and CH2FB low-level output voltage               | I <sub>Sink</sub> = 100 μA                                                                          |                           | 15                        | 50                        | mV    |

| VOL(1)                 | Chirb and Chirb low-level output voltage               | I <sub>Sink</sub> = 2 mA                                                                            |                           |                           | 500                       | IIIV  |

| C <sub>ATTEN</sub>     | Cross-coupling attenuation CH1FB and CH2FB             | f <sub>in</sub> max <sub>(ch1)</sub> = 20 kHz, measured on channel 2                                | 40                        |                           |                           | dB    |

| Av                     | Open-loop gain                                         |                                                                                                     | 60                        | 100                       |                           | dB    |

| G <sub>BW</sub>        | Gain bandwidth product                                 | Input range 0.5 V to 4.5 V                                                                          | 1                         | 2.6                       |                           | MHz   |

| V <sub>IN</sub>        | Input voltage range                                    |                                                                                                     | 0.05                      |                           | V <sub>DD</sub> –<br>0.05 | V     |

| V(offset)              | Offset voltage at input                                |                                                                                                     | -10                       |                           | 10                        | mV    |

| CMRR                   | Common-mode rejection ratio                            | Inputs at V <sub>mid</sub> f <sub>in</sub> = 0 to 20 kHz                                            | 60                        | 80                        |                           | dB    |

| PM                     | Phase margin                                           | Gain = 1, $C_L$ = 200 pF, $R_L$ = 100 kΩ                                                            | 45                        |                           |                           | deg   |

| Prescaler, X           | Prescaler, XIN                                         |                                                                                                     |                           |                           |                           |       |

| Vosc                   | Minimum input peak amplitude                           | $V_{DD} = V_{min}$ , oscillator inverter biased feedback resistor 1 M $\Omega$ , $f_{OSC} = 24$ MHz | 150                       |                           |                           | mV    |

| C <sub>IN</sub>        | Input capacitance                                      | Assured by design                                                                                   |                           |                           | 7                         | pF    |

| I <sub>lkg</sub> (XIN) | Leakage current                                        |                                                                                                     | -1                        |                           | 1                         | μΑ    |

# **TPIC8101** KNOCK SENSOR INTERFACE SLIS110 - APRIL 2003

# dc electrical characteristics, $V_{DD}$ = 5 V $\pm 5\%$ , input frequency before prescaler = 4 MHz to 20 MHz ( $\pm 0.5\%$ ), $T_A$ = $-40^{\circ}$ C to 125°C (unless otherwise specified) (continued)

|                     | PARAMETER                                          | TEST CONDITIONS                                                                                 | MIN                   | TYP                       | MAX | UNITS |

|---------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----|-------|

| Multiplexe          | r                                                  |                                                                                                 | •                     |                           |     |       |

| C <sub>ATTEN</sub>  | Cross-coupling attenuation (assured by design)     | f <sub>in</sub> max <sub>(ch1)</sub> = 20 kHz, measured on channel 2                            | 40                    |                           |     | dB    |

| Anti-Aliasii        | ng Filter                                          |                                                                                                 | •                     |                           |     |       |

| f <sub>C</sub> ‡    | Cut-off frequency at -3 dB                         |                                                                                                 | 35                    | 45                        | 55  | kHz   |

| BW                  | Response 1 kHz to 20 kHz referenced to 1 kHz       | 70-mV RMS, input: CH1FB or CH2FB, output: OUT                                                   | -1                    | -0.5                      | 1   | dB    |

| ATTEN               | Attenuation at 100 kHz referenced to 1 kHz         | 70-mV RMS, input: CH1FB or CH2FB, output: OUT                                                   | -10                   | -15                       |     | dB    |

| Analog-to-          | Digital Converter                                  |                                                                                                 | •                     |                           |     |       |

| f <sub>S</sub>      | Sampling frequency                                 | For all frequencies stated                                                                      | 198                   | 200                       | 202 | kHz   |

| AR                  | Analog resolution                                  |                                                                                                 | 10                    |                           |     | Bit   |

| ADNL                | Differential linearity error (DNL)                 |                                                                                                 |                       | 1                         |     | Bit   |

| AINL                | Linearity error (INL)                              |                                                                                                 |                       | 1                         |     | Bit   |

| Digital-to-A        | Analog Converter                                   |                                                                                                 | _                     |                           |     |       |

| f <sub>S</sub> (DA) | Sampling frequency                                 |                                                                                                 | 198                   | 200                       | 202 | kHz   |

| DR                  | Resolution at 200 kHz                              |                                                                                                 | 10                    |                           |     | Bit   |

| DDNL                | Differential linearity error (DNL)                 | (Vreset < DACout < 0.98 V <sub>DD</sub> )                                                       | -1                    |                           | 1   | LSB   |

| DINL                | Linearity error (INL)                              | (Vreset < DACout < 0.98 V <sub>DD</sub> )                                                       | -2.5                  |                           | 2.5 | LSB   |

| DRNIL               | Repeatability (for characterization purposes only) |                                                                                                 | -1                    |                           | 1   | LSB   |

| Output Buf          | ffer                                               |                                                                                                 | -                     |                           |     |       |

| VOH                 | High-level output voltage                          | V <sub>DD</sub> = 5 V, I <sub>Source</sub> = 2 mA                                               | V <sub>DD</sub> - 0.2 | V <sub>DD</sub> –<br>0.15 |     | V     |

| V <sub>OL</sub>     | Low-level output voltage                           | V <sub>DD</sub> = 5 V, I <sub>Sink</sub> = 2 mA                                                 |                       | 120                       | 175 | mV    |

| Av                  | Open-loop gain                                     | $I_O = \pm 2 \text{ mA}$                                                                        | 60                    | 100                       |     | dB    |

| G                   | Output gain                                        | $I_O = \pm 2 \text{ mA}$                                                                        |                       | 1                         |     |       |

| V <sub>ripple</sub> | Ripple voltage                                     | C <sub>L</sub> = 0 to 22 nF, max slew rate,<br>12 mV/μs from Vreset to 4 V                      |                       |                           | 10  | mV    |

| t <sub>S</sub>      | Settling time                                      | C <sub>L</sub> = 0 to 22 nF, max slew rate,<br>12 mV/μs from Vreset to 4 V,<br>output: ±0.5 LSB |                       |                           | 20  | μs    |

<sup>‡</sup> f<sub>C</sub> is programmable (see Table 1).

# ac electrical characteristics, $V_{DD}$ = 5 V ±5%, $T_A$ = -40°C to 125°C (unless otherwise specified)

|      | DESCRIPTION                                                        | MIN | TYP | MAX | UNITS |

|------|--------------------------------------------------------------------|-----|-----|-----|-------|

| fSPI | SPI frequency                                                      |     |     | 5   | MHz   |

| t1   | Time from CS falling edge to SCLK rising edge                      | 10  |     |     | ns    |

| t2   | Time from CS falling edge to SCLK falling edge                     | 80  |     |     | ns    |

| t3   | Time for SCLK to go high                                           | 60  |     |     | ns    |

| t4   | Time for SCLK to go low                                            | 60  |     |     | ns    |

| t5   | Time from last SCLK falling edge to CS rising edge                 | 80  |     |     | ns    |

| t6   | Time from SDI valid to falling edge of SCLK                        | 60  |     |     | ns    |

| t7   | Time for SDI valid after falling edge of SCLK                      | 10  |     |     | ns    |

| t8   | Time after CS rises until INT/HOLD to go high                      | 8   |     |     | ns    |

| t9   | Time between two words for transmitting                            | 170 |     |     | ns    |

| t10  | Time for SDO valid after SDI on bus, at VDD = 5 V and load = 20 pF |     |     | 40  | ns    |

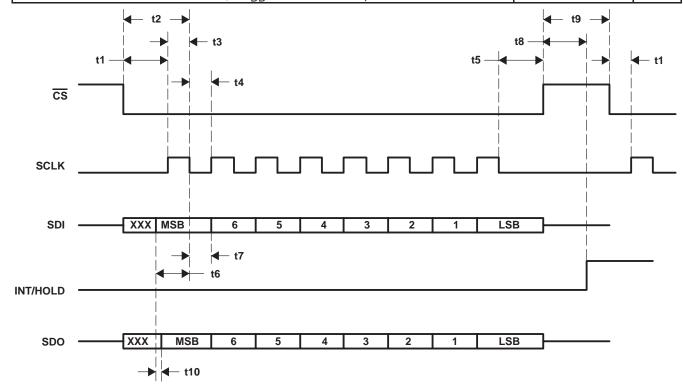

Figure 1. Serial Peripherial Interface (SPI)

This is an 8-bit SPI protocol used to communicate with the microcontroller in the system for setting various operating parameters.

When  $\overline{CS}$  is held high, the signals on the SCLK and SDI lines are ignored and SDO is forced into a high-impedance state. SCLK must be low when  $\overline{CS}$  is asserted low.

On each falling edge of the SCLK pulse after  $\overline{\text{CS}}$  is asserted low, the new byte is serially shifted into the register. The most significant bit (MSB) is shifted first. Only eight bits in a frame are acceptable. When a number of bits shifted is different than the value eight, the information is ignored and the register retains the old setting.

The shift register transfers the data into a latch register after the eighth SCLK clock pulse and when  $\overline{CS}$  transitions from low to high (see Figure 1).

The function of the integration mode is to ignore any SPI frame transmission when the INT/HOLD bit = 1. In the hold mode with INT/HOLD = 0, all necessary bytes may be transmitted.

# TPIC8101 KNOCK SENSOR INTERFACE

SLIS110 - APRIL 2003

#### function principle

The TPIC8101 is designed for knock sensor signal conditioning in automotive applications. The device is an analog interface between the engine acoustical sensors or accelerometers and the fuel management systems of a gasoline engine. The two wide-band amplifiers process signals from the piezoelectric sensors. Outputs of the amplifiers feed a channel select mux switch and then a 3<sup>rd</sup> order antialiasing filter. This signal is converted using an analog-to-digital conversion (10 bits with a sampling frequency of 200 kHz) prior to the gain stage.

The gain stage is adjustable via the SPI to compensate for the knock energies. The gain setting is selectable up to 64 values ranging from 0.111 to 2.0.

The output of the gain stage feeds a band-pass filter circuit to process the particular frequency component associated with the engine and transducer.

The band-pass filter has a gain of two and a center frequency range between 1.22 kHz and 19.98 kHz (64-bit selection). The output from this stage is internally clamped.

The output from the band-pass filter is full-wave rectified with its output clamped below VDD.

The full-wave rectified signals are integrated using an integrator time constant set by the SPI and integration time window set by the pulse width of INT/HOLD. At the start of each knock window, the integrator output is reset. The output of the integrator is internally clamped and the digital output may be directly interfaced to the microprocessor.

The integrated signal is converted to an analog format by a 10-bit DAC. The microprocessor may interface to this signal, reads this data, and adjusts the spark ignition timing to optimize fuel efficiency related to load versus engine RPM.

#### description of the functional terminals

#### supply voltage (V<sub>DD</sub>)

The  $V_{DD}$  terminal is the input supply for the IC, typically 5 V  $\pm$ 5% tolerant. A noise filter capacitor of 4.7  $\mu$ F (typ) is required on this terminal to ensure stability of the internal circuits.

#### ground (GND)

The GND terminal is connected to the system ground rail.

#### reference supply (V<sub>ref</sub>)

The  $V_{ref}$  is an internally generated supply reference voltage for biasing the amplifier inputs. The terminal is used to decouple any noise in the system by placing an external capacitor of 22 nF (typ).

#### buffered integrator output (OUT)

The OUT terminal is the output of the integrated signal. This is an analog signal interfaced to the microprocessor A/D channel for data acquisition. A capacitor of 2.2 nF is used to stabilize the signal output.

#### integration/hold mode selection (INT/HOLD)

The INT/HOLD is an input control signal from the microprocessor to select either to integrate the sensed signal or to hold the data for acquisition. There is an internal pulldown on this terminal (default HOLD mode).

#### chip select for SPI (CS)

The  $\overline{\text{CS}}$  terminal allows serial communication to the IC through the SPI from a master controller. The chip select is active low with an internal pullup (default inactive).

#### description of the functional terminals (continued)

#### oscillator input (XIN)

The XIN terminal is the input to the inverter used for the oscillator circuit. An external clock signal from the MCU, crystal, or ceramic resonator is configured with resistors and capacitors. To bias the inverter, a resistor (1  $M\Omega$  typ) is placed across XIN and XOUT.

This clock signal is prescaled to set the internal sampling frequency of the A/D converter.

#### oscillator output (XOUT)

The XOUT terminal is the output of the inverter used for the oscillator circuit.

#### data output (SDO)

The SDO output is the SPI data bus reporting information back to the microprocessor. This is a 3-state output with the output set to high-impedance mode when  $\overline{CS}$  is pulled to  $V_{DD}$ . The high-impedance state can also be programmed by setting a bit in the prescale word which takes precedence over the  $\overline{CS}$  setting. The output is disabled when the  $\overline{CS}$  terminal is pulled high  $(V_{DD})$ .

#### data input (SDI)

The SDI terminal is the communication interface for data transfer between the master and slave components. The SDI has an internal pullup to V<sub>DD</sub>; the data stream is in 8-bit word format.

#### serial clock (SCLK)

The SCLK output signal is used for synchronous communication of data. Typically, the output from the master clock is low with the IC having an internal pullup resistor to  $V_{DD}$ . The data is clocked to the internal shift register on the falling clock edge.

#### test (TEST)

The  $\overline{\text{TEST}}$  terminal, when pulled low, allows the IC to enter the test mode. During normal operation, this terminal is left open or tied high (V<sub>DD</sub>). There is an internal pullup to V<sub>DD</sub> (default).

#### feedback output for amplifiers (CH1FB and CH2FB)

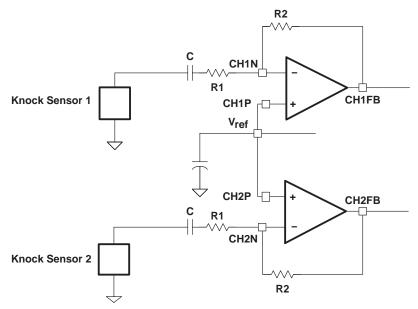

The CHXFB are amplifier outputs for the sensor signals. The gain of the respective amplifiers is set using the CHXFB and CHX input terminals (see Figure 1).

#### input amplifiers (CH1P, CH1N, CH2P, and CH2N)

CH1P, CH1N, CH2P, and CH2N are the inputs for the two amplifiers which interface to the external knock sensors.

The gain is set by external resistors R1 and R2. The inputs and outputs of the amplifier are rail-to-rail compatible to the supply V<sub>DD</sub>.

An internal multiplexer selects the desired sensor signal to process programmable through the SPI.

NOTE: The series capacitor C is not mandatory and may be removed in some application circuits.

Figure 2. Input Signal Configuration

**Table 1. Integrator Programming**

| DECIMAL<br>VALUE (D4D0) | INTEGRATOR TIME<br>CONSTANT<br>(μSEC) | BAND-PASS<br>FREQUENCY<br>(kHz) | GAIN  | DECIMAL VALUE<br>(D5D0) | BAND-PASS<br>FREQUENCY<br>(kHz) | GAIN  |

|-------------------------|---------------------------------------|---------------------------------|-------|-------------------------|---------------------------------|-------|

| 0                       | 40                                    | 1.22                            | 2     | 32                      | 4.95                            | 0.421 |

| 1                       | 45                                    | 1.26                            | 1.882 | 33                      | 5.12                            | 0.4   |

| 2                       | 50                                    | 1.31                            | 1.778 | 34                      | 5.29                            | 0.381 |

| 3                       | 55                                    | 1.35                            | 1.684 | 35                      | 5.48                            | 0.364 |

| 4                       | 60                                    | 1.4                             | 1.6   | 36                      | 5.68                            | 0.348 |

| 5                       | 65                                    | 1.45                            | 1.523 | 37                      | 5.9                             | 0.333 |

| 6                       | 70                                    | 1.51                            | 1.455 | 38                      | 6.12                            | 0.32  |

| 7                       | 75                                    | 1.57                            | 1.391 | 39                      | 6.37                            | 0.308 |

| 8                       | 80                                    | 1.63                            | 1.333 | 40                      | 6.64                            | 0.296 |

| 9                       | 90                                    | 1.71                            | 1.28  | 41                      | 6.94                            | 0.286 |

| 10                      | 100                                   | 1.78                            | 1.231 | 42                      | 7.27                            | 0.276 |

| 11                      | 110                                   | 1.87                            | 1.185 | 43                      | 7.63                            | 0.267 |

| 12                      | 120                                   | 1.96                            | 1.143 | 44                      | 8.02                            | 0.258 |

| 13                      | 130                                   | 2.07                            | 1.063 | 45                      | 8.46                            | 0.25  |

| 14                      | 140                                   | 2.18                            | 1     | 46                      | 8.95                            | 0.236 |

| 15                      | 150                                   | 2.31                            | 0.944 | 47                      | 9.5                             | 0.222 |

| 16                      | 160                                   | 2.46                            | 0.895 | 48                      | 10.12                           | 0.211 |

| 17                      | 180                                   | 2.54                            | 0.85  | 49                      | 10.46                           | 0.2   |

| 18                      | 200                                   | 2.62                            | 0.81  | 50                      | 10.83                           | 0.19  |

| 19                      | 220                                   | 2.71                            | 0.773 | 51                      | 11.22                           | 0.182 |

| 20                      | 240                                   | 2.81                            | 0.739 | 52                      | 11.65                           | 0.174 |

| 21                      | 260                                   | 2.92                            | 0.708 | 53                      | 12.1                            | 0.167 |

| 22                      | 280                                   | 3.03                            | 0.68  | 54                      | 12.6                            | 0.16  |

| 23                      | 300                                   | 3.15                            | 0.654 | 55                      | 13.14                           | 0.154 |

# TPIC8101 KNOCK SENSOR INTERFACE SLIS110 - APRIL 2003

# **Table 1. Integrator Programming (Continued)**

| DECIMAL<br>VALUE (D4D0) | INTEGRATOR TIME<br>CONSTANT<br>(μSEC) | BAND-PASS<br>FREQUENCY<br>(kHz) | GAIN  | DECIMAL VALUE<br>(D5D0) | BAND-PASS<br>FREQUENCY<br>(kHz) | GAIN  |

|-------------------------|---------------------------------------|---------------------------------|-------|-------------------------|---------------------------------|-------|

| 24                      | 320                                   | 3.28                            | 0.63  | 56                      | 13.72                           | 0.148 |

| 25                      | 360                                   | 3.43                            | 0.607 | 57                      | 14.36                           | 0.143 |

| 26                      | 400                                   | 3.59                            | 0.586 | 58                      | 15.07                           | 0.138 |

| 27                      | 440                                   | 3.76                            | 0.567 | 59                      | 15.84                           | 0.133 |

| 28                      | 480                                   | 3.95                            | 0.548 | 60                      | 16.71                           | 0.129 |

| 29                      | 520                                   | 4.16                            | 0.5   | 61                      | 17.67                           | 0.125 |

| 30                      | 560                                   | 4.39                            | 0.471 | 62                      | 18.76                           | 0.118 |

| 31                      | 600                                   | 4.66                            | 0.444 | 63                      | 19.98                           | 0.111 |

#### PRINCIPLES OF OPERATION

#### system transfer equation

The output voltage may be derived from:

$$V_{O} = V_{IN} \times A_{IN} \times A_{P} \times A_{BP} \times A_{INT} \times \frac{t_{INT}}{\tau_{C}} \times A_{O} + V_{RESET}$$

where:

V<sub>IN</sub> = Input voltage peak (amplitude)

V<sub>O</sub> = Output voltage

A<sub>IN</sub> = Input amplifier gain setting

A<sub>P</sub> = Programmable gain setting

A<sub>BP</sub> = Gain of band-pass filter

A<sub>INT</sub> = Gain of integrator

$t_{INT}$  = Integration time from 0.5 ms to 10 ms

A<sub>O</sub> = Output buffer gain

$\tau_C$  = Programmable integrator time constant

V<sub>RESET</sub> = Reset voltage from which the integration operation starts

If  $A_{BP} = A_{INT} = 2$  and  $A_{IN} = A_O = 1$ ,

then

$$V_{O} = V_{IN} \times A_{P} \times \frac{8}{\Pi} \times \frac{t_{INT}}{\tau_{C}} + V_{RESET}$$

# programming in normal mode ( $\overline{TEST} = 1$ )

To enable programming in the normal mode, the  $\overline{\text{TEST}}$  terminal must be high. Communication is through the SPI and the  $\overline{\text{CS}}$  terminal is used to enable the IC. The information on the SDI line consists of two parts: address and data

After power up, the SPI is in default mode (see Table 2).

#### default SPI mode

The SPI is in the default mode on the power up sequence. In this case, the SDO directly equals the SDI (echo function). In this mode, five commands can be transmitted by the master controller to configure the IC (see Table 2).

#### SLIS110 - APRIL 2003

#### PRINCIPLES OF OPERATION

Table 2. Default SPI Mode

| NO. | CODE          | COMMAND (t)                                | DATA                                                                                                                                                                                                                                                                                       | RESPONSE (t)           |

|-----|---------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1   | 010 D[4:0]    | Set the prescaler and SDO status           | OSC <sub>IN</sub> frequency D[4:1]=0000=> 4 MHz D[4:1]=0001=> 5 MHz D[4:1]=0010=> 6 MHz D[4:1]=0011=> 8 MHz D[4:1]=0100=> 10 MHz D[4:1]=0101=> 12 MHz D[4:1]=0110=> 16 MHz D[4:1]=0111=> 20 MHz D[4:1]=0111=> 20 MHz D[4:1]=1000=> 24 MHz D[0]=0 => SDO active D[1]=1=> SDO high impedance | SDI<br>(010 D[4:0])    |

| 2   | 1110 000 D[0] | Select the channel                         | D[0]=0 => Channel 1 selected D[1]=1=> Channel 2 selected                                                                                                                                                                                                                                   | SDI<br>(1110 000 D[0]) |

| 3   | 00 D[5:0]     | Set the band-pass center frequency         | D[5:0] (see Table 1)                                                                                                                                                                                                                                                                       | SDI<br>(00 D[5:0])     |

| 4   | 10 D[5:0]     | Set the gain                               | D[5:0] (see Table 1)                                                                                                                                                                                                                                                                       | SDI<br>(10 D[5:0])     |

| 5   | 110 D[4:0]    | Set the integration time constant          | D[4:0] (see Table 1)                                                                                                                                                                                                                                                                       | SDI<br>(100 D[4:0])    |

| 6   | 0111 0001     | Set SPI configuration to the advanced mode | None                                                                                                                                                                                                                                                                                       | SDI<br>(0111 0001)     |

NOTE: Command #6 is to enter into the advanced mode.

#### advanced SPI mode

The advanced SPI mode has additional features to the default SPI mode. A control byte is written to the SDI and shifted with the MSB first. The response byte on the SDO is shifted out with the MSB first. The response byte corresponds to the previous command. Therefore, the SDI shifts in a control byte n and shifts out a response command byte n-1. Each control/response pair of commands requires two full 8-bit shift cycles to complete a transmission. The control bytes with the expected response are shown in Table 3.

In the advanced SPI mode, only a power-down condition may reset the SPI mode to the default state on the subsequent power-up cycle.

#### PRINCIPLES OF OPERATION

**Table 3. Advanced SPI Mode**

| NO. | CODE          | COMMAND (t)                                | DATA                                                                                                                                                                                                                                                                                       | RESPONSE (t)                                                |

|-----|---------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1   | 010 D[4:0]    | Set the prescaler and SDO status           | OSC <sub>IN</sub> frequency D[4:1]=0000=> 4 MHz D[4:1]=0001=> 5 MHz D[4:1]=0010=> 6 MHz D[4:1]=0011=> 8 MHz D[4:1]=0100=> 10 MHz D[4:1]=0101=> 12 MHz D[4:1]=0110=> 16 MHz D[4:1]=0111=> 20 MHz D[4:1]=11100=> 24 MHz D[4:1]=1000=> 24 MHz D[0]=0=> SDO active D[1]=1=> SDO high impedance | Byte 1 (D7 to D0) of the digital integrator output          |

| 2   | 1110 000 D[0] | Select the channel                         | D[0]=0 => Channel 1 selected D[1]=1=> Channel 2 selected                                                                                                                                                                                                                                   | D9 to D8 of digital integrator output followed by six zeros |

| 3   | 00 D[5:0]     | Set the band-pass center frequency         | D[5:0] (see Table 1)                                                                                                                                                                                                                                                                       | Byte 1 (MSB) of the 00000001                                |

| 4   | 10 D[5:0]     | Set the gain                               | D[5:0] (see Table 1)                                                                                                                                                                                                                                                                       | Byte 2 (LSB) 11100000                                       |

| 5   | 110 D[4:0]    | Set the integration time constant          | D[4:0] (see Table 1)                                                                                                                                                                                                                                                                       | SPI configuration<br>(MSB)01110001(LSB)                     |

| 6   | 0111 0001     | Set SPI configuration to the advanced mode | None                                                                                                                                                                                                                                                                                       | Inverted SPI configuration (MSB)10001110(LSB)               |

# digital data output from the TPIC8101

## digital output

- Digital integrator output (10 bits, D[9:0])

- First response byte (MSB): 8 bits for D7 to D0 of the integrator output

- Second response byte (LSB): 2 bits for D9 to D8 of the integrator output followed by six zeros

#### programming examples

#### prescaler/SDO status

• 01000101 programs an input frequency of 6 MHz with SDO terminal in high impedance.

#### channel selection

• 1110001 selects channel 2.

#### band-pass frequency

• 00100111 programs a band-pass filter with center frequency of 6.37 kHz.

#### gain control

• 10010100 programs the gain with attenuation of 0.739.

#### integrator time constant

• 11000011 programs integrator time constant of 55 μs. The binary values are in Table 1 through Table 3.

## programming in TEST mode ( $\overline{TEST} = 0$ )

To enter test mode, the TEST terminal must be low. See Table 4 for the signal that may be accessed in this mode.

**Table 4. Programming in TEST Mode**

| NO. | TEST DESCRIPTION                                    | SDI COMMAND<br>MSBLSB | RESPONSE          | NOTE                                                                                                                                                                                            |

|-----|-----------------------------------------------------|-----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T1  | AAF individual test                                 | 1111 0000             | ADC clock         | Deactivates the input and output op amps AAF input connected to CH1FB terminal AAF output connected to OUT terminal                                                                             |

| T2  | In-line test to AAF output                          | 1111 0000             | None              | Deactivates the output op amp AAF output connected to OUT terminal                                                                                                                              |

| Т3  | Output buffer individual test                       | 1111 0010             | None              | Opens the feedback loop of the output buffer and deactivates the input op amp and AAF CH1FB connected to positive input terminal of op amp CH2FB connected to negative input terminal of op amp |

| T4  | ADC/DAC individual test (with the output buffer)    | 1111 0011             | ADC data          | Deactivates the input op amps and AAF INT/HOLD = ADC_Sync OSCIN = ADC_SCLK DAC shifted in from SDI terminal                                                                                     |

| T5  | ADC/DAC individual test (without the output buffer) | 1111 0100             | ADC data          | Deactivates the input op amps, AAF, and output buffer INT/HOLD = ADC_Sync OSCIN = ADC_SCLK DAC is shifted in from SDI terminal                                                                  |

| Т6  | In-line test to ADC output                          | 1111 0011             | ADC data          | INT/HOLD = ADC_Sync OSCIN = ADC_SCLK DAC shifted in from SDI terminal                                                                                                                           |

| T7  | Reading of digital clamp flag                       | 1111 1000             | Clamp flag D[2:0] | Implies command 6 (advanced SPI mode) D[0]: Gain stage clamp status D[1]: BPF stage clamp status D[2]: INT stage clamp status D=0 => No clamp activated D=1 => Clamp activated                  |

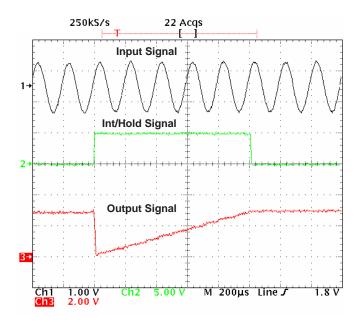

# TYPICAL CHARACTERISTICS

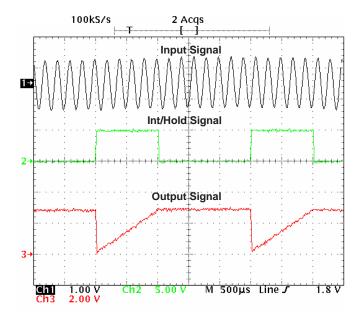

Figure 3. Amplified Input Signal Process

Figure 4. Input Signal Processing

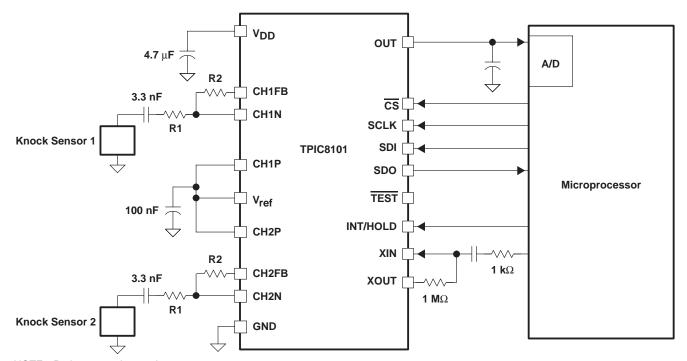

# application schematic

NOTE: R1 is greater than 25 k $\Omega$ .

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated