August 1986 Revised April 2000

# DM74S174 • DM74S175 Hex/Quad D Flip-Flop with Clear

#### **General Description**

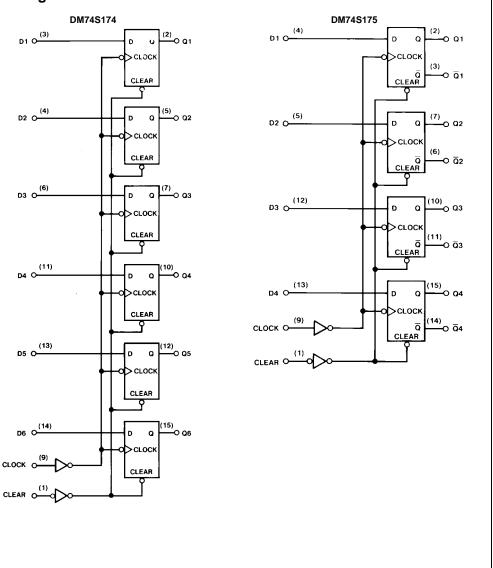

These positive-edge-triggered flip-flops utilize TTL circuitry to implement D-type flip-flop logic. All have a direct clear input, and the quad (DM74S175) versions feature complementary outputs from each flip-flop.

Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the HIGH or LOW level, the D input signal has no effect at the output.

#### **Features**

- DM74S174 contain six flip-flops with single-rail outputs.

- DM74S175 contain four flip-flops with double-rail outputs.

- Buffered clock and direct clear inputs

- Individual data input to each flip-flop

- Applications include:

Buffer/storage registers Shift registers

- Pattern generators

- Typical clock frequency 110 MHz

- Typical power dissipation per flip-flop 75mW

#### **Ordering Code:**

| Order Number Package Number Package Description |           |      |                                                                       |  |  |  |

|-------------------------------------------------|-----------|------|-----------------------------------------------------------------------|--|--|--|

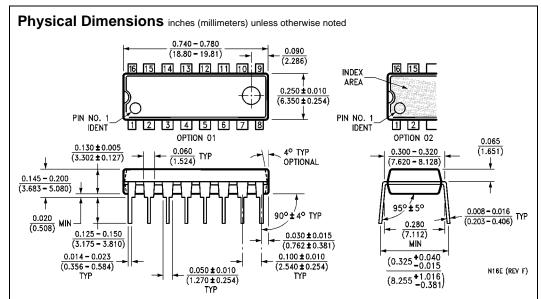

|                                                 | DM74S174N | N16E | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |  |  |  |

|                                                 | DM74S175N | N16E | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |  |  |  |

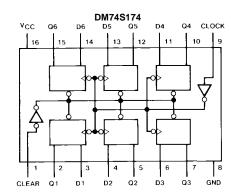

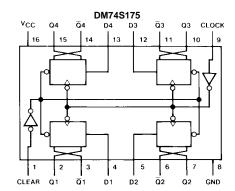

### **Connection Diagrams**

### Function Table (Each Flip-Flop)

|       | Inputs | Outputs |       |                  |  |

|-------|--------|---------|-------|------------------|--|

| Clear | Clock  | D       | Q     | Q (Note 1)       |  |

| L     | Х      | Х       | L     | Н                |  |

| Н     | 1      | Н       | Н     | L                |  |

| Н     | 1      | L       | L     | Н                |  |

| Н     | L      | X       | $Q_0$ | $\overline{Q}_0$ |  |

- H = HIGH Level (steady state)

- H = HIGH Level (steady state)

L = LOW Level (steady state)

X = Don't Care

↑ = Transition from LOW-to-HIGH level

Q<sub>0</sub> = The level of Q before the indicated steady-state input conditions were established.

Note 1: DM74S175 only.

#### **Logic Diagrams**

### **Absolute Maximum Ratings**(Note 2)

Storage Temperature Range

Supply Voltage 7V Input Voltage 5.5V Operating Free Air Temperature Range 0°C to +70°C

Note 2: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol           | Parameter                                               |         | Min  | Nom | Max  | Units |

|------------------|---------------------------------------------------------|---------|------|-----|------|-------|

| V <sub>CC</sub>  | Supply Voltage                                          |         | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub>  | HIGH Level Input Voltage                                |         | 2    |     |      | V     |

| V <sub>IL</sub>  | LOW Level Input Vo                                      | oltage  |      |     | 0.8  | V     |

| I <sub>OH</sub>  | HIGH Level Output                                       | Current |      |     | -1   | mA    |

| I <sub>OL</sub>  | LOW Level Output                                        | Current |      |     | 20   | mA    |

| f <sub>CLK</sub> | Clock Frequency (Note 3)                                |         | 0    | 110 | 75   | MHz   |

| f <sub>CLK</sub> | Clock Frequency (Note 4)                                |         | 0    | 90  | 65   | MHz   |

| t <sub>W</sub>   | Pulse Width                                             | Clock   | 7    |     |      |       |

|                  | (Note 3)                                                | Clear   | 10   |     |      | ns    |

|                  | Pulse Width                                             | Clock   | 9    |     |      | 115   |

|                  | (Note 4)                                                | Clear   | 12   |     |      |       |

| t <sub>SU</sub>  | Data Setup Time (Note 3)                                |         | 5    |     |      | no    |

|                  | Data Setup Time (Note 4)                                |         | 7    |     |      | ns    |

| t <sub>H</sub>   | Data Hold Time (Note 3) Data Hold Time (Note 4)         |         | 3    |     |      |       |

|                  |                                                         |         | 5    |     |      | ns    |

| t <sub>REL</sub> | Clear Release Time (Note 3) Clear Release Time (Note 4) |         | 5    |     |      |       |

|                  |                                                         |         | 7    |     |      | ns    |

| T <sub>A</sub>   | Free Air Operating Temperature                          |         | 0    |     | 70   | °C    |

$-65^{\circ}C$  to  $+150^{\circ}C$

Note 3:  $C_L = 15$  pF,  $R_L = 280\Omega$ ,  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ . Note 4:  $C_L = 50$  pF,  $R_L = 280\Omega$ ,  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

#### **Electrical Characteristics**

over recommended operating free air temperature (unless otherwise noted)

| Symbol          | Parameter                         | Conditions                                                   | Min | Typ<br>(Note 5) | Max  | Units |

|-----------------|-----------------------------------|--------------------------------------------------------------|-----|-----------------|------|-------|

| VI              | Input Clamp Voltage               | $V_{CC} = Min, I_I = -18 \text{ mA}$                         |     |                 | -1.2 | V     |

| V <sub>OH</sub> | HIGH Level Output Voltage         | $V_{CC} = Min, I_{OH} = Max$<br>$V_{II} = Max, V_{IH} = Min$ | 2.7 | 3.4             |      | ٧     |

| V <sub>OL</sub> | LOW Level Output Voltage          | $V_{CC} = Min, I_{OL} = Max$ $V_{IH} = Min, V_{IL} = Max$    |     |                 | 0.5  | V     |

| I               | Input Current @ Max Input Voltage | $V_{CC} = Max, V_I = 5.5V$                                   |     |                 | 1    | mA    |

| I <sub>IH</sub> | HIGH Level Input Current          | $V_{CC} = Max, V_I = 2.7V$                                   |     |                 | 50   | μΑ    |

| I <sub>IL</sub> | LOW Level Input Current           | $V_{CC} = Max, V_I = 0.5V$                                   |     |                 | -2   | mA    |

| Ios             | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 6)                               | -40 |                 | -100 | mA    |

| I <sub>CC</sub> | Supply Current (DM74S174)         | V <sub>CC</sub> = Max (Note 7)                               |     | 90              | 144  | mA    |

| Icc             | Supply Current (DM74S175)         | V <sub>CC</sub> = Max (Note 7)                               |     | 60              | 96   | mA    |

|                 |                                   |                                                              |     |                 |      |       |

Note 5: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 6: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 7: With all outputs OPEN and 4.5V applied to all DATA and CLEAR inputs, I<sub>CC</sub> is measured after a momentary ground, then 4.5V applied to the CLOCK input.

# **Switching Characteristics**

at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

|                  | I Parameter                              |                 | $R_L = 280\Omega$      |     |                        |     |       |    |

|------------------|------------------------------------------|-----------------|------------------------|-----|------------------------|-----|-------|----|

| Symbol           |                                          | From (Input)    | C <sub>L</sub> = 15 pF |     | C <sub>L</sub> = 50 pF |     | Units |    |

|                  |                                          | To (Output)     | Min                    | Max | Min                    | Max |       |    |

| f <sub>MAX</sub> | Maximum Clock Frequency                  |                 | 75                     |     | 65                     |     | MHz   |    |

| t <sub>PLH</sub> | Propagation Delay Time                   | Clock to Output | Clock to Output        | 12  |                        | 15  | ns    |    |

|                  | LOW-to-HIGH Level Output                 | Clock to Catput |                        |     |                        |     |       |    |

| t <sub>PHL</sub> | Propagation Delay Time                   | Clock to Output |                        | 17  |                        | 21  | ns    |    |

|                  | HIGH-to-LOW Level Output                 | Clock to Catput | Took to Output         |     |                        |     |       |    |

| t <sub>PLH</sub> | Propagation Delay Time                   | Clear to Q      | 15                     |     | 18                     | ns  |       |    |

|                  | LOW-to-HIGH Level Output (DM74S175 Only) |                 |                        | 15  |                        | 10  | 115   |    |

| t <sub>PHL</sub> | Propagation Delay Time                   | Clear to O      | Clear to Q             |     | 22                     |     | 23    | ns |

|                  | HIGH-to-LOW Level Output                 | Ciour to Q      |                        |     |                        | 2.5 | 113   |    |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com