引言

目前,在嵌入式处理器芯片中,以ARM7为核心的处理器是应用较多的一种。它具有多种工作模式,并且支持两种不同的指令集(标准32位ARM指令集和16位Thumb指令集)。μC/OSII是专为嵌入式应用设计的抢占式、多任务实时操作系统,可用于各类8位、16位和32位单片机或DSP。μC/OSII向ARM7移植具有得天独厚的优点,所以“μC/OSII+ARM7”成为广泛应用的一款平台。

不管是哪种型号的ARM处理器,也无论该嵌入式系统中是否有操作系统,在计算机与外界实时交互的过程中,中断技术都是一项关键的技术。当外部事件发生时,CPU必须及时响应中断以实现对相应事件的处理,因此能否中断嵌套是影响嵌入式系统实时性能的主要因素。

1 ARM7的中断处理

ARM7处理器的中断主要有两种,本文主要讨论IRQ中断异常的响应机制。当中断请求IRQ到来使CPU进入中断响应时,CPU将会自动完成下列工作:首先,将PC、CPSR的当前值存入中断模式的LR、SPSR中;然后,操作CPSR中的运行状态位,使CPU进入中断模式并关闭中断;最后将PC的值改成0x00000018,从而使CPU的执行跳转到IRQ中断入口0x00000018处。异常向量表中的0x00000018处使用一条“LDR PC,[PC,#0xff0]”指令,在IRQ处使用的这条指令与其他向量不同。当CPU执行这条指令但还没有跳转时,PC的值为0x00000020(因为ARM7TDMI内核是三级流水结构),0x00000020减去0x00000FF0为0xFFFFF030,这是VIC的特殊寄存器VICVectAddr的地址单元。这个寄存器保存当前将要服务的IRQ的中断服务程序的入口,故读取VICVectAddr寄存器的值,然后放入PC程序指针,即跳转到相应中断服务程序,从而使CPU开始执行中断服务程序。

2 Handler宏分析

“μC/OSII+ARM7”系统中,只使用了ARM7的IRQ中断。由于不同的ARM芯片的中断系统并不完全一样,因此不可能编写出对所有使用ARM核的处理器通用的中断及时钟节拍移植代码。但是,为了使用户用C语言编写中断服务程序时不必为处理器的硬件区别而困扰,这里根据μC/OSII对中断服务程序的要求以及ARM7体系结构和ADS编译器的特点,编写了一个适用于所有基于ARM7核处理器的汇编宏--Handler。这个宏实现了“μC/OSII+ ARM7”中断服务程序的汇编语言代码与C语言函数代码之间的通用接口。其作用是对用户的C语言中断处理程序进行包装,只有通过这个包装之后,系统才能执行用户的中断处理程序。

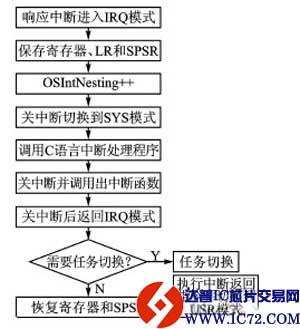

中断服务程序流程如图1所示。在进入Handler宏中,首先保存LR、SPSR以及相关寄存器的值于中断模式下的堆栈中,以便于断点恢复。然后使记录系统中断次数的全局变量OSIntNeSTing加1并关中断切换到系统模式,调用C语言中断处理程序。在执行完中断处理程序后,调用出中断函数,以获取最高优先级就绪任务的任务控制块指针和任务优先级。返回中断模式后,通过比较当前任务与待切换任务的优先级,判断是否进行任务切换,最后返回断点。

IRQ异常处理代码的汇编部分--Handler宏:

MACRO

$IRQ_Label HANDLER $IRQ_ExcepTION_Function

EXPORT $IRQ_Label;输出的标号

IMPORT $IRQ_Exception_Function;引用的外部标号

$IRQ_Label

SUB LR, LR, #4;计算返回地址

STMFD SP!, {R0R3, R12, LR};保存任务环境

MRS R3, SPSR;保存状态

STMFD SP, {R3,SP,LR}^;保存用户状态的R3、SP、LR

;OSIntNesting++

LDR R2,=OSIntNesting

LDRB R1, [R2]

ADD R1, R1, #1

STRB R1, [R2]

SUB SP, SP, #4*3

MSR CPSR_c, #(NoInt | SYS32Mode)

;切换到系统模式以便对相关寄存器进行操作

CMP R1, #1

LDREQ SP, =StackUsr

;在第1次中断时就重新开辟一个专门存储中断中用到

;的变量以避免存储空间的冲突

BL $IRQ_Exception_Function ;调用C语言的中断处理程序

MSR CPSR_c, #(NoInt | SYS32Mode);切换到系统模式

LDR R2, =OsEnterSum

;OsEnterSum,使OSIntExit退出时中断关闭

MOV R1, #1

STR R1, [R2]

BL OSIntExit

;获取最高优先级就绪任务的任务控制块指针和优先级

LDR R2, =OsEnterSum

;中断服务程序要退出,所以OsEnterSum=0

MOV R1, #0

STR R1, [R2]

MSR CPSR_c, #(NoInt | IRQ32Mode) ;切换回中断模式

LDMFD SP, {R3, SP, LR}^ ;恢复用户状态的R3、SP、LR

LDR R0, =OSTCBHighRdy

LDR R0, [R0]

LDR R1, =OSTCBCur

LDR R1, [R1]

CMP R0, R1

ADD SP, SP, #4*3

MSR SPSR_cxsf, R3

LDMEQFD SP!, {R0R3, R12, PC}^ ;不进行任务切换

LDR PC, =OSIntCtxSw;进行任务切换

MEND

END

通过对Handler宏的分析可知,用户的C语言中断处理程序是在特权模式--系统模式下运行的,并且CPU在执行中断服务程序时中断都是关闭的,所以本系统采用的是最为简单的非嵌套中断方式。这种方式的优点是,上下文数据不会被任何顺序的中断所破坏;缺点是,在中断服务程序执行时不能根据中断优先级进行中断嵌套,延时时间长,只有当一个ISR完全结束并退出中断后才重新接受中断,降低了系统的实时特性。为提高系统的实时性,需要对其中断进行优化。

3 中断的优化

改写μC/OSII 内核中 HANDLER 宏可以实现ARM的中断嵌套,这样做虽然提高了系统的实时性,但损害了系统运行的稳定性和可移植性。通过对中断过程的分析,下面给出一种编写中断服务程序的模板,充分利用ISR执行在特权模式--系统模式这一特点来实现中断嵌套的条件。中断服务程序模板如下:

void ISR(void){

OS_ENTER_CRITICAL();//在中断服务程序中关中断清中断标志;//防止没有清中断标志使得中断多次进入关闭低优先级;//禁止低优先级中断

S_EXIT_CRITICAL();//在中断服务程序中开中断用户的C语言代码;//进行用户在中断中要做的工作

VICVectAddr=0;//将中断服务程序的入口地址置0

}

由于Handler宏中已将LR、SPSR、返回地址和发生中断前的堆栈指针等寄存器入栈保存,所以接下来要做的就只剩下开关中断的工作。由于在进入C中断处理程序之前进入的是关中断系统模式,所以必须在C语言中重新打开中断,而C语言是不能进行寄存器操作的,因此必须调用软中断OS_EXIT_CRITICAL()重新打开中断。在开中断之前,要判断将全局变量OsEnterSum减1后是否为0,所以必须在调用开中断之前调用软中断OS_ENTER_CRITICAL()将OsEnterSum变成1。在临界区中可以进行一些处理,如清中断标志、关低优先级中断等。进行C语言中断服务程序之后要将VICVectAddr置位为0,这是ARM7处理器核的要求必须进行这样的编写,否则会导致一些错误(如不能第2次进入中断等)。

结语

“μC/OSII+ ARM7”是当前嵌入式系统中广泛应用的一款平台,适合于复杂度不是很高的中小型嵌入式系统。本文在深入分析”μC/OSII+ ARM7”中断机制的基础上,对IRQ中断响应机制进行了改进,提出了优化方案。实验证明,此方法可以实现中断的嵌套并且提高系统实时性,具有一定的应用价值。