1 NAND FLASH控制器架构

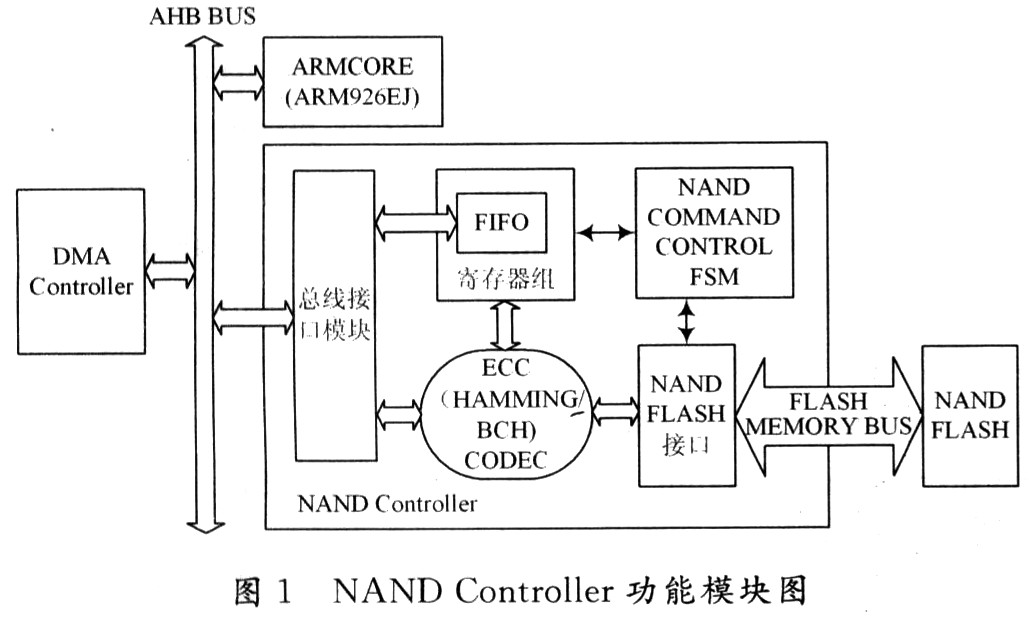

图1是NAND控制器和DMA模块的组成框图,ARM9内核和DMAC都是AHB总线上的master模块,都包含符合AMBA标准的总线接口模块与之交互工作,NAND控制器包含总线接口模块,控制状态机转换的状态控制模块,用以缓冲数据、收发命令和状态字的寄存器组,提供ECC校验纠错码的ECC算法编/解码器模块和直接控制NAND FLASH的接口模块。

总线接口模块负责接受CPU核发送的指令,将收发数据送至相应数据寄存器和指令寄存器,并将状态寄存器内容返回给CORE。寄存器组负责整个FLASH控制器的控制工作,包含指令、配置、状态、数据、错误地址寄存器等等,是控制器的核心,通过配置不同的参数,可以实现对多种SLC/MLC NAND FLASH的支持。ECC算法编程F解码器模块提供校验功能,提供纠错信息。状态控制模块提供包括命令字发送状态组,地址发送状态组,读状态组,写状态组共26种NANDFLASH状态的翻转,用以发出对NAND FLASH读写控制信号。与NAND FLASH直接连接的接口模块提供NAND FLASH工作电压、使能和动作时所需的相应电平状态,该模块受到状态机控制模块的控制。该控制器对电平的控制简化了软件工作,驱动软件不必再按照读写时序来配置繁琐的控制电平。本设计针对MLCNAND FLASH的特点,在控制器中增加了对Randomdata output/input命令的支持,以满足ECC纠错的要求,并使读写不再限于整页的方式,提高了数据处理的灵活性。

2 BCH编解码器

BCH编解码器是保证MLC NAND FLASH数据可靠性的关键,也是本设计的核心部分。本设计采用二进制BCH(4148,4096,9)码,是GF(213)上BCH(819l,8139)码的缩短码,通过52个校验比特可以纠4 b的差错(t=4)。生成多项式G(x)=gRxR+gR-1xR-1+…+g1x+g0(R=n-k-1)是2t个连续幂次的根a,a2,a3,…,a8对应既约多项式的最小公倍式。a是生成GF(213)的本原多项式p(x)=x13+x4+x3+x+1的根。对于2 KB/page的NAND FLASH,可保证纠16 b错误。

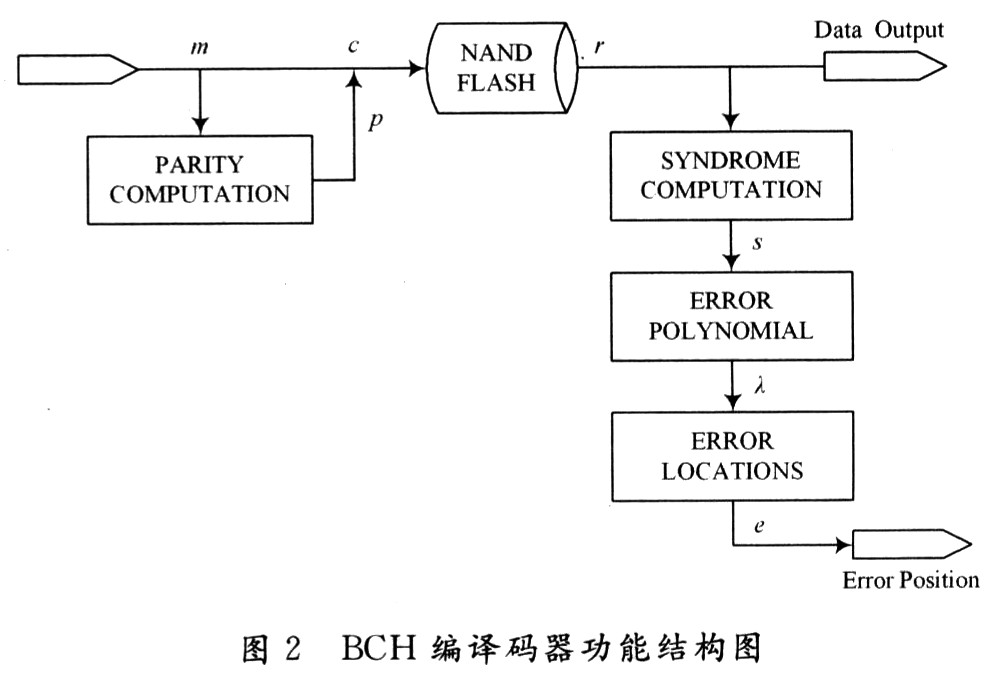

BCH编译码器结构图如图2所示。4 096 b数据先经过BCH编码(PARITY COMPUTATION)模块后得出4 148 b BCH码,再写入NAND FLASH,冗余位写入FLASH的spare area;读出时,将信息位和冗余位一起读出,若译码发现错误则产生中断,若错误数超过纠错能力则纠错失败,否则确定错误位,并由软件对该位取反即可纠错,若未发现错误则数据顺利读出。

2.1 BCH编码器

生成多项式G(x)得出之后,即可根据G(x)在GF(2m)上的除法电路实现编码。BCH码编码采用系统编码,这是因为系统码的前k比特的数据就是信息比特加上n-k个校验位就完成了编码,这使得编解码器的设计都非常方便,编码可以通过下式来实现:

![]()

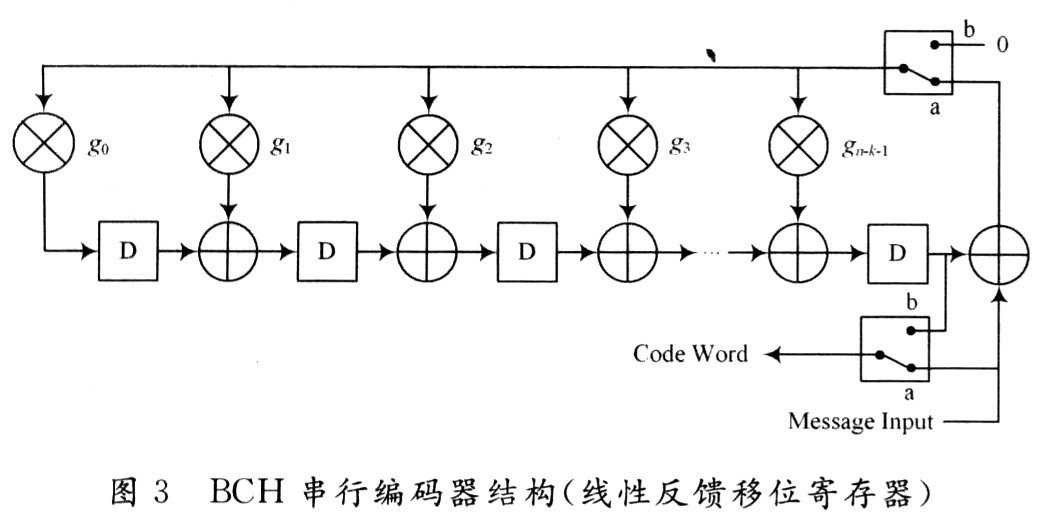

式中:m(x)和c(x)分别表示信息多项式与码字多项式;Rem(a(x))b(x)表示a(x)除以b(x)后的余数多项式。BCH系统编码器实现的关键是通过除法电路得到上式的余数作为系统码的校验位,如图3所示。

k比特原始信息数据由线性反馈移位寄存器最右边输入,在前k个时钟周期开关a闭合,信息位直接输出,在输出的同时,信号乘以x后送人线性反馈移位寄存器。前k拍结束时,线性反馈移位寄存器的内容就是余式。因此在后n-k个时钟,开关b闭合,输入接0,余数依次移位输出,从而得到冗余位。

2.2 BCH解码器

BCH码译码分为三个步骤:

(1)由接收多项式R(x)计算伴随式S(x);

(2)由伴随式S(x)得到差错位置多项式σ(x);

(3)由σ(x)根据钱式搜索得到差错位置数。

2.2.1 伴随式生成

接收多项式R(x)是码字多项式C(x)和差错多项式E(x)之和,即:

![]()

BCH译码首先由生成伴随多项式S(x)开始,也就是要求出其2t个伴随式Si

Si=R(αi)=E(αi), 0≤i≤2t-1

若与αi对应的最小多项式是φi(x),接收码多项式除以φi(x)的余式为pi(x),则有:

R(x)=qi(x)φi(x)+pi(x)

以x=αi代人,因为αi是φi(x)的根,所以φi(αi)=0。由此可得:

![]()

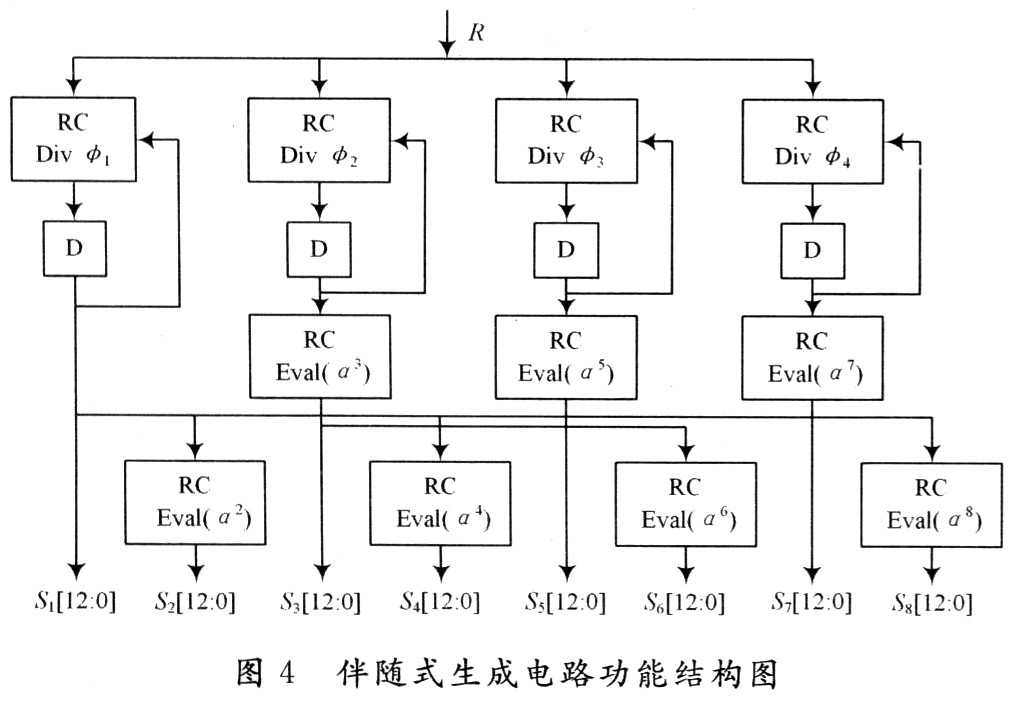

实现电路如图4所示。

由图4可以看出,通过R(x)除以若干最小多项式所得的余式来求伴随式,由于最小多项式φi(x)的次数低于生成多项式G(x),不需要2t个电路分别计算Si,可简化电路实现。

2.2.2 解关键方程

伴随式得出后即可进行下一步,求解关键方程:

![]()

其中:S(x)=S2t-1x2t-1+S2t-2x2t-2+…+S0是伴随多项式,![]() 是差错位置多项式,以差错位置数的倒数为根。

是差错位置多项式,以差错位置数的倒数为根。

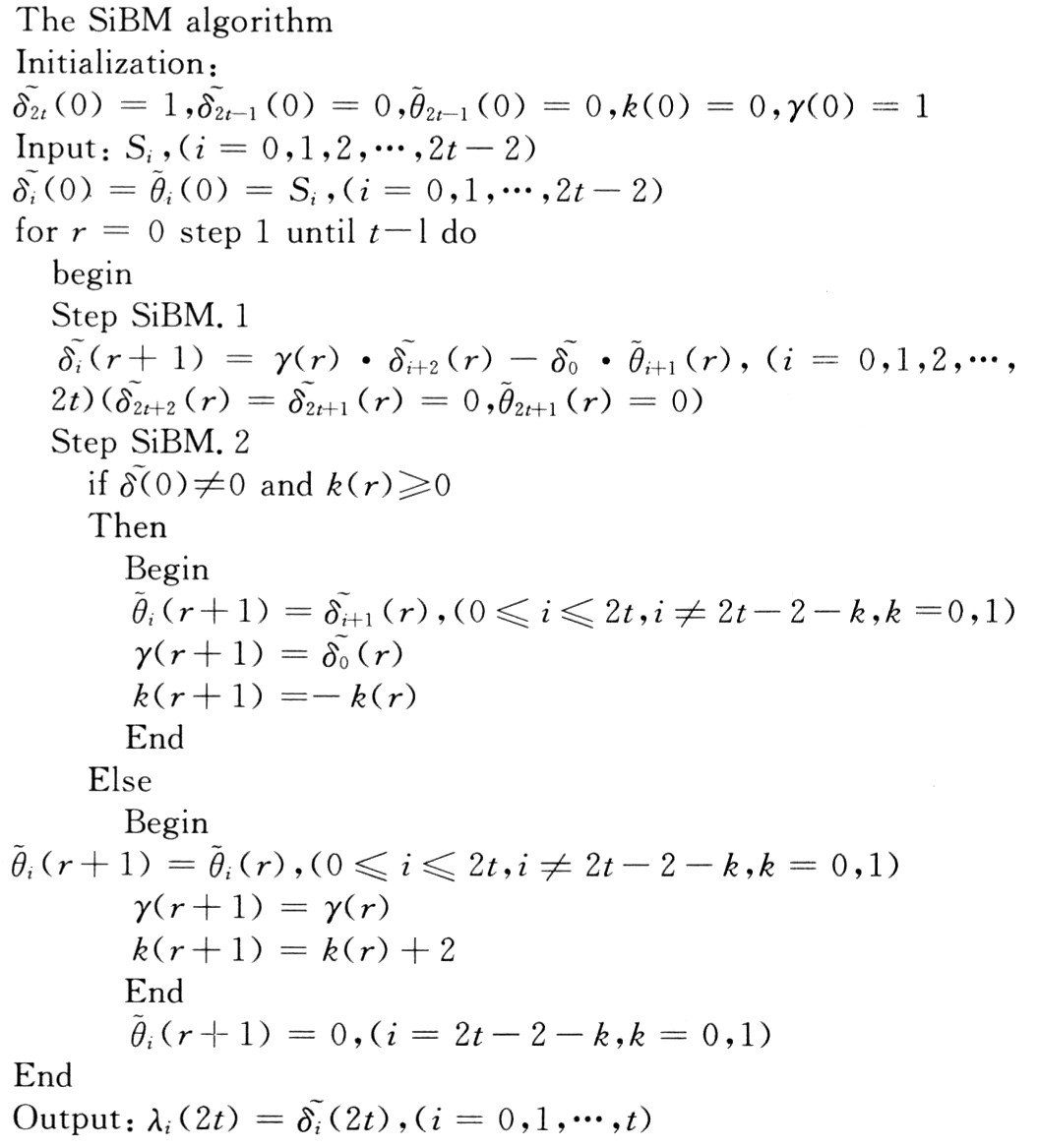

关键方程的求解采用经典的BCH应用译码算法——伯利坎普一梅西算法。传统的实现中涉及到有限域的求逆运算和求差错位置及差错图样的大量运算,成为硬件实现的关键路径所在。本设计采用一种简化的免求逆BM算法,其算法推导在文献[2,3]里有详细的描述,极大地缩短了关键路径,可以高效地实现差错位置多项式的根的求解。该算法利用二元BCH码的特点,即奇数次迭代时迭代差异为0,进一步节省了迭代周期,只需要t周期即可完成迭代。其电路实现采用可重配置的模块化和规则化的脉动结构电路实现,非常适合VLSI设计。其算法伪码描述如下:

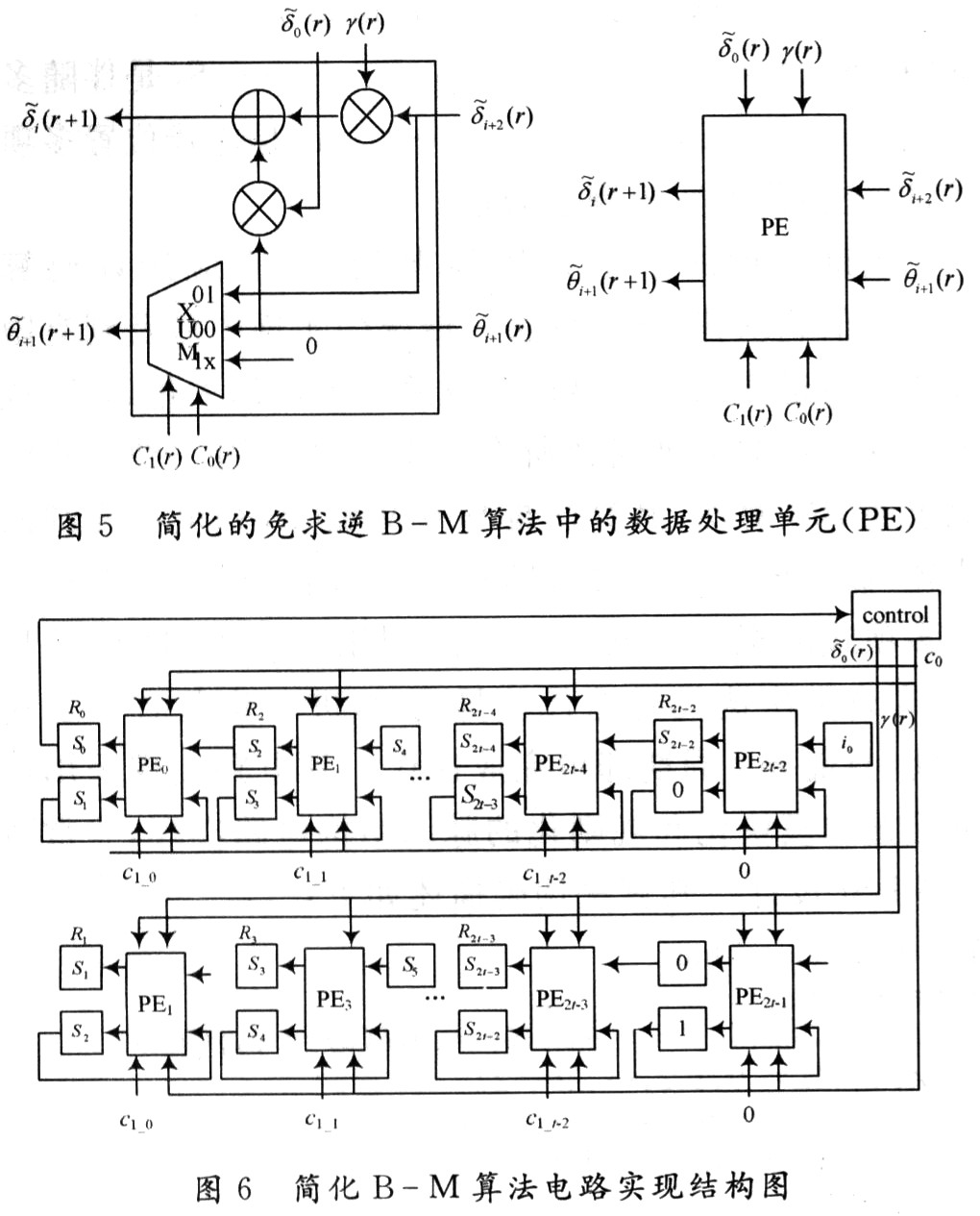

根据SiBM算法,在第r次迭代时,SiBM.1里第i个系数的更新可以和SiBM.2里的第i+1个系数的更新可以同时计算得到,一个SiBM处理单元PE如图5所示,可以同时更新Λ(r,x)的第i个系数和θ(r,x)的第i+1个系数。每个PE包含2个有限域乘法和1个有限域加法,还有一个m位多路选择器。SiBM算法可以由2t个PE和2t+1个寄存器实现,形成一个2t的阵列,如图6所示。

在PE模块里涉及到有限域的乘法,依据文献[5]中的公式和体系架构在本设计中引入了一种低复杂度并行结构的基于多项式的有限域GF(213)的乘法器,非常适合Verilog编码实现。

2.2.3 钱式搜索

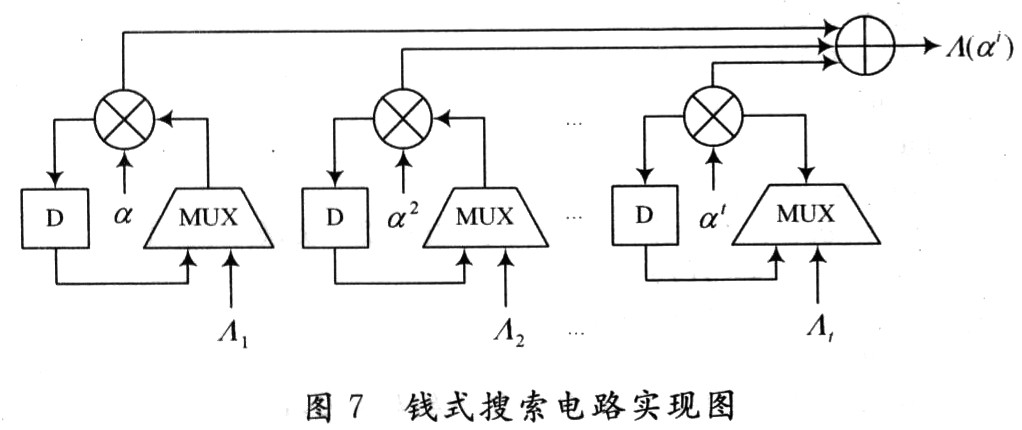

钱式搜索通过从高位开始的逐位检验Λ(α-i)是否等于O(O≤i≤2t-1)来搜索差错位置。假设从rn-1开始由高到低位输入,如果Λ(a-i)=0,那么ri有错误。电路实现如图7所示。

钱氏搜索通过“验根”的方法,从高位开始逐位校验、逐位输出,从而不必等全部差错数验算完毕再译码输出,大大降低了译码延时。当发现错误后,该错误位将保存到相应的寄存器,供软件提取错误信息。

3 测试结果

先后经过FPGA验证和芯片流片后板级测试,MLCNAND FLASH芯片选用三星的K9K2G08Q0M和意法半导体的NAND08GW3C2A,SLC NAND FLASH芯片选用东芝的TC58512FT,芯片频率为200 MHz,经过实测,在规范要求内的多种错误比特引入都可以成功纠正,当超过规范要求时会通过寄存器相应位显示纠错失败,在正常读写情况下可保证数据无误传输,在文件系统下的读写速度可达到2 Mb/s,满足系统需求。

4 结 语

讨论了支持MLC NAND FLASH的控制器的设计方案,着重论述了其中ECC模块的BCH编解码器部分的实现。该电路实现采用优化的算法,规则化的电路结构和模块化的设计思路,流片测试后证明功能无误,可以实现对当前主流MLC NAND FLASH的各种基本操作,并保证在设计预定纠错能力范围内的无误传输。今后将在此基础上进一步提高数据传输性能,采用更复杂的并行算法实现BCH编解码器部分,并探究在性能面积上的折衷。