在诸如Micron, Toshiba, STMicroelectronics, Intel, Chartered Semiconductor以及TSMC等众多制造商中,使用穿透硅通孔(through-silicon via)的3D集成技术已经呼之欲出。

本文的第一部分“3D集成电路将如何实现?”(《半导体国际》2009年3月刊)中,综述了用于制造3D叠层器件的众多可选方案。第二部分将探究那些正在进行3D穿透硅通孔(TSV)技术商业化的公司。

首次应用

传统的器件按比例缩减将在未来10-15年之内到达其自身物理极限,而在这段时间内,新型器件结构,比如碳纳米管(CNT)、自旋电子器件以及分子开关等,还不能发展到可被实际使用的水平。因此,在继续使用铜和低k介电材料进行集成的情况下,对器件和系统级组装方式的担心促使工业界的领导者们寻求更新的组装方法,以满足近期的需求。站在这类技术最前端的是3D集成电路,这一技术可以缩短互连长度,从而提高电路速度,降低功耗,并增加系统存储带宽。

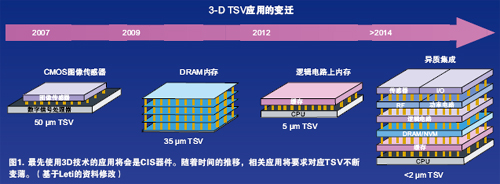

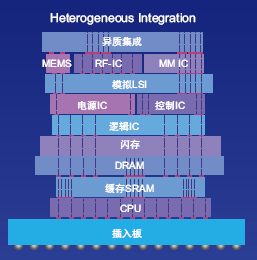

目前的3D IC集成被描述为一种系统级架构,内部含有多个平面器件层的叠层,并经由TSV在Z方向相互连接。最先的3D应用将会是CMOS图像传感器(CIS),接着是DRAM、逻辑电路上存储器,并在2014年之前在异质集成中获得应用(图1)。伴随这一过程,TSV尺寸将不断变小,而硅层厚度也将不断变薄。

图1. 最先使用3D技术的应用将会是CIS器件。随着时间的推移,相关应用将要求对应TSV不断变薄。(基于Leti的资料修改)

近几年,在不断增加的手机摄像头需求的推动下,传感器件的使用迅速膨胀。为避免使用传统的基于凸点的互连解决方案,CIS必须以正面朝上的方式组装。这样,允许这种取向(正面朝上)的TSV技术成为目前可获得的尺寸最小也是最具成本有效性的封装解决方案。CIS的成功已经使TSV技术获得了大量的商业化方面的关注。相似地,当逻辑电路上DRAM(正面对正面组装的芯片)键合被首次展示,并随后在2005年索尼的PlayStation和众多MEMS应用中商业化时,3D键合技术也成为了焦点。

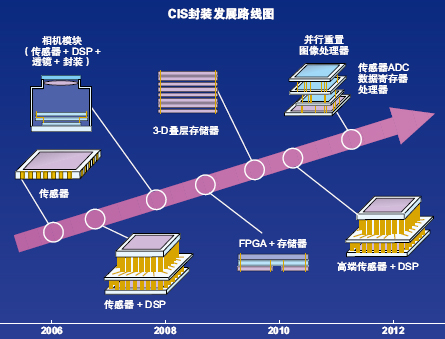

第一代CIS产品是基于圆片级封装(WLP)技术的,从芯片的背面刻蚀到达I/O焊盘获得TSV,然后进行背面的再布线。所有的发展路线图都显示,下一代这类产品将会与DSP键合在一起,从而获得真正的3D叠层结构,Oki/Zycube的发展路线图(图2)2即是其中一例。

图2. Zycube/Oki CIS封装的发展路线图表明,大部分服务器DRAM将需要使用TSV封装解决方案。(来源:Zycube)

在过去的一年里,对CIS TSV技术的关注明显增加,东芝宣称已具备了CIS TSV的制造能力3,Oki和新兴公司Zycube合作,计划2009年3月在现存Oki工艺线上实现每月10,000片的加工能力,STMicroelectronics宣称“在2008年六月底之前”实现量产4,而从Micron分离出的Aptina也声称其最新的CIS将使用TSV技术2。

未来需求

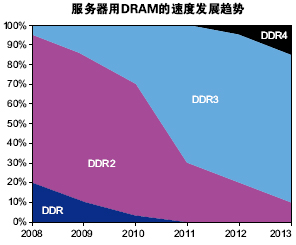

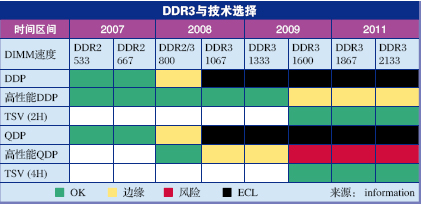

很明显,对速度的需求将决定在制造下一代叠层型存储器件中使用这一技术。到2009年,DDR3将需要采用速度超过1333 Mbps的DIMM封装,而据预测只有TSV技术可以满足这一要求(图3)。Micron的Kyle Kirby同意这一观点,他认为,“整个产业作为一个整体,Micron作为一个个体,将不得不转向3D TSV叠层技术来满足未来对DDR3和DDR4器件性能的要求” 5。IBM服务器部门的Biao Cai也同意这一观点6。而据预测,在2013年之前, 服务器用DRAM中的一大部分也将需要使用TSV封装解决方案(图4)。

图3.为适应DIMM的速度要求,TSV技术提供比目前其他技术更宽的边界。(来源:Micron)

图4.服务器用DRAM的高速趋势使得在2013年之前,大多数DRAM将很可能需要

使用TSV封装解决方案。(来源:Micron)

逻辑电路上存储器

传统的二维处理器架构,在同一芯片上包含L0和L1级缓存作为处理器核,而将L2级缓存放在另一个独立的芯片上。因此处理器核与缓存间的互连可能会比较长,在一些情况下,将导致在数据从一端传递到另一端之前经历多个时钟周期。

在未来多核处理器系统中,为避免这种速度问题所需的巨大带宽,很可能采用会缩短互连长度的TSV技术。这是为什么芯片与圆片叠层的技术很可能成为逻辑电路+存储器应用的最佳选择。使用该技术,不同尺寸的芯片可以叠层在一起,对微处理器和存储器的早期测试相对较为直接,而且允许使用已知良好芯片(KGD)。

这些优点使得芯片制造商如Intel同时关注逻辑电路+存储器的叠层和逻辑电路+逻辑电路的叠层方式,前者包括将缓存和主存叠层在高性能逻辑器件之上,而后者则是将一个完整的逻辑电路拆分到两个或更多的器件层上,将会需要使用比前者更小的互连节距。

举例来说,2006年英特尔展示了一个带有80核微处理器的300mm晶圆,采用TSV将处理器核与SRAM直接连接起来7,注意这里是TSV技术使得他们可以克服速度问题,并实现处理器与存储器间所需的信息传输速度。英特尔的CEO Paul Otellini介绍说,这些芯片将在5年之内实现产品化,并补充道:“TSV将会大大提高整个系统的性能,可能比在单芯片内包含80个核更有效”。TSV很可能会在很多英特尔的芯片中被使用,并不仅仅是“terascale”芯片。

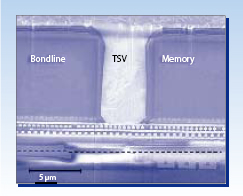

在已发表的工作中,英特尔已经展示了用于机械和电学连接的铜-铜键合技术。图5的剖面图是将一个SRAM芯片与一个处理器通过Cu-Cu键合在一起,并采用穿透10μm厚存储器芯片、尺寸为5μm的TSV连接起来。通过这种逻辑电路上叠层存储器的键合方式,英特尔将平均总线功率降低了66%,将DRAM叠层在一个92W的微处理器之上,最高温度仅升高约2°C。这是因为DRAM只消耗很小的功率,而且较热的处理器依然临近热沉(图6)

图5.该剖面图所示为英特尔的SRAM芯片与存储器采用Cu-Cu键合在一起,并通过一个5 μm尺寸的TSV连接起来。(来源:Intel)

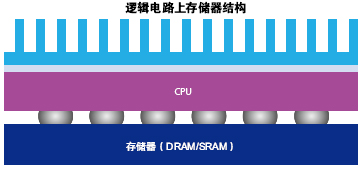

图6.本图展示了使用TSV的封装配置结构,CPU被叠层在DRAM/SRAM之上。(来源:Intel)

图7.一种用于异质集成的3D叠层方案,描述了相互不兼容技术间的集成。(来源:Zycube)

异质集成

3D架构从包含DSP、SRAM、DRAM等具体功能芯片的圆片开始的。这些圆片经由减薄、对准并垂直连接(芯片对圆片或者圆片对圆片)在一起,成为一个具有整体功能的器件。由于可以集成互不兼容的工艺,3D概念在性能、功能和尺寸上具有巨大优势。在一些分支领域,这被称为“异质集成”,图7为这一概念的示意图。其他还可以添加的器件包括叠层的天线、传感器、电源管理和能量存储器件等。

举例来说,我们都知道在所有手机中,功率放大器都是使用GaAs工艺制造的。而在实际上,只有很少几种电路需要使用GaAs工艺。3D集成将允许这些小块的GaAs电路键合在CMOS电路的上面,构成一个完整的电路。这也会在本质上降低成本。这一技术具有很强的军用背景,实际上在军事领域被称为COSMOS(compound semiconductor on silicon,硅上化合物半导体)技术。9

不断演变的基础架构

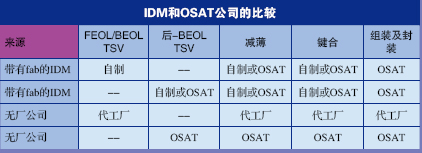

可以采用若干种不同的路径,将3D IC集成转化成目前存在的基础架构。举例来说,拥有制造工厂的IDM公司可以在前道互连(FEOL)、后道互连(BEOL)或者后-BEOL阶段进行TSV的制作,同样也可以完成减薄、对准及键合等步骤。这些公司也可以仅仅在自己工厂里制作完成TSV,然后将圆片出售给具有传统外包性质的半导体组装和测试供应商(OSAT)来进行后续的减薄、键合及封装工序。

尽管没那么方便,无制造工厂(fabless)的公司同样也可以在其他工厂中完成FEOL和BEOL型TSV的制作,并在OSAT提供商或者制造厂中实现减薄及键合工序。如果需要后-BEOL型TSV,则全部工作都可以由OSAT提供商完成。

蓄势待发

制造工厂在实际行动上落后于TSV技术。去年,特许半导体和Tezzaron联合宣布,特许将增加应用Tezzaron的TSV技术。10而台积电(TSMC)也紧跟需求,负责后道技术的高层主管T.W. Karta在2008年公布了“量产技术”,对应TSV的节距为140 μm,这一尺寸将在2009年降到60 μm,而到2010年将降到17 μm。11

类似的,OSAT供应商正在为生产订单做准备。在2007年,Amkor宣称与IMEC合作,共同开发3D集成技术,12而且他们的3D技术路线目标是在2008-2010年间,进行存储器+存储器以及存储器+逻辑电路的叠层。13此外,Amkor已经详细公开了针对铜和钨TSV进行减薄及键合的工作。

2007年还看到其他的一些OSAT公司进入这个领域:ASE的CTO Ho-Ming Tong宣称,ASE正在使用TSV进行3D集成方面的研究工作,预测将在2008-2011年期间开始45 nm工艺节点实现量产。10另外,STATS ChipPAC宣告收购了Schott玻璃公司的CMOS成像芯片封装部门,包括在这一部门中进行的3D TSV技术的开发研究成果。10

最可能的情况是,制造工厂将在前道工艺中完成TSV,而OSAT公司将进行后续的工序,包括减薄、键合及背面工艺处理。14

除了器件制造之外,设备和材料供应商也是3D基础架构正在成长的一部分。在2006年,一些设备制造商、材料公司和技术研究机构联合在一起,组成一个国际性的联盟,称为EMC-3D。这一联盟的既定目标是通过展示成本有效的、制造可行的、可叠层的TSV互连技术,来拓展3D市场基础架构,他们的目标是在第三年将拥有成本(CoO)降低到每圆片$200。15这一组织包括EV Group、Alcatel、Xsil、RHEM、Enthone、Honeywell、AZ和Brewer Science。另外一个可宽松加入的设备小组开始于2008年,其主要成员包括SUSS MicroTec、NEXX Systems以及Surface Technology Systems (STS),该小组也聚焦于提供低成本3D集成解决方案。5

加速发展的信号

展望未来的若干年,3D IC集成技术表现出即将商业化的姿态。要注意观察FPGA和电路设计方面的动态,并特别关注三星和英特尔的动向,这其中的任何一个都必然会成为整个发展曲线的加速信号。

在电路设计方面,尽管已经可以从一些诸如R3Logic的关注该领域的公司获得具体的软件,但Cadence和Mentor Graphics等大型设计公司显示,他们还没有真正认同工业界将“朝这个方向发展”。13,16这些EDA提供商中任一个的决定,都会成为3D技术加速发展的另一个重大指示信号。

FPGA经常存在互连延时方面的问题。3D集成可以消除逻辑块层中的可编程互连,而将其放在叠层体的另外一层,从而降低互连延时,提高FPGA的性能。因而,由于其自身重复性的结构特点,FPGA很可能会比其他逻辑芯片更快地选用3D体系结构。从概念上来说,存储器也会被增加为3D叠层的一部分。

三星是DRAM、NAND、CIS和手机等市场领域的主导者。他们展示的DRAM和NAND叠层样品芯片同样也证实了他们还是3D TSV技术的主导者。该公司CEO在2006年IEEE主办的国际电子器件会议(IEDM)上宣称:“存储器、逻辑电路、传感器、处理器和软件等的集成将基于芯片叠层的3D技术”。然而,三星还未曾宣告其3D集成的商业化,而是将全部商业化信息冻结在内部。一些分析家推测,这家芯片制造商将不声不响地在其自己的手机产品中使用3D叠层技术,在取得成功之前不会做出任何宣告。17很明显,三星的官方说法将会促使整个工业界获得更快的商业化发展步调。

在2007年半导体集成和封装3D体系结构会议上,英特尔的Jerry Bautista评论说,他们已经不存在任何技术难题,只要产品小组决定好将该技术放入何种产品,英特尔就会立即将其3D集成技术商业化。18由于该技术已经多次在英特尔设计者论坛中被着重关注,而且该公司也已经发表了很多技术论文,论及在多核处理器技术中开发3D电路集成技术的巨大需求,因此整个世界都在等待英特尔通过某款产品的公告来扣动扳机,给3D集成技术带来一记更有力刺激。

结论

种种迹象表明,3D IC集成技术将被普遍采用,成为解决传统器件按比例缩减过程中面临问题的短期方案。这一架构的各个层面都在进步,特别是对技术的集成,以及进一步降低成本使其可以为主流技术采用。对于微电子工业来说,未来几年将可能会非常令人兴奋。