最近在引线上流体(FOW)技术方面的进步,包括FOW膏和薄膜,使得封装工程师可以设计更薄的封装,减少制造工艺步骤并降低总的封装成本。

为满足当今的应用要求,传统的单芯片IC封装设计,逐渐被更加复杂的多芯片封装方案取代。在产品功能更多、性能更高、成本更低的趋势下,封装工程师使用叠层芯片型芯片尺寸封装(SCSP)或类似的封装形式,在与传统单芯片封装体同样尺寸的前提下,可以提供更高的性能。SCSP将2个或者更多的IC,比如ASIC和存储器(SRAM和DDR),放进一个封装体中,基本加工步骤包括:首先叠层对应芯片,然后通过引线键合连接起来,最后通过模塑操作得到标准封装体(图1)。这些封装与非叠层封装相比,具有更小的尺寸和更低的外形。它们与单一封装的芯片或其他三维封装相比,成本更低。

图1. 叠层芯片型芯片尺寸封装,在一个单一的封装体中包含2个或更多的IC,基本加工步骤包括:首先将芯片叠层,然后通过引线键合的方式连接它们,最后通过模塑操作获得标准封装体。

目前已经发表了很多关于叠层芯片封装设计的工作,包括芯片版图和引线键合优化策略,薄芯片处理工艺以及电学/RF性能优化。然而,在叠层芯片封装中使用的封装材料通常还未得到很好理解。在这些复杂IC封装中使用的每一种材料都会与其他材料相互反应,形成界面和应力,并影响整体的封装性能。此外,材料系统在封装器件的成本和制造工艺复杂性方面都是重要的影响因素。为了最小化重新设计或重新制作的成本,针对封装在设计阶段就选择好正确的材料系统至关重要。

本文*主要讨论用于叠层芯片封装的芯片粘结技术,通常称作引线上流体(FOW)技术,芯片放置之前或者放置过程中,在各个芯片间应用粘结膏。FOW芯片粘结材料可以提供芯片间的低应力结合,在引线键合过程中保证芯片在对应位置上不发生移动。它还用于控制叠层中芯片间的空隙高度,避免不同芯片间引线键合的相互挤压。大约10年前通过使用支撑填充芯片粘结膏首次展示了FOW技术。前不久,又出现了FOW的薄膜形式,可以使芯片键合工艺变得更加简单。

叠层封装所用材料

在第一款SCSP的开发早期,工程师们发现,传统的芯片粘结膏不能满足这一新型IC封装的要求。特别的,传统环氧基芯片粘结材料的高模量值,以及这些材料中使用的摩擦性填充物阻碍了它们在叠层芯片间的应用。在叠层芯片封装体内,拥有较高模量的芯片粘结材料会引起较大的应力,从而导致芯片碎裂或者脱开。在非导电芯片粘结中使用的典型填充物比较坚硬而且具有摩擦性,会在芯片放置工艺中摩擦芯片有源面的表面钝化层,从而引起电失效。因此,在叠层芯片间使用低应力且无摩擦性的芯片粘结材料,可以降低芯片间应力,由芯片粘结摩擦引起的钝化层损伤也可以被忽略。

这些材料在金字塔型芯片叠层IC方案中得到成功应用。然而,对于相同尺寸的芯片叠层方案,还需要额外的键合引线控制以保证在安放顶层芯片过程中底层芯片上引线键合不致被损坏。考虑到这一原因,开发了支撑填充型FOW粘结膏材料。

早期的这类芯片粘结胶中含有玻璃珠,可以充当支撑体,提供必要的间隙和芯片倾斜控制。然而,这种硬质的玻璃支撑体是不可压缩的,会形成微小应力点从而导致芯片钝化层损伤。最新一代的支撑体技术使用有机塑料珠。这些塑料珠与硬质的玻璃珠充当同样角色,功能一致,又是柔性的,可以被压缩从而不会引起芯片钝化层损伤。

传统封装的相同尺寸芯片叠层使用非功能芯片放置在功能芯片之间,以保证约4mil的键合引线高度,与此相比,支撑膏可以提供更高的制造工艺效率。非功能芯片方案方式需要额外的工艺步骤,包括芯片粘结膏涂敷、芯片粘结和额外的固化过程,这些都会增加成本且降低产能。通过使用支撑体填充膏,避免了额外工艺步骤的使用,整体的封装体高度也得到降低。而且,建模分析表明,使用同尺寸支撑体代替非功能性芯片降低了芯片粘结材料中的最大应力。

用于处理薄芯片的DA薄膜

大多数叠层芯片封装需要晶圆减薄技术。没有支撑的薄晶圆在多个电路薄膜层和厚钝化层的应力影响下会发生弯曲和卷曲。在线晶圆减薄时,使用胶带支撑晶圆来更好地控制工艺,并将操作过程中损坏的可能性降到最低。这一过程包括两步背面研磨工艺,即粗研磨和精研磨,研磨之后接着进行机械抛光操作,去除掉厚度约为2μm的硅损伤层,并消除相应残余应力。

同样的线上加工系统可以经由一个转轴在晶圆背面粘贴一层20μm厚的芯片粘结胶带薄膜。这一技术,被称作“划片用芯片粘结胶带”或DDF,可用于处理50μm厚甚至更薄的晶圆。由于DDF对芯片边缘粘结胶形貌的控制和键合界面厚度的控制较好,因此DDF代替了传统的芯片粘结膏被应用于叠层封装中。然而,DDF材料不能应用在引线键合之上,其应用被限制在金字塔型叠层或台阶型叠层芯片结构中。

最近,为了采用叠层型芯片粘结胶带,并实现同尺寸芯片叠层,引入了FOW薄膜材料。FOW薄膜与划片用胶带结合使用,类似于DDF。当使用FOW薄膜时,晶圆首先被层叠在FOW薄膜上,然后进行划片、紫外固化(如果划片用胶带是UV型的),最后拾取并粘结上对应芯片。在芯片拾取过程中,芯片键合薄膜与划片胶带间的释放和分离至关重要。另外,芯片放置速度和压力将决定FOW的总体使用成本。FOW设计为具有流动性,可以在底层芯片的引线键合之上流动。该材料消除了对支撑硅芯片或者交错有序芯片的需要。

FOW薄膜的很多材料特征都可能影响封装的性能和/或工艺要求。大多数特征与DDF和/或FOW膏相似,只有很少的一些特征会有显著区别。首先,FOW薄膜包覆叠层芯片封装的引线键合,而典型的DDF却非如此。因此,芯片粘结薄膜的热机械性能以及离子净化性能会影响薄叠层芯片的性能。若FOW薄膜非离子稳定,偏置HAST或者潮湿环境将会引起腐蚀问题。其次,这种薄膜的粘性和弹性特征使得可以在不改变引线键合形状、不让引线交接的前提下,将薄膜放置在引线键合上面。

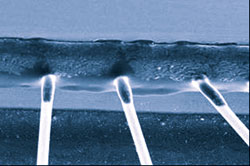

图2是在叠层封装内部使

图2. FOW薄膜必须在引线键合周围流动而且不引起机械变形。

用FOW薄膜包覆键合引线之后的照片。与DDF类似,FOW薄膜应在引线键合工艺中处理,并避免固化操作以将工艺步骤降到最少。

FOW的工艺考虑

FOW膏和薄膜材料的使用,可以避免同尺寸芯片叠层封装中非功能芯片的使用。正如前面所描述的,FOW膏和薄膜技术避免了叠层封装中非功能芯片的使用需要,从而降低了叠层芯片制造工艺的整体复杂性(图3)。

图3. FOW膏消除了非功能芯片的使用。FOW薄膜避免了芯片粘结胶的涂布工艺。压力敏感的FOW薄膜避免了芯片粘结剂的固化步骤。

FOW膏技术避免了与非功能芯片放置相关的工艺步骤。FOW薄膜的使用进一步消除了芯片粘结胶涂敷和固化的步骤。FOW技术使用现有的芯片抓取和放置设备,从传统的非功能芯片型叠层设计转变成FOW叠层设计,不需要追加任何基础设施更换的投资。

与传统的芯片粘结工艺相比,FOW技术提供更好的键合引线和芯片倾斜控制。FOW膏所用支撑体的低误差值以及FOW薄膜厚度的低误差值,可以保证精确的、可重复操作的键合引线和倾斜控制。

JEDEC性能

为评测FOW薄膜材料的JEDEC性能,测试了分别使用两种不同FOW薄膜技术的双芯片叠层CSP,其中一种FOW薄膜需要使用烘箱进行固化操作,另一种FOW薄膜采用了压力敏感释放机理,不需要任何固化步骤。

在这两种情况下,FOW薄膜在双芯片CSP结构中表现都很好。在第一种情况,使用了烘箱固化型薄膜,在使用很低的放置压力前提下,材料表现出接近无孔洞的性能。此外,没有蠕变,没有引线损伤,而且表现出很好的BLT控制性能。在这种情况下,需要在175°C的温度下对芯片粘结材料固化1小时。这一封装通过了JEDEC第II级260°C的要求,并且在芯片放置之后,没有任何引线交接,在引线键合底部也没有任何孔洞形成。在这一分析中,使用了80μm厚的薄膜,对应引线弧高度为70μm。由于FOW薄膜厚度可在50-80μm变化,所开发的这一工艺可以应用于很多不同的FOW薄膜厚度和键合线弧高度的情况。建议所用的薄膜到线弧的高度差异是10μm(薄膜要比线弧高度厚10μm)。

在这一实验中,使用了80μm厚的FOW薄膜和75μm厚的芯片。叠层用芯片尺寸为250×300μm,金线直径为1mil,引线线弧高度为70μm。对应CSP的外形尺寸为12×12mm。结果显示,在芯片放置之后,键合线弧下面存在一些交接的引线(图4)。然而,声学显微分析表明,在模塑工艺中,这些交接的引线被去除了。情况2中叠层CSP通过了JEDEC第II级260°C潮湿环境测试以及JEDEC情况B的热循环测试(2000次循环)和HAST 168小时暴露测试。

图4. 芯片放置之后在键合线弧底部观察到交接引线,但它们在注塑过程中被去除。

结论

为保持价格竞争性和生产效率,使用现今复杂封装的企业需保证对产能造成最小影响。随着消费者对小尺寸、高功能性产品的需求,封装设计者必须将超薄芯片集成入叠层芯片CSP中,这使得保持产能变得更具挑战性。研究结果表明,新型FOW技术是获得高可靠、高产能并具价格竞争能力工艺的最有效手段。使用这些下一代材料,可以在使用更少工艺步骤的前提下获得更薄的封装,这将大大降低基础设施资金投资和总体制造成本。