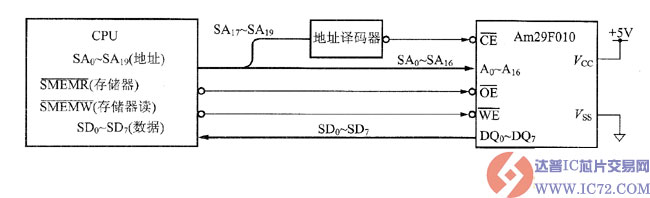

图1 8位CPU与闪速存储器的连接思路

进而OE与SMEMR信号、WE与SMEMW信号相连,DQ0~DQ7连接于CPU的数据总线。

该图中特意考虑到时序的关系。根据CPU的总线工作时间,或者需要仔细计算时间,或者使其等待、延长总线周期等。ISA总线与近期的闪速存储器工作等相比,其速度是足够缓慢的,所以该图可以在添加缓冲器的电路中工作。

如果CPU的数据总线超过8位(16位或者32位宽等),则需要排列若干个闪速存储器。但是一般的CPU即使数据总线具有16位或者32位,作为命令一般设计时也是以8位为单位进行输入输出的。为了适应这样的命令,一般CPU的外部数据总线也以8位为单位进行分组,并且设计了在读写时标明存取所对应的分组信号。

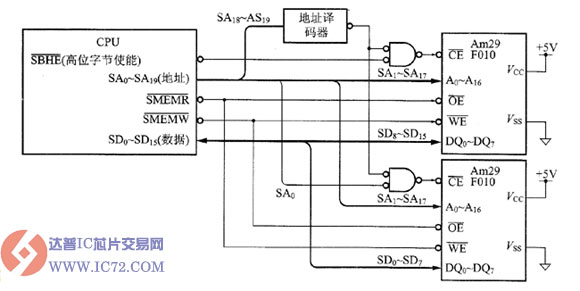

以图2为例,表示在16位的CPU中连接了2个Am29F0l0的电路。这里的信号种类与名称是以ISA总线为基准的(事实上在ISA上进行16位的存取需要使MLMCSl6有效,在此省略)。与前图相比,我们知道增加了SBHE信号,该信号用于表示是否使用数据总线的高8位,对低8位的访问是由A0确定的。表总结了ISA总线上存取操作与A0、SBHE信号的操作。信号名存在若干不同,但处理器基本上都采用相同的方法。

图2 16位CPU与闪速存储器的连接思路

表 在16位总线上的存取操作实例

注:进行由奇数地址的字存取时,是分割奇数地址与偶数地址的字节存取(2次存取)来运行的.

由此表我们知道,由于A0与低位字节的选择信号等价,所以地址偏移一个,将A1~A17赋予了闪速存储器。当地址一致、A0为低电平时,低8位的闪速存储器的面有效;当SBHE为低电平时,高8位的闪速存储器的CE有效。

上述的例子为16位的CPU。在32位以上CPU的情况下,没有A0及A1,而是准各了以字节为单位的使能信号(大多命名为BE0,BE1,BE2,BE3等名称)作为替代。