可编程器件及其技术自20世纪90年代以来得到了迅猛发展,他促进了逻辑设计的概念和方法以及数字电路实现手段的转换。ISP技术消除了传统可编程逻辑器件(PLD)的某些限制和连接弊病,可以在电路板上直接进行编程和重复编程,有利于在板和系统级设计、制造及编程,根据用户和市场需求进行产品开发,从而有效地降低了产品成本,缩短产品进入市场的时间。Lattice公司的ISP器件可由该公司的ispDesignExpert软件所支持,且能够在系统电路板上直接进行重构,因而无需单独的编程器即可在桌面上进行电路的仿真、测试和查错等工作,迅速地改变原电路和更新系统的性能,完成设计。

1 HDB3编码基本原理

为了满足基带传输的要求,单极性脉冲序列必须经过适当的基带编码,以保证传输码型中无直流分量,有一定的自检能力和适应不同信源的统计特性的能力。在基带传输中,常用的码型有:传输极性交替码(AMI码)、三阶高密度双极性码(HDB3码)、4B3T码、传号翻转码(CMI)以及双相码(Manchester码)等。

1.1 HDB3码的构成规则

首先简单介绍AMI码的构成规则,把单极性脉冲序列中相邻的"1"码(即正脉冲)变为极性交替的正、负脉冲,将"0"码保持不变,把"1"码变为+1、-1交替的脉冲。

HDB3码是一种AMI码的改进型,又称四连"0"取代码。在AMI码中,如果连续较长的一段序列为"0"码,则在接收端会因为长时问无交替变化波形的控制而丢失同步信号。为克服传输波形中出现的长连"0"的情况,设计了AMI码的改进型HDB3码,其码型中最长连"0"数不超过3个。

HDB3码的编码原理可简述如下:在消息的二进制代码序列中,当连"0"码的个数不超过3时,HDB3编码规律与AMI码相同,即"1"码变为"+1"、"-1"交替脉冲;当出现4个及以上连"0"码时,把连"0"段按4个"0"分节,即"0000",并使第4个"0"码变为"1"码,用V脉冲表示,这样就可以消除长连"0"现象。为了便于识别V脉冲,必须使V脉冲极性与前一个"1"脉冲极性相同,这样就破坏了AlMI码极性交替的规律,所以V脉冲为破坏脉冲。把V脉冲和前3个连"0"称为破坏节"000V",为了使脉冲序列仍不含直流分量,则必须使相邻的破坏点V脉冲极性交替,为了保证上述条件成立,必须使相邻的破坏点之间有奇数个"1"码。如果原序列中破坏点之间的"1"码为偶数个,则必须补为奇数,即将破坏节中的第一个"0"码变为"1",用B脉冲表示,这时破坏节变为"B00V"形式。这样就保证B脉冲极性与前一"1"脉冲极性相反,而B脉冲极性和V脉冲极性相同。

1.2 HDB3码的特点

其特点主要有:

(1)与AMI码一样无直流分量,且低频分量也很少;其功率谱也与AMI码类似,其方波中丰富的高频分量同样被消除了;

(2)由于引入取代节,因而解决了AMI码在连"0"过长时提取位定信号的困难;

(3)具有内在检错能力。

由此可见,HDB3码是一种优良码,目前广泛应用于基带传输接口码。

2 ISP技术在HDB3编码中的应用

2.1 用ISP实现HDB3码编码

2.1.1 编码设计思想

HDB3码为三阶高密度双极性码,其编码设计思想为:

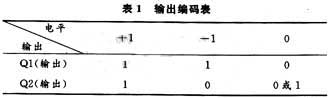

(1)由于ISP不能输出负电平,只能输出"1"、"0",所以先要对他的输出进行编码,如表1所示。

(2)考虑将某些"0"改为"1"。用一个四位移位寄存器来对输入的序列进行检测,当检测到4个连0时,将其第四个0改为1。再设置一个T触发器来检测两个相邻的破坏节之间"1"的个数,若T触发器为"0",则说明两个相邻的破坏节之间"l"的个数为偶数个,需要将第2个破坏节的第一个"0"置"1",若T触发器为"1",则说明两个相邻的破坏节之间"1"的个数为奇数个,不变。

(3)正、负号的考虑。除了破坏节的V即"1"的符号与他前面最近的"1"的符号相同外,其他的"1"的符号都是正、负交替的。所以再设置一个T触发器,当他检测到"1"时就使Q2翻转。当然,这样就不可避免地使破坏节的V的符号也出现翻转,为了防止他的翻转,用一个三位移位寄存器来跟踪V码,以保证V码的符号与他前面最近的"1"的符号相同。

2.1.2 编码流程图

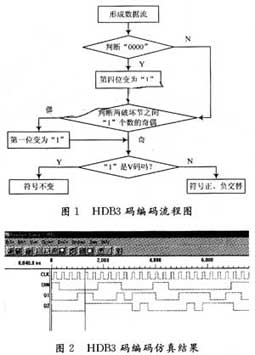

编码流程图如图1所示:

2.1.3 编码程序仿真结果

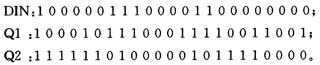

仿真结果说明:由于输入的数据流经过了5个寄存器,输出就延长了4个时钟脉冲周期,所以仿真输出的有效起始位置应该是4个时钟脉冲以后(即图2上的黑线以后的部分)。

对照上面的仿真图,可以得到:

根据前面所提编码表格1,当Q1Q2=11代表"+1",Q1Q2=10代表"-1",Q1Q2=00或01代表"0",则输出Q1、Q2可翻译成:

+1000+10-1+1-1000-1+100+1-100-1

以上结果完全符合}tDB3码的编码规则。

2.2 用ISP实现HDB3码译码

2.2.1 译码设计思想

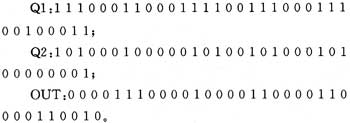

(1)由HDB3码的编码规则可知,"0000"都被"000+1"或"000-1"或"+100+1"或"-100-1"取代,故只要能检测出"+1000+1"、"-1000-1"、"+100+1"、"-100-1",将他们分别改为"10000"、"10000"、"0000"、"0000"即可。

(2)、当然"+1"、"-1"、"0"还是由Q1Q2来表示,那么就需要有两个5位移位寄存器(c和d),Q1通过d,Q2通过c。通过d、c来检测。如果检测到两个移位寄存器分别为"10001"、"0xxx0"或"10001"、"1xxx1"或"1001x"、"1xx1x"或"1001x"、"0xx0x"("x"代表任意,即可以是"1"也可以是"0"),数据输出是将d里面的数据流输出,所以只要将d中所检测到的以上数据分别改为"10000"、"10000"、"0000x"、"0000x",就可得到HDB3码的译码了。

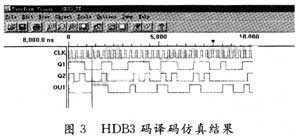

2.2.2译码仿真结果

对应译码结果为:

3结 语

随着可编程技术及器件的迅速发展,当今硬件设计日趋软件化。为适应社会发展与需求,作者进行了基于ISP技术的研究与应用,采用软件设计思维,将原理图与程序仿真相结合的方法,实现了HDB3的编码和译码功能。