1. E5的特点及体系结构

E5是位于美国硅谷的公司Triscend 推出的一款全新的CPU,它是基于8051的内核,但将微处理器的内核,ASCI及可重构逻辑阵列集成与一体,构成一款CSOC(可配置系统)芯片。Triscend E5的主要特点有:

1.1 它的主控制器是一个增强型的8032,与工业标准的8051指令上完全兼容。

1.2 它包含一个嵌入式的可重构系统逻辑矩阵(CSL)。共有2048 个可配置系统逻辑(CSL)单元(约40000 个逻辑门)。

1.3 拥有一个高性能的系统总线(CSI),连接微处理器,存储器和可重构系统逻辑矩阵。

1.4 增加了一个存储器接口单元(MIU),负责连接外部存储器。

1.5 片上64k 字节的系统专用RAM(XDATA RAM)

由此可知,E5的主要部件是:8032增强型CPU,可重构系统逻辑矩阵(CSL),内部系统总线(CSI),片上64KRAM,可编程I/O口以及一些专用外设。

2. E5存储区的映射关系

E5内部含有64K的SRAM供数据存取之用,但不含ROM。因此须接以External Memory供程序运行。在使用E5的系统中,E5可以从Internal RAM或External Memory中取得指令运行。一般情况下,E5从External Memory中取得运行指令,而External Memory一般为FLASH。

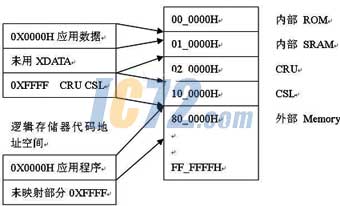

E5使用增强型的8051内核,其逻辑寻址能力遵循8051的规则,即逻辑地址上CODE、XDATA区各64KByte。在传统的8051系统中,指针DPTR可利用指令MOVC、MOVX分别寻址CODE、XDATA的64KByte。但E5利用其MIU(Memory Interface Unit)将实际物理寻址范围作了极大的提升。在使用E5的系统中,合理利用TRISCEND提供的地址映射器CMAP、DMAP,使得寻址范围达到32位的物理地址空间。图1为逻辑地址空间与物理地址空间的映射关系。

图1 E5逻辑地址空间与物理地址空间的映射

从图中可知E5的物理地址划分如下:

0000_0000~0000_FFFF Primary Initialization Code ROM(初始化代码ROM空间)

0001_0000~0001_FFFF Internal RAM(内部RAM空间)

0002_0000~0002_FFFF Configuration Register Unit(可配制寄存器单元)

0003_0000~0003_FFFF CPU Debug Registers(CPU仿真寄存器)

0004_0000~0007_FFFF Initialization Memory(初始化存储器空间)

0008_0000~0009_FFFF Reserved(保留空间)

0010_0000~007F_FFFF CSL-based Soft Module Registers Decoded via Selectors(软件IP库寄存器空间)

0080_0000~00FF_FFFF External Memory(外部存储器空间)

下面再分析实际使用中FLASH MEMORY的空间分配问题。

在本文利用E5所设计的应用系统中,使用29LV800BA-90PFTN,作为External Memory程序存储器。它的容量是8M (1M * 8/512K * 16)BIT,并以64K分段(SECTORED)。它的段(SECTOR)空间与E5的物理地址的对应关系如图2所示。

图2 Flash段空间与E5的物理地址

在实际应用中,FastChip自动将E5 CSL数据存放在FLASH的SA12,如果这部分数据需要占用的空间超过64KByte,则向后继续占用SA13,并依此类推;其余SA0~SA11作为程序代码存放区。实际上程序代码所需要的存储空间并不是总需要那么大,多数情况下甚至少于64KByte。因此我们可以将FLASH中的部分区域划做数据存储,用于保存需要在掉电或硬件复位后可再恢复的数据。

3. FLASH 做DATA MEMORY的说明

使用FLASH中的部分区域作数据存储,必然涉及到数据的改写。对FLASH而言,在进行数据改写时,必须先将该数据所在的SECTOR完全擦除(ERASE),然后再执行写(WRITE)操作。受FLASH操作的限制,在对FLASH进行EREASE、WRITE操作时,相应部分功能程序代码不可能从FLASH内取得,所以必须预先将它们转移到适当的位置(SRAM),以保证读、写FLASH的程序正常运转,完成这一部分操作完成后,可以恢复从FLASH内取得程序代码继续执行其他功能。

在这些应用中,内部SRAM由CODE与XDATA地址空间共享。E5内部有一定容量(64K)的SRAM,故可以从SRAM取得程序代码完成规定的操作。但是这个RAM的容量有限(具体:E502-8KByte,E505-16KByte,E512-32KByte,E520-40KByte),而且SRAM本身还必须预留足够的空间作为中间数据的存放,所以转移到RAM的程序代码应该尽可能精简。

要E5完成对FLASH中部分区间的数据改写,最少必须具有以下两个功能:将程序代码区的内容转移到内部RAM区;完成对FLASH的ERASE、WRITE。

3.1 程序代码转移

按照设计要求,被转移的程序代码所完成的功能是操作FLASH。为保证该部分代码转移至E5内部RAM后能正确运行,代码的绝对起始地址应该为0。

这部分代码应该利用FastChip的CODE BANK存放在单独的BANK内。如一般功能应用程序占用BANK0~N,则这部分代码存放在BANKN+1。

进行程序代码转移时,需要确定的参数包括:被转移程序代码的首地址、被转移程序代码的长度、被转入区间的首地址。在进行该项工作之前,确认改变地址映射器的设置不会导致程序运行的混乱。

3.2 Internal RAM区块说明

改写FLASH的功能代码必须在Internal RAM运行,而且起始地址必须是0000,因此,在设计时,Internal RAM的低段区域不要用来保存数据,我们设定该区域长度为4KByte,地址范围0001_0000~0001_0FFF。即其它数据的存取在0001_1000H之上。

3.3 地址映射

为将FLASH区域内的功能代码转移到Internal RAM指定的位置,我们设置地址映射器来分别指向:

设置地址映射器DMAP2,使保存有改写FLASH的功能代码的FLASH之SECTOR的地址映射至XDATA区的0000~0FFF。映射器DMAP2各寄存器设置如下:

DMAP2_TAR_0ß0x00 ;源映射区的起始地址

DMAP2_TAR_1ß0x(80+BANK_No) ;源映射区的起始地址

DMAP2_TAR_2ß0x00 ;源映射区的起始地址

DMAP2_ SRCß0x00 ;目的映射区的起始地址

DMAP2_ CTLß0x2C ;代码长度

设置地址映射器DMAP4,将Internal RAM低4KByte的地址映射至XDATA区的1000~1FFF。映射器DMAP4各寄存器设置如下:

DMAP4_TAR_0ß0x00 ;源映射区的起始地址

DMAP4_TAR_1ß0x01 ;源映射区的起始地址

DMAP4_TAR_2ß0x00 ;源映射区的起始地址

DMAP4_ SRCß0x10 ;目的映射区的起始地址

DMAP4_ CTLß0x2C ;代码长度

完成上述存储器映射后,就可以将FLASM MEMORY的程序按BYTE TO BYTE的方式COPY到INTERNAL SRAM内执行。当然,这些都是在XDATA中处理的。

4.对FLASH的操作

在这个设计中,感兴趣的是FLASH作数据存储区使用,而不是作为程序存储区使用时的操作,所以,下面的描述是针对FLASH作数据存储区使用时的关注事项。

在进行操作前,要事先进行地址映射器的配置,使DPTR能正确指向。

读(READ)--类似于标准的RAM。可在任意时候进行。

写(WRITE)--FLASH片内任一位都只能从1写为0,要从0写为1,必须使用擦除操作。

擦除(ERASE)--擦除操作不能针对特定的字节,最少必须以扇区为单位进行,也可以选择将整个器件内的字节全部擦除。

对FLASH的读、擦除操作,必须按照其Datasheet给定的步骤进行。如:

擦除: xxAAA/AA-xx555/55-xxAAA/80-xxAAA/AA-xx555/55-xxAAA/10(整片擦除); xxAAA/AA-xx555/55-xxAAA/80-xxAAA/AA-xx555/55-ADDR/30(按扇区擦除)

很显然,在我们的应用中,不能使用整片擦除操作,只能按需要将要改写的扇区进行擦除以保存我们的数据。

写:xxAAA/AA-xx555/55-xxAAA/A0-PA/PD

写FLASH时,每个命令序列只能写一个字节。其中PA是所要改写的字节的地址,PD是将要写入的内容。

5.总结

在很多场合,如何将数据保护而不受掉电的影响是很重要的。本文作者创新点:说明了在E5微处理器中如何将FALSH MEMORY用与存取、保护数据,提供了FLASH与SRAM在XDATA空间中映射的方法,希望对使用E5 CPU的研发人员能有所帮助。