20世纪80年代末90年代初,直接序列扩频码分多址(DS/CDMA)开始进入商用,宽带码分多址(BCDMA)的概念也相继提出,对具有大TW(时 间带宽积,越大表明多址能力越强)值的匹配滤波器需求强烈,随着超大规模集成电路(VLSI)和逻辑可编程门阵列(FPGA)的发展使这一需求得以满足。 针对CDMA通信中的快速捕获和各种实际情况折叠滤波、部分相关等多种数字匹配滤波器(DMF)结构相继提出。

1DMF码元捕获的基本原理

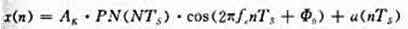

设接收到的中频采样信号为:

其中AK=±1为第k个信息符号;PN(nTS)为码片周期为L的PN序列;该PN序列的码片速率为fpn;TS=1/fs为采样周期;fc为中频信号的 中频频率;Φ0为中频 的初始相位,是均匀分布于[0,2π]的随机变量。a(nTS)是均值为0,方差为δ2 的正态分布的白噪声。设fc已知,则选取本地匹配滤波器为与Φ0无关的复指数型函数 :

其中信息分量:

可以看出m=0 时,|RS(m)|取得最大值,则在无噪声时只要找出|RS(m)|的最大值点即为码元同步的起 点。可见码元捕获方法的依据是PN序列尖锐的自相关特性,在一个信息符号长度内做循环相关,相关值的模的最大位置即为码元起点。

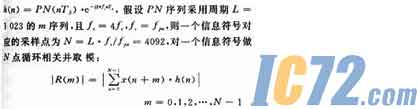

2传统串行匹配滤波器

传统串行数字匹配滤波器有如图2所示的2种等价结构。

本地码aN-1…a0预先存储于FPGA寄存器中,a0是本地码首位(为了节省slice,一般本地码用片内RAM存储),输入抽样数据Xi从左端送入匹 配滤波器 ,经过乘法和加法运算每一个时钟周期都有一个相关值输出。设本地码长L=256,对于图2的第一种结构意味着至少256个抽头,对应256 个乘法单元,加法网络需要至少8级流水线结构,因此采用传统串行结构设计实现匹配滤波器所消耗资源是非常大的。设每个样点采用6b量化,过采样率为4,对 于FPGA器件占用触发器数目可以用下面的公式来计算[1]:占用触发器数=每个样点的量化位数×过 采样率×抽头数目,因此第一种结构需要的触发器数为6×4×256=6 144相当于3 072 个 slice。第二种等价结构虽然减少了加法器网络,但随着每级加法器后面寄存器位宽的增加 硬件规模仍然很庞大。采样时间间隔为1/4TC(TC =1/fC),平均捕获时间T a=( L+L/2)TC =3/2LTC,而一般采用滑动相关的方法平均捕获时间Ta=LTD,其中TD为 滑动相关的相关积分时间,所以传统串行匹配滤波器结构虽然占用的资源大,但实现简单,捕获时间短,随着大规模集成电路的发展,在快速捕获中具有很强的生命力。

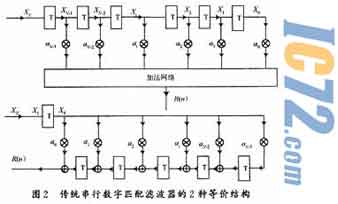

3并行匹配滤波器

文献[2]提及了并行匹配滤波器的结构,如图3所示,将周期为L的本地码分成K段,每段长M=L/K,图3中K=4,M=256,共4路。不难看出,由 于将本地码分成了多组,每路匹配滤波器输出值大于门限时都可以认为捕获成功,所以该种结构的滤波器的平均捕获时间为: 3/2(1/4L)TC =3/8LTC,是传统匹配滤波器的1/K。因此这种并行结构的匹配滤波器具有捕获时间短的优点,但是由于将本地码分成若干段,所以这种结构的滤波器抗干 扰能力有所降低,文献[3]提及的将并行匹配滤波器增加参考支路用于信道估计,有助于提高其抗干扰能力。

4折叠匹配滤波器

折叠滤波器的结构如图4所示。如果滤波器的时钟频率是K倍的采样数据速率 ,对于一个256的本地码序列这种折叠滤波器只需要256/K=64个抽头,这里K=4。每4个时钟周 期送入一个采样数据。在折叠滤波器中码字必须以折叠的形式存放,在第一个时钟周期a0…a 63被送入64个抽头单元中,同时a0加法器中注入一个0,第一个时钟结束时加法器的结构送入保持寄存器。第二个 时钟周期a64…a127被送入64个抽头单元当中,a64加法器的送入来自保持寄存器,第二个时钟周期结束时加法器的结果送入保持寄存器;接下来的两个 时钟周期的情况与此类似,第四个时钟周期 结束时结构送入捕获寄存器。可以看出这种折叠滤波器复用了加法器,在保证平均捕获时间与传统串行匹配滤波器相同的条件下,大大节省了加法器网络所占用的资 源,图4结构所占用的资源=256/4[8(16 b 加减法器)+9(延时单元)+1(本地码存储单元)] +30(控制单元)=1 182 slices,与传统匹配滤波器相比节约了大概2/3的资源。

进一步提高时钟频率可以使资源利用率更低,但是对于硬件设计来说时钟频率的提高使得设计的难度加大,所以在采用折叠滤波器的情况下要综合考虑信息速率,过采样率和硬件所能够支持的时钟频率,使得在硬件所能达到性能条件下,最大限度地降低资源利用率 。

5基于多项分解的匹配滤波器

在FIR滤波器中,转移函数为:

L为滤波器长度,可以将滤波器的冲击响应分成D组,

对接收信号进行M倍过采样[4]时,在本地码相应位置插0,即:

于是可以得到如图5所示的滤波器网络结构图。

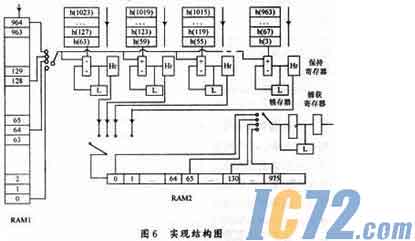

这里M=4,D=16,将本地序列的首位定义为h(1023),末位定义为h(3 ),实现结构如图6所示。在16倍时钟速率下采用循环存储的方法,输入采样数据送入RA M1,16个子滤波器输出送入RAM2,第一个时钟周期读入RAM1中地址0处的数据,h(63)h(3)送入抽 头单元,加法器结果送入琐存单元,同时将保持寄存器1中的结果送入RAM2中的0地址单元。第二个时钟周期读入RAM1中地址为64处的数据,h (127)h(67)送入抽头单元,加法器结果移入锁存器,同时将保持寄存器2中的数据送入RAM2中地址为1的单元。后面14个时钟周期做法类似,在第 16个时钟周期结束的时候,所有锁存器的结果送入保持寄存器,同时清0。RAM2中 的数据以地址为17的间隔输出,送入加法器,每16个数据的和为滤波器的输出。从图6中我们可以看到,滤波器的抽头数目和分组的多少有关,由于加法器分时 复用,所以分组越多,所用的资源越少。同时由于不需要延时单元,所以大大减少了对延时寄存器的占用。资源占用数目比折叠匹配滤波器还少。但是我们也可以看 到,这种结构的滤波器对时钟的要求较高,在设计的时候必须考虑硬件所能支持的最高时钟频率,同时该结构的设计复杂度较大,由于要预先对数据进行存储,捕获 时间相对较长。

以上讨论的是具有通用结构的匹配滤波器,对于特殊的情况还存 在着其他结构比较优秀的滤波器,例如文献[5],[6]根据广义Golay序列的构造方法分别提出了针对WCD MA主同步信道的两种级联数字匹配滤波器,极大地节省了资源提高了运行速度,虽然不是通用的结构但也有较高的实用价值。

6结语

分析了数字匹配滤波器原理的基础上着重分析了多种滤波器的FPGA实现结构,并对每一种结构给出相应的分析结果。随着通信技术的发展,数字匹配滤波器将在今后的实际应用中起着更大的作用,本文在对其结构的设计上具有指导意义。

参考文献

[1]CDMA Matched Filter Implementation in Virtex Devices

[EB/OL ].http://www.Xilinx.com

[2] Milstein L B,Gevargiz J,Das P K. Rapid Acquistion for Direct Sequence Spread Spectrum Communication Using Parallel SAW Convolv ers[J]. IEEE Trans,Com,vol,com33,1985,(7)

[3]胡捍英,邬江兴,蔡斌,等.CDMA通信中匹配滤波器的应用[J].电路与系统学报,1999,(12).

[4]宗孔德.多抽样率信号处理[M].北京:北京清华大学出版社,199 6.

[5]朱春梅,牛凯,吴伟陵.WCDMA主同步信道匹配滤波器的改进与实现

[J]北京邮电大学学报,2002,(9).

[6]牛凯,王双全,吴伟陵.一种新颖的WCDMA主同步信道匹配滤波器

[J ]电子学报,2002,(10).