浅沟槽隔离(STI)填充对晶体管性能的影响极大,是CMOS器件制作中的关键工艺之一。最终目标是在不损伤底层结构的情况下获得无空隙填充的效果。因为随后采用的湿法刻蚀工序可能会产生空隙而导致良率下降,所以获得无空隙填充尤其重要。75nm及以下技术节点对STI填充的要求为缝宽小于75nm、纵宽比(AR)大于8:1。

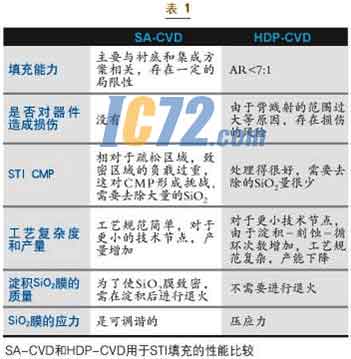

作为应用于STI的高AR填充工艺,SA-CVD和HDP-CVD工艺已被广泛地用在半导体工业中。这两种CVD 技术有一些差别,参见表1。

在SA-CVD工艺中,可调整参数规范使SiO2在单晶硅(c-Si)上有选择地生长,在多晶硅和氮化硅上的生长是受到抑制的。选择式氧化物(SelOx)淀积技术适用于高纵宽比的无隙STI填充。

由于未来技术节点进一步缩小而不断提高STI纵宽比,所以最新HDP-CVD工艺的发展空间越来越小(如图1)。对更小设计规则的热预算的进一步限制也影响着其它STI填充材料充分合拢裂缝所需的退火温度。

实验

研究中采用了来自Applied Materials的通用300mm SA-CVD设备及标准O3/TEOS试剂。在裸硅晶圆上进行的实验是为了表征膜的特性,在结构晶圆上依照一些设计规则进行的实验是为了研究填充效果。集成晶圆上的HDP capping采用标准HDP工艺参数在标准HDP设备上进行。

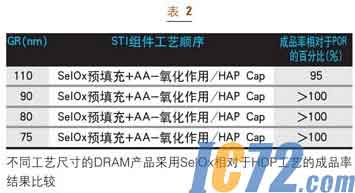

为了获得电性能数据与POR STI方案比较,我们在高成品率DRAM产品上进行了成品率、参数和可靠性测试。该高成品率DRAM产品采用90nm技术,使用HDP-CVD法作为POR STI填充方案。

在这些DRAM器件中,具有存储单元(DT)的致密晶体管阵列区域中的沟槽须进行填充矫正。填充效果采用横截面和自上而下SEM进行直观显示。此外,用器件晶圆的具体成品率参数从电学上来表征填充效果。连续排列成品率(YWL-WL)也间接定量了失效STI组件,其中最常见的失效是多个填充的STI空隙在GC线之间引起的短路。

结果与讨论

A. 裸晶圆上选择式氧化物淀积

氧化层的特性可由工艺参数决定,如容器压强、温度、气体流量、间距和淀积时间。表征氧化层的最重要参数是淀积速率和选择性。

淀积速率由确定衬底上的氧化物生长速率来限定,单位为nm/min。工艺选择性被定义为氧化物在c-Si上生长速率与氧化物在氮化硅上生长速率的比值。

我们研究了工艺参数变化对选择性和淀积速率的影响。工艺选择性是选择氧化物工艺的独特之处。工艺可通过改变工艺压强、臭氧和TEOS的流量比值、间隔(加热器和喷头之间的距离)和晶圆温度进行调谐。

裸晶圆上选择氧化物的膜应力在淀积时约为115Mpa(拉应力)。随后的退火工艺(RTP)使膜收缩了约4%从而使应力变成了压应力。在RTP退火后,选择氧化膜具有相对低的湿法刻蚀速率,即2.0nm/min(DHF 100:1)。

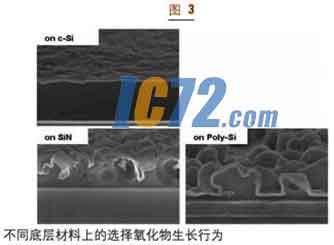

由于淀积的选择性,选择氧化物的生长情况高度地依赖衬底类型。图3表示选择氧化膜在不同衬底(淀积在非结构化晶圆)上的生长图形。拓扑图表明,如果选择氧化物生长在多晶硅、氮化硅和热氧化物表面受到抑制,那么将会从单个点(籽晶,表面缺陷)开始生长,最终形成不规则粗糙表面。

目前还不存在统一的关于选择性生长机理的理论,仅有一些关于此现象的数据资料。在衬底表面上的硅醇群(Si-OH)密度是促成选择性的一个重要因素。人们可采用RTP退火,把CVD-TEOS氧化膜上选择氧化物的生长速率从不具有选择性(高)调谐到具有选择性(低)。晶圆表面上的硅醇群是气相硅种类(乙氧硅醇)的结合位点。图4是关于反应机理的示意图。

B. 结构晶圆上的选择式氧化物淀积

如图5所示, 75nm技术节点用的STI填充工艺分两步进行。在STI刻蚀、掩膜版去除之后,第一步是在c-Si上具有高生长速率的氧化物选择生长工艺,然后在氮化硅及多晶硅上选择生长具有较低生长速率的氧化物。

第二步工艺是常用的HDP cap淀积。HDP厚度与随后的CMP工艺要求有关。

当选择性生长在氧化硅表面不存在时(如图6),AA氧化反应必须在STI填充的第一部分完成之后进行。高温退火对TEOS氧化层的密致作用也是必要的。

图7表示STI短环式晶圆上的选择氧化物填充行为。这些晶圆只有STI结构,而在下面没有DT。对氮化物衬垫的选择性会引起自底而上的填充,所以即使是高纵宽比的沟槽也能被填充。其余的AR采用HDP氧化物填充。

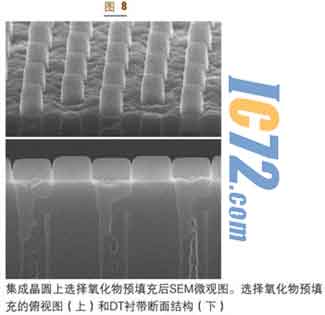

图8表示在全流式晶圆产品上选择氧化物的集成。DT结构中的多晶硅改变了选择氧化物的生长行为。

为表明选择氧化物沉积法的延伸性适用于更小设计规则的STI填充方案,我们对AR高达6:1的STI结构上进行测试,结果论证了选择氧化物沉积法的高AR填充能力。

由于选择氧化物沉积法的填充能力主要受衬底和集成方案的影响,所以我们认为其可延伸到更小设计规则.

C. DRAM器件结果

在采用选择氧化物进行STI填充的晶圆和采用POR工序(用HDP-CVD进行STI填充)的晶圆之间进行性能比较。

成品率及其与STI组件之间的关系类型可分为以下几种:

1.连续排列成品率Y WL-WL:STI填充,

2.基本芯片的功能性Y DC:STI氧化物质量,

3.不可修复性失效后成品率Y B:STI填充工艺与Si/SiO2隔离沟槽内界面之间的相互作用。

一般情况下,所有选择氧化物STI填充方法都表现出较高成品率(如表2)。用接近100%的连续排列成品率可论证无隙填充的效果。选择氧化物法的整体成品率增益可以表示出SA-CVD的优势,并且不会对器件造成等离子体损伤。

结论

SA-CVD基SelOx技术的纵宽比填充能力高、膜质量好、工艺复杂度低,同时产量更高,它能够取代HDP-CVD成为90nm及以下工艺逻辑和DRAM技术的全新STI解决方案。

相对于其它用于90nm及以下工艺的STI填充法,SelOx基集成方案的工艺复杂性和成本都低。这是因为该方案要求一定的预填充工序,其后要求CMP、凹槽刻蚀及HDP Cap工序。

以上的研究已考虑了器件边缘状态,例如热预算低、坡度高(>87°)和由于底层结构(DT和BS),所以要求横向隔离。

所有结果都表明,SA-CVD将成为应用于未来技术节点的一种可行性介质填充方案。