引言

异步串行通信是现代电子系统中最常用的数据信息传输方式之一,一般情况下,为了能够正确地对异步串行数据进行发送和接收,就必须使其接收与发送的码元同步,位同步时钟信号不仅可用来对输入码元进行检测以保证收发同步,而且在对接收的数字码元进行各种处理等过程中,也可以为系统提供一个基准的同步时钟。

本文介绍的位同步时钟的提取方案,原理简单且同步速度较快。整个系统采用VerilogHDL语言编写,并可以在CPLD上实现。

位同步时钟的提取原理

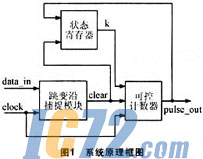

本系统由一个跳变沿捕捉模块、一个状态寄存器和一个可控计数器共三部分组成,整个如图1所示,其中data_in是输入系统的串行信号,clock是频率为串行信号码元速率2N倍的高精度时钟信号,pulse_out是系统产生的与输入串行信号每个码元位同步的脉冲信号,即位同步时钟。

跳变沿捕捉模块的输入也就是整个的输入data_in和clock。当data_in发生跳变时,无论是上升沿或是下降沿,捕捉模块都将捕捉所发生的这次跳变,并产生一个脉冲信号clear,这个clear信号所反应的就是输入信号发生跳变的时刻。然后以它为基准,就可以有效地提取输入串行信号的同步时钟。

状态寄存器有两个输入,分别接跳变沿捕捉模块的输出clear和可控计数器的输出pulse_out,当clear信号的上升沿到来时,此状态寄存器的输出k被置1,之后在pulse_out和k信号本身的控制下,k在pulse_out和k信号上产生一个脉冲之后被置0,这个k为一般连接到可控计数器的控制端。

可控计数器是模可变的计数器,在k信号的控制下可以对clock信号进行模为N-2或2N的计数,其三个输入分别接跳变沿捕捉模块的输出clear、状态寄存器的输出k和时钟clock。其中clear信号可以对计数器进行异步清零,k信号可选择计数的模,当k=1时,计数器的模为N-2,计数满N-2后即产生输出脉冲pulse_out,当k=0时,计数器的模为2N,计数满2N时,产生输出脉冲pulse_out。

整个系统工作时,当输入信号data_in发生跳变时,跳变沿捕捉将可以捕捉到这次跳变,并产生一个脉冲信号clear,此clear信号可以将可控计数器的计数值清零,同时将状态寄存器的输出k置1,并送入可控计数器中,以使计数器进行模块为N-2的计数,待计满后,便可输出脉冲信号pulse_out,此信号一方面可作为整个系统输出的位同步时钟信号,另一方面,它也被接进了状态寄存器,以控制其输出k在计数器完成N-2的计数后就变为0,并在没有clear脉冲信号时使K保持为0,从而使可控计数器的模保持为2N,直到输入信号data_in出现新的跳变沿并产生新的clear脉冲信号,由以上原理可见,在输入信号为连“1”或连“0”的情况下,只要系统使用的时钟信号足够精确,就可以保证在一定时间里输出满足要求的位同步时钟,而在输入信号发生跳变时,系统又会捕捉下这个跳变沿并以此为基准输出位同步时钟。

位同步时钟的提取

本系统包括三个部分,一是采用VerilogHDL语言编写程序,第二步再将每个部分作为一个模块(module)来编写,最后通过元件例化的方法将三个模块连接起来,以完成这个整个系统的设计。

下面是跳变沿捕捉模块的部分程序,其中Int0为串行输入信号,PCclk为输入系统的高精度时钟信号,本模块的输出Pcout对应于图1中的clear信号,它同时又接入状态寄存器模块的Psclr和可控计数器模块的clr。其仿真结构如图2所示。

跳变沿捕捉模块的部分程序如下:

module PcheckCapture (PCout,Int0,PCclk);

……

reg PCtemp1,PCtemp2;

always@(posedge PCclk) begin

PCtemp1<=Int0;

PCtemp2<=PCtemp1;

end

assign PCout="PCtemp1"^PCtemp2;

……

状态寄存器模块的部分程序如下,其中输入信号Psclr来自跳变沿捕捉模块,另一个输入信号Pss则来自可控计数器的输出s对应图1中的pulse_out,输出信号Psout对应图1中的k;

module PcheckSreg (Psout,Pss,Psclr);

……

wire Pstemp;

assign Pstemp=~(Pss&Psout);

always@(posedge Pstemp or posedge Psclr) begin

if(Psclr==1b1)Psout<=1;

else Psout<=~Psout;

end

……

下面是可控计数器模块的部分程序,其中三个输入信号k、clr、clk分别对应于图1中的k、clear、clock,输出信号s对应于图1中的输出信号pulse_out;

module PcheckCoumter (s,k,clr,clk);

……

always@(posedge clk or posedge clr)

begin

if(clr==1)begin

s=0;

cnt=0;

end

else begin

if(k==0) begin

if(cnt==2N-1)begin

cnt=0;

s=1;

end;

else begin

cnt=cnt+1;

s=0;

end

end

else begin

if(cnt==N-2)begin cnt="0";

s=1;

end

else begin

cnt=cnt+1;

s=0;

end

………

在顶层模块中,应对三个模块进行例化,并在导线相连接,以构成一个完整的系统,此模块的程序如下:

modulePcheckTop (PTout,PTint,PTclk);

inout PTout;

input PTint,PTclk;

PcheckCapture a (clear,PTint,PTclk);

PcheckCounter b (PTout,k,clear,PTclk);

PcheckSreg

c(k,PTout,clear);

endmodule

图3为整个系统的仿真结果。

结束语

本位同步时钟提取方案已在CPLD器件上进行了仿真实现,通过以上的分析可知,本位同步时钟的提取方案具有结构简单、节省硬件资源、同步建立时间短等优点,在输入信号有一次跳变后,系统出现连“1”连“0”,或信号中断时,此系统仍然能够输出位同步时钟脉冲,此后,只要输入信号恢复并产生新的跳变沿,系统仍可以调整此位同步时钟脉冲输出而重新同步,此系统中输入的时钟信号频率相对码元速率越高,同步时钟的位置就越精确,而当输入码元速率改变时,只要改变本系统中的N值系统就可重新正常工作。