摘 要:在工控现场及各种仪表中往往需要实时记录一些数据,本文介绍采用Xicor公司X24C45实现设备掉电时的数据自动存储的方法,并给出了应用实例。

关键词:X24C45; 掉电; 数据自动存储

在工控现场及电度表、流量计等仪表中往往有一些数据需要被不断地实时刷新存储(常常每天可达数万次),并且在设备掉电或重新启动时这些数据也需被保持。在这种情况下,使用静态RAM虽然可以无限次记录数据,但为了保持数据,RAM必须加有电池;如果使用E2PROM或Flash ROM,则记录次数有限(大多在百万次左右)。同时为了掉电时能自动存储数据,系统必须具有掉电检测电路,这样系统将变得复杂且成本增加。

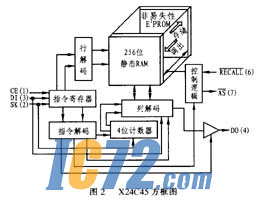

Xicor公司的X24C45串行256位NOVRAM则可以很好的满足以上要求。X24C45是按16×16组织的静态RAM,与非易失性E2PROM阵列位对位(bit-by-bit)重叠,可以利用软件命令或外部输入端在两个存储器阵列之间传送数据。存储操作(RAM数据至E2PROM)最长需5ms完成;调出操作(E2PROM数据至RAM)最长需5μs完成。X24C45可以不受限制的把数据从主机写至RAM或从E2PROM调至RAM,最小存储操作次数为100万次,数据保存期大于100年。X24C45还具有用户可选的AUTOSTORE(自动存储)特性,即当VCC下降到预置的门限(4.0~4.3V)以下时能自动完成存储操作;同时它能上电自动执行调出操作。X24C45与串行端口兼容(COPSTM,8051),可很方便地和各种微控制器接口。

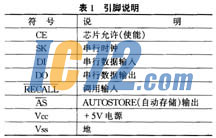

1. 引脚功能

X24C45的引脚排列如图1所示,各引脚说明如表1所列,具体的功能如下。

芯片允许(CE):CE为高电平时方可允许读写操作。在读或写命令后,CE必须保持高电平,直到数据传送完为止。CE为低电平将使X24C45处于低功耗的待机方式并复位指令寄存器。因此,在准备下一操作命令时,为了使指令寄存器复位,每一次操作完成之后必须把CE拉至低电平。

串行时钟(SK):SK用于所有数据能在时钟同步下输入或输出的器件。

数据输入(DI):DI是串行数据输入端。

数据输出(DO):DO是串行数据输出端。除了在响应READ指令数据输出周期之外,均为高阻状态。

AUTOSTORE(自动存储)输出(AS):AS是漏极开路输出端,当它为低电平有效时表示VCC已下降到AUTOSTORE(自动存储)门限(VASTH)之下。AS可以和多个漏极开路输出端“线或”(wire-ORed)连接,并可用作微控制器的中断输或低功率复位电路的输入。

RECALL:RECALL为低电平时,启动从E2PROM至RAM阵列的内部数据传送

2. 工作原理

X24C45包含一个8位的指令寄存器,它通过DI输入端来访问,数据在SK的上升沿由时钟同步输入。在整个数据传送操作期间,CE必须保持高电平。

表2列出了X24C45的所有指令及操作码。所有指令的最高有效位(MSB)是逻辑1(高电平),位6至3是RAM地址(A)或不关心(X),而位2至0是操作码。X24C45要求按最高位(MSB)在前的方式送入指令。在CE为高电平之后直到逻辑“1”送入DI为止,X24C45将不会解释数据流。因此,可以在SK工作(running)且DI为低电平的情况下把CE拉至高电平;但在X24C45开始任何动作之前,DI必须为高电平以表示指令的起始条件。

此外,SK时钟是完全静态的(totally static)。用户如完全停止时钟,数据移动也将被停止,重新启动时钟将恢复数据的移动。

现将X24C45的指令操作码及功能分述如下:

●RCL和RECALL

软件RCL指令或RECALL输入端的低电平可以启动数据从E2PROM传送到RAM。这种软件或硬件的调用操作可设置内部“先前调用(previous recall)”锁存器。该锁存器上电时被复位,为了允许任何写或存储操作,它必须由用户加以设置。虽然上电前完成了调用操作,但是此操作并不设置“先前调用”锁存器。

●WRDS和WREN

X24C45内部包含“写允许”(write enabled)锁存器。写入RAM或对E2PROM进行存储操作时必须设置该锁存器。可用WREN指令设置锁存器,WRDS指令复位锁存器,从而有效的保护非易失性数据,使之免受破坏。上电时“写允许”锁存器自动复位。

●STO

STO指令将启动数据从RAM至E2PROM的传递。要避免不想要的存储操作,下列条件必须为真:

(1) 发生STO指令

(2)内部“写允许”锁存器必须被设置(WREN指令已发出)

(3)“先前调用”锁存器必须被设置(软件或硬件调用操作)

一旦存储周期开始,器件的所有其它功能将被禁止,存储周期完成之后,写允许锁存器被复位。

●WRITE(写)

WRITE(写)指令包含要写的字的4位地址和写指令之后要写的16位字,移入的数据将写至RAM。在整个操作期间,CE必须保持高电平。在写结束后到SK下一个上升沿之前,CE必须变为低电平。但如果CE过早的变为低电平(在指令之后但16位数据被传送之前),那么指令寄存器将被复位。如果CE保持高电平的时间大于24个SK时钟周期(8位指令加16位数据),那么已移入的数据将被重写。

●READ(读)

READ(读)指令包含要访问的字的4位地址。与其它的6个指令不同,该指令字的I0是“不关心”。这样有两个优点,首先,在把DI和DO二者连接在一起的设计中,指令中不存在第8位,这将允许主机有时间把I/O线从输出转为输入;其次,在第9个SK时钟周期内,它可供有效数据输出使用。

读操作期间的首位输出DO被截断。即它在内部由第8个SK时钟的下降沿同步;然后,所有的后续位由SK的上升沿同步。

●低功耗方式

当CE为低电平时,非关键的内部器件被断电,使器件处于待机状态,因而功耗最小。

●AUTOSTORE(自动存储)特性

AUTOSTORE(自动存储)指令(ENAS)用来设置“AUTOSTORE允许”锁存器,X24C45在VCC下降到AUTOSTORE(自动存储)门限(VASTH)以下时自动执行存储操作。执行该指令前必须先执行WREN指令。

●写保护

X24C45提供了两种软件写保护机制以防止未知数据的误存储,首先,上电时“写允许”和“AUTOSTORE”(自动存储)允许锁存器处于复位状态,禁止任何存储操作;其次,在上电后“先前调用(previous recall)”锁存器被设置后可进行数据存储,它仅通过运行软件或硬件调用操作来设置,以确保所有的RAM单元内的数据有效。

●系统的考虑

X24C45执行上电调用时,可把E2PROM的内容传送到RAM阵列。虽然可以从RAM阵列读出数据,但是这种调用并不设置“先前调用”锁存器。因为在这种上电调用操作期间所有的命令被忽略,因此,在VCC稳定之后,主机还应当把X24C45的任何操作最少延迟tPUR(最大为200μs)的时间。

3. 应用实例

在我们开发的智能流量积算仪中,需要每秒记录一次累积流量,并且该累积流量在设备停用或掉电时要被保存,以便重新运行时继续对累积流量进行累积。在该积算仪中采用了一片X24C45来存储累积流量,很好的满足了系统的要求。X24C45与系统中的8051微处理器的接口如图3所示。DO和DI口被接到微处理器的同一个I/O口P1.7上,从而节省一个I/O口。

微处理器以字节为单位,读写X24C45的程序如下:

SK BIT P1.5 ;SK接在P1.5口

CE BIT P1.6 ;CE接在P1.6口

DIO BIT P1.7 ;DI与DO接在P1.7口

WRDS EQU 80H ;各个指令字

STO EQU 81H

ENAS EQU 82H

WRITE EQU 83H

WREN EQU 84H

RCL EQU 85H

READ EQU 86H

DATAHI EQU R0 ;数据的高位寄存器

DATALO EQU R1 ;数据的低位寄存器

ADDR EQU R2 ;地址寄存器

COUNT EQU R3 ;计数器

INST EQU R4 ;命令寄存器

ORG 0000H ;程序复位地址

LJMP BEGIN

ORG 0100H ;程序起始地址

BEGIN MOV SP,#60H ;初始化堆栈指针

CLR CE ;复位控制信号

CLR SK

CLR DIO

MOV A,#RCL ;进行一次调出操作以便设置“先前调用”锁存器

MOV INST,A

SETB CE

LCALL OUTBYT

CLR CE

MOV A,#WREN ;设置“写允许”锁存器

MOV INST,A

SETB CE

LCALL OUTBYT

CLR CE

MOV A,#05H ;读地址5中的内容,并保在寄存器DATALO与DATAHI中

MOV ADDR,A

LCALL RDWRD

MOV A,#09H ;将前面地址5中读出的内容写入地址9中

MOV ADDR,A

LCALL WDWRD

MOV A,#STO ;进行一次存储操作

MOV INST,A

SETB CE

LCALL OUTBYT

CLR CE

DONE: LJMP DONE ;循环直到复位

;将寄存器DATALO与DATAHI中的内容写入X24C45,地址由寄存器ADDR指定。

WRWRD SET CE ;将寄存器DATALO与DATAHI中的内容写入寄存器ADDR指定的地址中

MOV A,ADDR

RL A ;将地址加入指令中

RL A

RL A

ORL A,#WRITE

MOV INST,A

LCALL OUTBYT ;输出写指令

MOV A,DATAHI

MOV INST,A

LCALL OUTBYT ;输出数据的高字节

MOV A,DATALO

MOV INST,A

LCALL OUTBYT ;输出数据的高字节

CLR CE

RET

;读由寄存器ADDR指定的地址中的内容,并存入寄存器DATALO与DATAHI中。

RDWRD: SET CE ;读寄存器ADDR指定的地址中内容

MOV A,ADDR

RL A ;将地址编入指令中

RL A

RL A

ORL A,#READ

MOV INST,A

LCALL SEND7 ;送出7位指令字

SETB DIO

LCALL CLOCK ;设置时钟为读数据作准备

MOV COUNT,#10H;读进16位数据

BIXT: MOV C,DIO

NO1: MOV A,DATALO ;将数据移进寄存器DATALO与DATAHI中RLC A

MOV DATALO,A

MOV A,DATAHI

RLC A

MOV DATAHI,A

LCALL CLOCK ;发出时钟脉冲

DJNZ COUNT,BITX;读数据循环

CLR CE

RET

;将寄存器INST中的内容传送到X24C45的输入口。

SEND 7 MOV COUNT,#07H;移出7位读命令字

SJMP LOOP0

OUTBYT: MOV COUNT,#08H;移出8位命令字

LOOP0: MOV A,INST ;为将数据输出到DI作准备

RCL A

MOV INST,A

MOV DIO,C

LCALL CLOCK ;发出时钟脉冲

DJNZ COUNT,LOOP0;循环

RET

;产生时钟脉冲

CLOCK: SET SK

CLR SK

END